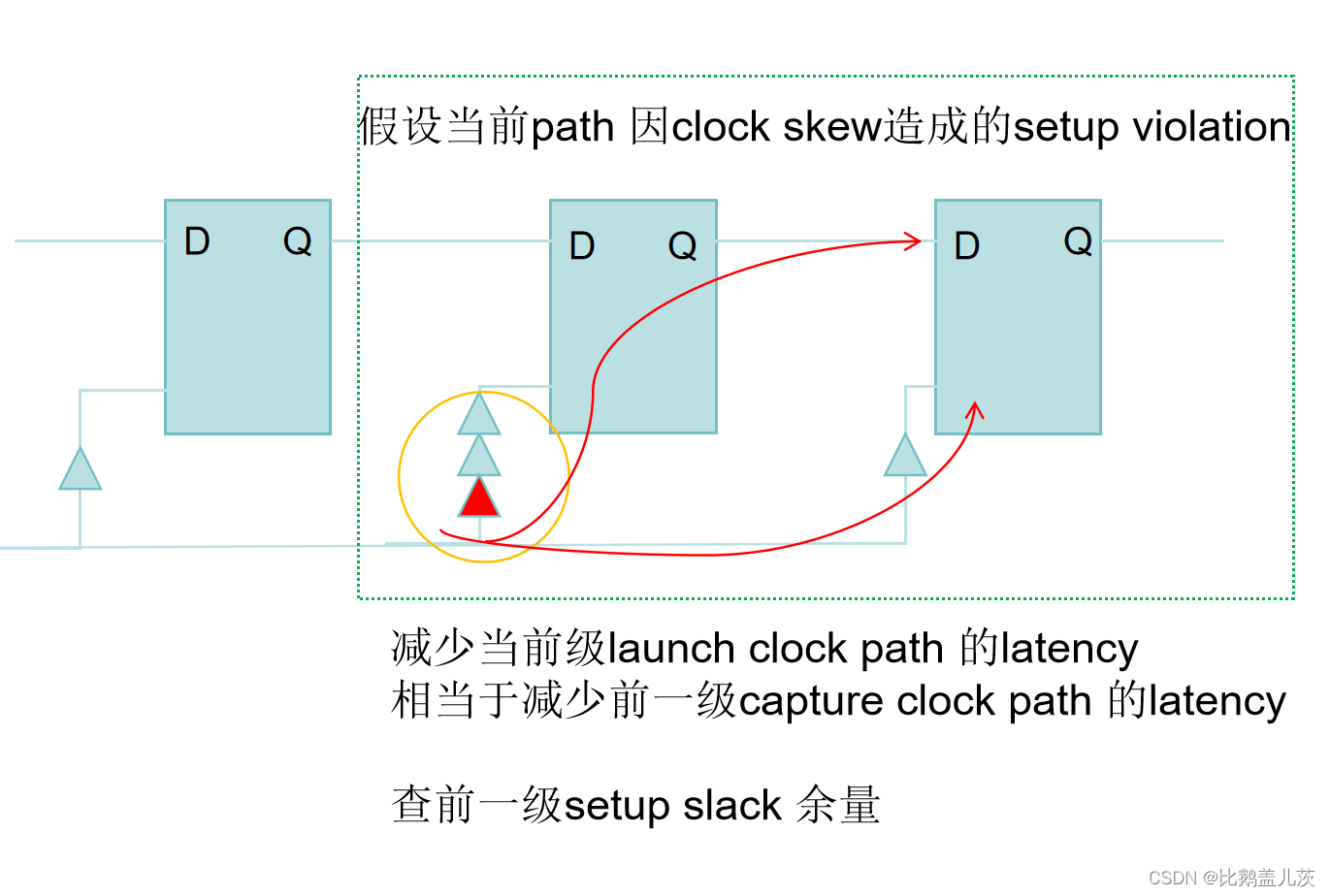

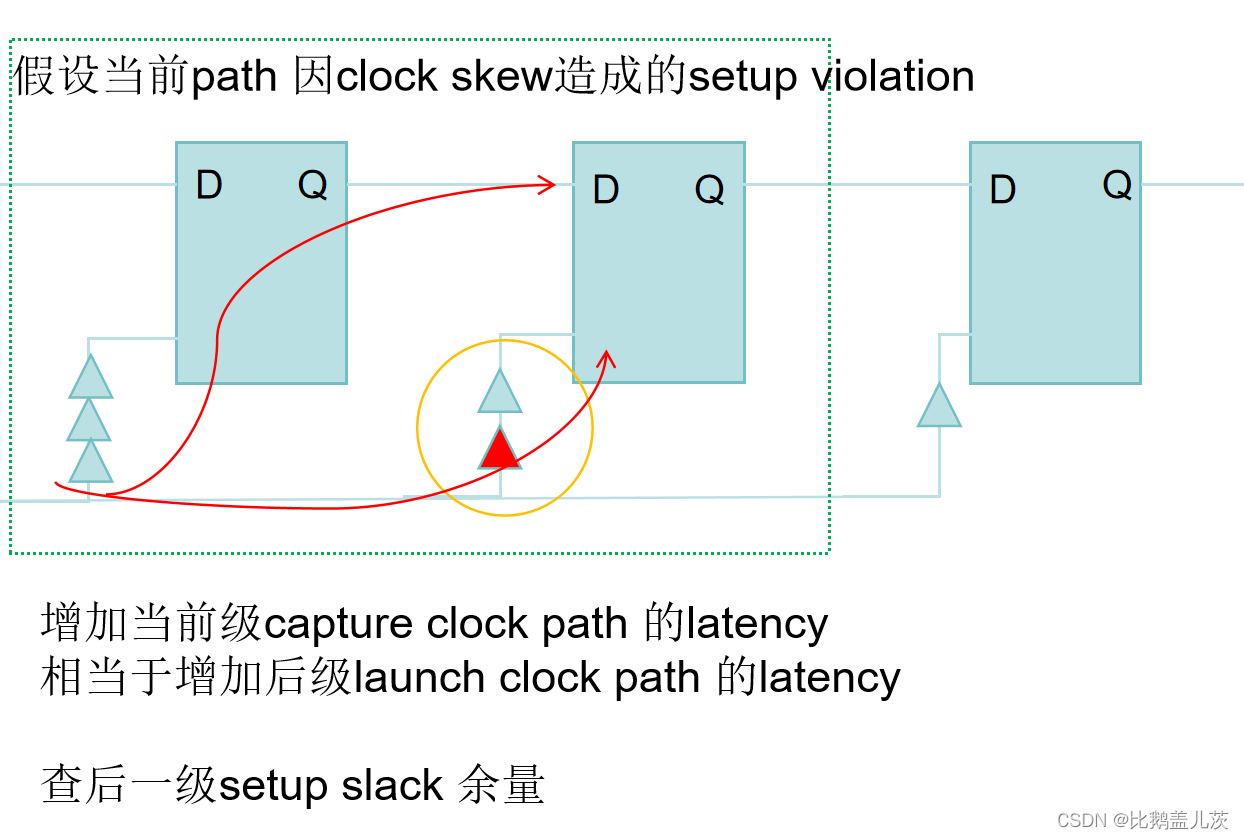

1.请例出修复由clock skew 造成的f2f setup violation时需要检查什么,并描述你怎么实现skew。

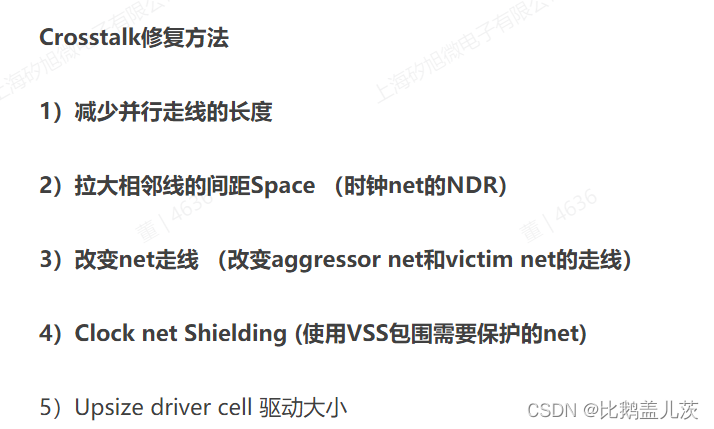

2.例举修复crosstalk 所有方法

3.给你一个10层金属的设计,描述你将设计的典型的电源网络。

如果是block level设计,10层金属留给顶层打power,8-9层为power stripe,一层为power rail为st cell 供电。底层金属由顶层金属通过层层打孔进行电源供给。若是先进工艺power stripe 可以通过打孔直接连接macro内部PG pin为其供电,若非先进工艺,也可以在macro四周设置power ring 为其供电。

4.

5.请描述你如何初始化和建立一个还没有做floorplan的block。请说明如何量化和验证你的工作。

1.导入文件:网表,lib,Techlef,lef,mmmc,qrc,sdc等

2.读入det文件初始化block的尺寸(如果顶层没给可以需要自己根据要求定义)

3.建立row和track (如果需要的话)

4.摆放macro:根据准则和要求摆放并调整布局,比如出pin方向,macro之间的位置,channel,预留的st cell 摆放区为正方形等。如果需要微调macro,让macro pin在相应track上

6.建立 voltage areas

7. place ports:

8.建立 keepout margin around hard macros

9.create placement blockages :macro 的channel里

10.插入boundary cell 和 tap cell

11.电源规划:定义逻辑连接,建立via规则,创建power stripe, power rail等步骤

量化和验证

导入文件之后需要check netlist,检查时钟周期是否符合SPEC;检查log中是否有ERROR;

lib缺失,constraint定义问题等

floorplan 之后:总的来说就是,各个模块cell的分布符合data flow, congestion map 和cell density适度, drc相对clean。

检查memory摆放的方向是否正确(poly方向需要和标准单元,memory的poly方向一致)

检查powerplan是否存在pg floating:

verifyConnectivity -noAntenna -noSoftPGConnect -noUnroutedNet -error 1000000 -net VDD

verifyConnectivity -noAntenna -noSoftPGConnect -noUnroutedNet -error 1000000 -net VSS

检查powerplan是否存在short和open:verify_PG_short -no_routing_blkg

检查floorplan&powerplan是否有drc violation:verify_drc -limit 10000

最好的办法就是先简单处理后在calibre里跑一遍,检查drc;

根据目前的drc进行floorplan阶段的迭代优化,可能到place_opt由于时序问题仍要返回优化迭代。

2814

2814

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?