今天分享咱们社区某位学员提问的20个时钟树综合相关问题。大家也可以借此机会再复盘下这些复杂时钟结构设计的时钟树综合做法。

数字IC后端培训教程之数字IC后端设计实现必须搞懂的5个问题

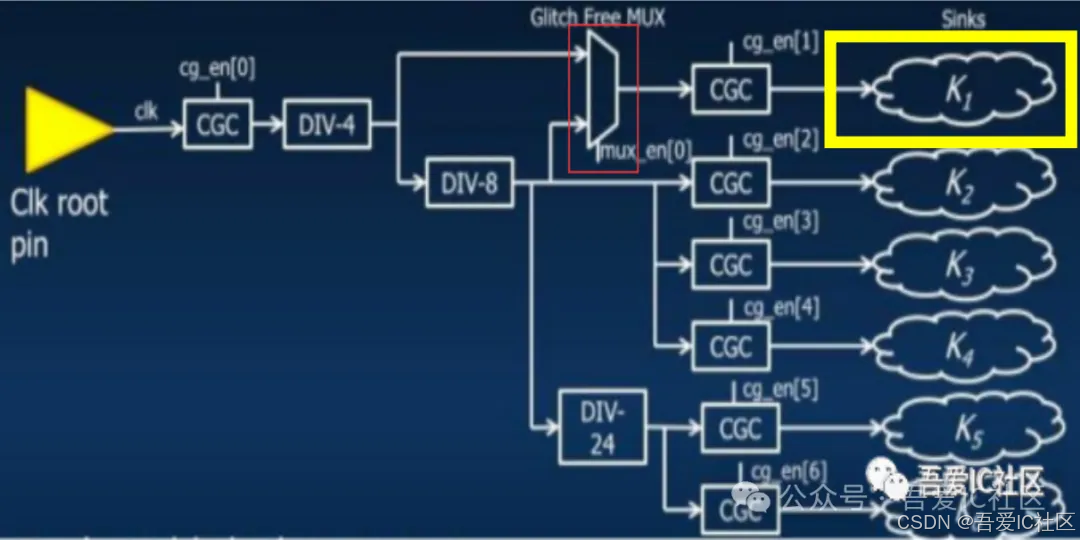

Q1:MUX的两个input pin为什么要设置成floating pin 是为了让A 和B不用做blance吗?为什么不直接把 A B设置成ignore pin 再在output pin那边create clock或者create generate clock呢,是不是遇到所有的MUX都要这样设置才是最优解 ,此外漏tree的意思是从 mux_out出来的CGC和K1那一块的CK PIN都不会连接到clk root上 ,就是把clock 当data长最后它们的ck pin会连接哪里?

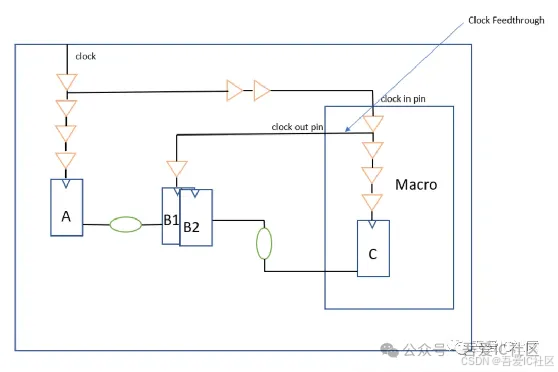

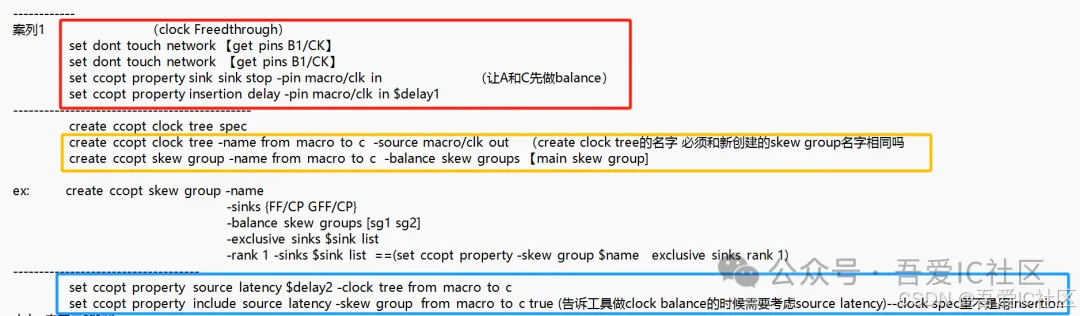

Q2: 假如在一个clock spec里面 create ccopt clock tree 两次,且source的clock root都不是同一个,最后怎么才能把两个不同clock root的tree长到一起(如图所示先让A和C做balance ,再长一颗从clk_Out为root的tree,如何让这两颗clock tree最后长到一起)

</

</

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3916

3916

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?