目录

大家好,这里是程序员杰克。一名平平无奇的嵌入式软件工程师。

上一篇主要是对Xilinx 官方对AXI协议的一些内容描述进行了介绍,本篇开始,AXI4的三种总线的时序以及相关特性进行总结分享。本篇结合Xilinx提供的模板对AXI4_Lite总线进行总结。

下面正式进入本章推送的内容。

01 AXI4_Lite介绍

AXI4_Lite总线协议是轻量化的AXI4总线,最关键的特性如下:

- 不支持突发传输(burst length为1)

- 仅支持32bit/64bit的数据位宽传输

- 所有的访问都是不可修改、不可缓存

- 不支持独占访问

- 适用于寄存器简单的访问场合

AXI_Lite接口信号

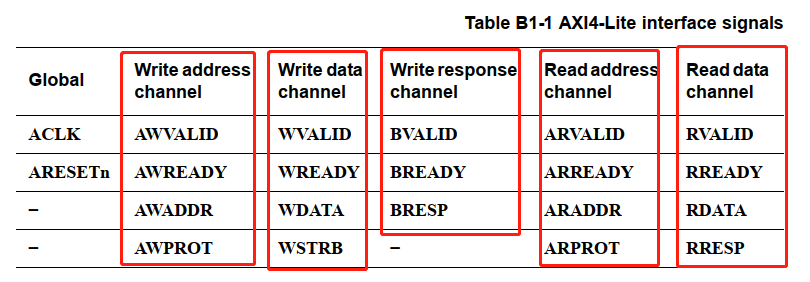

AXI4-Lite总线有5个独立的通道:读地址通道、写地址通道、读数据通道、写数据通道、写响应通道;各通道的接口信号如下图所示:

特别说明:

对于5个通道而言,每个通道的信号是独立的。即是写地址、写数据、读数据等通道时可以同时进行的。一定要理解"独立"这个词,对于后续理解/编写时序特别重要。

02 AXI4_Lite读写事务接口说明

对于AXI4、AXI4-Lite而言,关键是地址和数据。对于地址和数据有效而言,取决于各通道的握手机制(xVALID、xREADY),以此为依据对时序进行分析。

写事务(Write transaction)

对于Xilinx官方提供AXI4_Lite总线模板,一次写传输事务逻辑如下:

- Master将AWVALID、WVALID、BREADY置有效,等待握手和响应

- Slave检测到AWVALID、WVALID信号同时有效时获取AWADDR,在下一个时钟上升沿将AWREADY、WREADY置有效,同时数据开始传输

- Slave返回BRESP响应信息以及BVALID置有效

以下按照AXI4-Lite_master、AXI4-Lite_slave的顺序对AXI_Lite的逻辑实现进行说明,写事务逻辑仿真如下图:

-

AXI4-Lite_master写事务逻辑信号

AXI4-Lite_master控制的信号如下表:

| 信号 | 所属通道 | 说明 |

| AWVALID | 写地址通道 | 地址有效信号 |

| AWADDR | 写地址 | |

| AWPROT | 写保护类型,表示一次传输的特权、安全等级 | |

| WVALID | 写数据通道 | 写有效信号 |

| WDATA | 写数据(32bit/64bit) | |

| WSTRB | WDATA字节有效信号 | |

| BREADY | 写响应通道 | Ready信号,表明主机可以接收写响应信号 |

-

AXI4-Lite_slave写事务逻辑信号

AXI4-Lite_slave控制的信号如下表:

| 信号 | 所属通道 | 说明 |

| AWREADY | 写地址通道 | 地址有效信号 |

| WREADY | 写数据通道 | 写有效信号 |

| BVALID | 写响应通道 | Ready信号,表明主机可以接收写响应信号 |

| BRESP | 写响应,表明写传输的状态 |

读事务(Read transaction)

对于Xilinx官方提供AXI4_Lite总线模板,读事务逻辑仿真如下图:

-

AXI4-Lite_master读事务逻辑信号

AXI4-Lite_master控制的信号如下表:

| 信号 | 所属通道 | 说明 |

| ARVALID | 读地址通道 | 地址有效信号 |

| ARADDR | 读地址 | |

| ARPROT | 保护类型,表示一次传输的特权、安全等级 | |

| RREADY | 读数据通道 | 读READY信号,表明主机可以接收从机返回的数据 |

-

AXI4-Lite_slave读事务逻辑信号

AXI4-Lite_slave控制的信号如下表:

| ARREADY | 读地址通道 | 可读信号 |

| RVALID | 读地址通道 | 读有效信号 |

| RDATA | 读数据通道 | 读数据(32bit/64bit) |

| RRESP | 读响应,表明读传输的状态 |

03 文章总结

鉴于公众号文章篇幅不宜过长,本文仅是对AXI_Lite的特性以及读写事务的接口进行说明,AXI_lite模板(master/slave)代码的分析便只能在下一篇推送进行分享。

参考文档:

《ug761_axi_reference_guide.pdf》

《UG1037-Vivado-AXI Reference Guide.pdf》

《IHI0022E_amba_axi_and_ace_protocol_spec.pdf》

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?