写在前面

AXI4-Lite总线可以说是AXI4-Full总线的简化版,仅支持突发长度为1的事务传输。在学习AXI4-Lite总线时,建议先了解AXI4-Full总线,本文也注重介绍两者的差异。

AXI 表示 Advanced eXtensible Interface(高级可扩展接口),它是由 Arm 定义的接口协议,包含在“高级微控制器总线架构 AMBA”标准中。

AXI4 接口 (AMBA 4.0) 分 3 种类型:

- AXI4 (AXI4-Full):用于满足高性能存储器映射需求。

- AXI4-Lite:用于简单的低吞吐量存储器映射通信(例如,往来于状态寄存器的通信)。

- AXI4-Stream:用于高速流传输数据。

AXI4-Lite总线协议的特性如下:

- 事务传输突发长度为1

- 每次传输只能传输一个数据

- 所有访问都是不可修改(Non-modifiable),不可缓冲(Non-bufferable)

- 不支持专属访问(Exclusive access)

AXI4-Lite比起AXI4-Full总线来说,由于每次只传输一个收据,传输效率低了很多。比较适用的场景是单次访问某个寄存器(地址寻址),类似于IIC总线的单次读写。在SOC系统或者ZYNQ中比较常用。

2、通道(Channel)

AXI4-Lite定义了 5 条通道:

其中 2 条用于读取传输事务(transaction):

- 读地址(AR) read address

- 读数据 (R) read data

另 3 条用于写入传输事务(transaction):

- 写地址(AW) write address

- 写数据(W) write data

- 写响应(R) write response

2.1、AXI 读取传输事务

AXI 读传输事务需要在 2 条读取信道上发生多次传输:读地址通道 (Read Address Channel)、读数据通道 (Read data channel) 。

- 首先,读地址通道 (Read Address Channel) 从主设备 (Master) 发送到从设备 (Slave),以便设置地址和部分控制信号。

- 然后,此地址的数据通过读数据通道 (Read data channel) 从从设备发送到主设备。

请注意,根据下图所示,每个地址中可发生多次数据传输。此类型的传输事务称为突发 (burst)。需要注意的是AXI4-Full是支持突发的,而AXI4-Lite是不支持突发的,或者说“突发长度为1”。

2.2、AXI 写入传输事务

AXI 写入传输事务需要在 3 条读取信道上存在多次传输。

- 首先,写地址通道 (Write Address Channel) 从主设备发送到从设备,以便设置地址和部分控制信号。

- 然后,此地址的数据通过写数据通道 (Write data channel) 从主设备发射到从设备。

- 最后,写入响应通过写响应通道 (Write Response Channel) 从从设备发送到主设备,以指示传输是否成功

看到这里可能会发现读、写事务所需的通道数不相同,写事务需要3条通道,而读事务只需要2条通道,较之少了一条“读响应通道”,难道读事务不需要响应吗?读事务当然也需要响应,只不过既然已经存在一条读数据通道,刚刚好这条通道就是用来传输数据的,那么自然也可以用来传输数据作为读取响应。读事务的响应值规则与写事务的响应值规则一致。

2.3、通道定义(channel definition)

首先,5个通道都具有的同一类信号:VALID、READY。这两个信号用来实现AXI协议的握手机制(handshake)。在共同的定义之外,各个通道有自己的定义。

读、写地址通道(Read and write address channels)

读、写事务分别具有各自的独立通道,写入本次事务所需的地址和控制信息。

读数据通道(Read data channel)

读数据通道上包括从机发送给主机的读数据,以及从机对于本次读传输操作的回复。总线数据位宽可以是 32或者是64bit。

写数据通道(Write data channel)

写数据通道上包括主机发送给从机的写数据。总线数据位宽可以是 32或者是64bit。写数据通道还具有STROBE 信号,该信号以数据的字节为单位进行选取,可实现数据的掩码功能。

写响应通道(Write response channel)

写响应通道用于从机将写操作响应回复给主机。所有写传输操作都需要以写回复通道上接收写响应作为完成信号。

3、信号

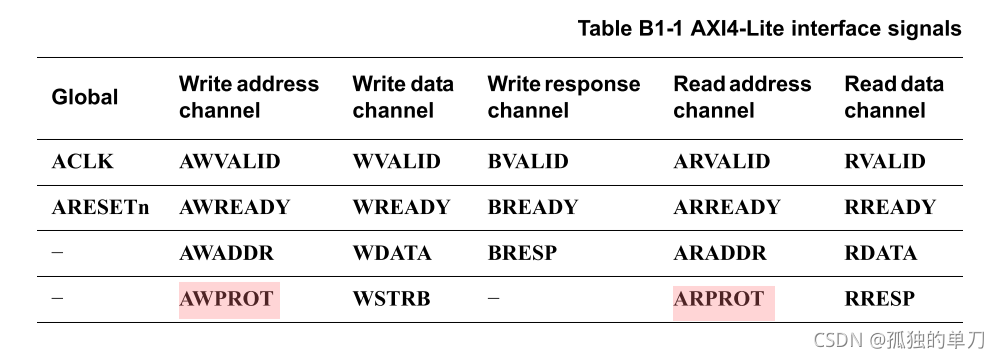

由于突发长度为1,所以在AXI-Full总线的基础上删除了很多 ,如下所示(红色部分是很少用到信号,我这里不讲,有兴趣自己看ARM的手册)

3.1、全局信号(Global signals)

- ACLK:全局时钟信号,所有的传输操作都发生在 ACLK 的上升沿

- ARESETn:低电平有效的同步复位信号

3.2、写地址通道信号(Write address channel signals)

该通道的信号均用AW作为前缀(address write):

- AWADDR:写地址,给出一次写突发传输的写地址。主机到从机;

- AWVALID:有效信号,表明此通道的地址控制信号有效。主机到从机;

- AWREADY:表明"从"可以接收地址和对应的控制信号。从机到主机。

3.3、写数据通道信号(Write data channel signals)

该通道的信号均用W作为前缀(write):

- WDATA :写地址,给出一次写突发传输的写地址。主机到从机;

- WSTRB :WSTRB[n:0]对应于对应的写字节,WSTRB[n]对应WDATA[8n+7:8n]。WVALID为低时,WSTRB可以为任意值,WVALID为高时,WSTRB为高的字节线必须指示有效的数据。主机到从机;

- WVALID :写有效,表明此次写有效。主机到从机;

- WREADY :表明从机可以接收写数据。从机到主机。

3.4、写响应通道信号(Write response channel signals)

该通道的信号均用B作为前缀(我也不知道B是什么意思,知道的可以告诉我):

- BRESP :写响应,表明写传输的状态。从机到主机;

- BVALID :写响应有效。从机到主机;

- BREADY :表明主机能够接收写响应。主机到从机。

3.5、读地址通道信号(Read address channel signals)

该通道的信号均用AR作为前缀(address read):

- ARADDR:读地址,给出一次读突发传输的读地址。主机到从机;

- ARVALID:有效信号,表明此通道的地址控制信号有效。主机到从机;

- ARREADY:表明"从"可以接收地址和对应的控制信号。从机到主机。

3.6、读数据通道信号(Read data channel signals)

该通道的信号均用R作为前缀(read):

- RDATA:读到的数据。从机到主机;

- RRESP :读响应,表明读传输的状态。从机到主机;

- RVALID:读有效信号。从机到主机;

- RREADY:表明"主机"可以接收从机发送的数据。主机到从机。

4、握手机制(handshake)

AXI-Lite 总线共有 5 个独立的通道,分别为写地址、写数据、写回应、读地址、读数据通道。5 条通道相互独立,有一些细小的差别,但共同使用一套握手机制:VALID/READY 机制,来实现信息的传递。

在握手机制中,通信双方分别扮演发送方(Source)和接收方(Destination),两者的操作(技能)并不相同。

-

发送方置高 VALID 信号表示发送方已经将数据,地址或者控制信息已经就绪,并保持于消息总线上

-

接收方置高 READY 信号表示接收方已经做好接收的准备

当双方的 VALID/READY 信号同时为高,在时钟 ACLK 上升沿,完成一次数据传输。所有数据传输完毕后,双方同时置低自己的信号。所谓的双向流控机制,指的是发送方通过置起 VALID 信号控制发送的时机与速度,接收方也可以通过 READY 信号的置起与否控制接收速度。发送方拥有传输的主动权,但接收方在不具备接收能力时,也能够置低信号停止传输,反压发送方。

三种握手情况

VALID/READY 信号按照到达的先后顺序可以分为 3 种情况:

情况1:VALID信号先到达,READY信号后到达(主机先于从机做好了发送数据的准备)

主机先拉高TVALID信号--表明当前主机可以传送数据给从机,而TVALID一旦被拉高,则只能在从机进行响应传输了数据后才能拉低。从机在接收到主机发送的准备好的信号后,会对自身的情况做判断,判断自己是否具备了接收数据的准备,这也给了从机对数据流进行反压的能力,保证从机的接收处理能力不会瘫痪。一旦从机可以接收数据,便拉高TREADY信号,表明自己可以接收数据。此时TVALID && TREADY为高,在时钟的上升沿进行数据传输。

不妨举个接地气的例子(写的不好,有点俗套):

快递小哥(主机MASTER)拿了一个快递,准备全部送去小区的菜鸟驿站入库,与驿站值班小妹(从机SLAVE)对话如下:

小哥:老妹,我这来了一个快递,赶紧让我入库(主机可以发送数据,拉高TVALID)

小妹:你先别急,我这货架还没空出来呢!先让我整理整理(从机没有做好接收数据的准备)

小妹: 好了,大兄弟,你赶紧入库吧(从机可以接收数据,拉高TREADY)

情况2:READY信号先到达,VALID 信号后到达(主机后于从机做好了发送数据的准备)

从机拉高TREADY信号,表明自己可以接收数据。主机会对自身的情况做判断,判断自己是否具备了发送数据的准备,一旦主机可以发送数据便拉高TVALID信号,此时TVALID && TREADY为高,在时钟的上升沿进行数据传输。

(依旧是俗套的例子)快递小哥(主机MASTER)拿了一个快递,准备全部送去小区的菜鸟驿站入库,与驿站值班小妹(从机SLAVE)对话如下:

小妹:大兄弟,你赶紧入库吧,我都等你半天了,不然早回家了(从机可以接收数据,拉高TREADY)

小哥:老妹,我这车快没电了,跑不快,再给我两分钟(主机没有做好发送数据的准备)

小哥:老妹,我终于来了,赶紧的吧(主机可以发送数据,拉高TVALID)

情况3:VALID、READY信号同时到达(主机、从机同时做好了传输数据的准备)

主机拉高TVALID信号的同时从机拉高TREADY信号,分别表明自己可以发送/接收数据,在时钟的上升沿进行数据传输。

(依旧是俗套的例子)快递小哥(主机MASTER)拿了一个快递,准备全部送去小区的菜鸟驿站入库,与驿站值班小妹(从机SLAVE)对话如下:

小妹:来了啊,大兄弟,赶紧的吧(从机可以接收数据,拉高TREADY)

小哥:哎哟我去,这不巧了吗,咱也刚到(同时主机也可以发送数据,拉高TVALID)

5、事务结构

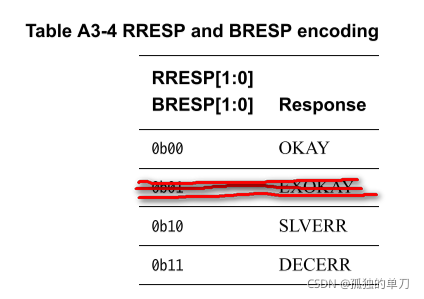

响应

读响应、写响应信号的响应值在AXI-Full的基础上,删除了专属访问成功EXOKAY,支持的值如下:

- OKAY (0b00):正常访问成功。表示已成功完成正常访问

- SLVERR (0b10):从设备错误。已成功访问从设备,但从设备希望向发端主设备返回错误条件(例如,数据读取无效)

- DECERR (0b11):解码器错误。通常由互连组件生成,用于指示传输事务地址处没有任何从设备

总线位宽(bus width)

AXI-Lite总线只支持固定的传输总线位宽(32bit和64bit),一般来讲使用32bit,只有需要64位原子访问的组件才使用64位接口。

写选通(Write strobes)

(Write strobes这里不知道怎么翻译,知道的朋友可以告诉我一下)

写数据通道上有一个WSTRB信号,该信号可以控制总线数据上的有效字节。比如32位的总线,WSTRB等于4'b0010,那么代表WDATA[15:8]中的数据有效,其他无效。如果要求WDATA[31:0]32位全有效,那么WSTRB就应该等于4'b1111。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?