1、边沿RT的大小对串扰的影响

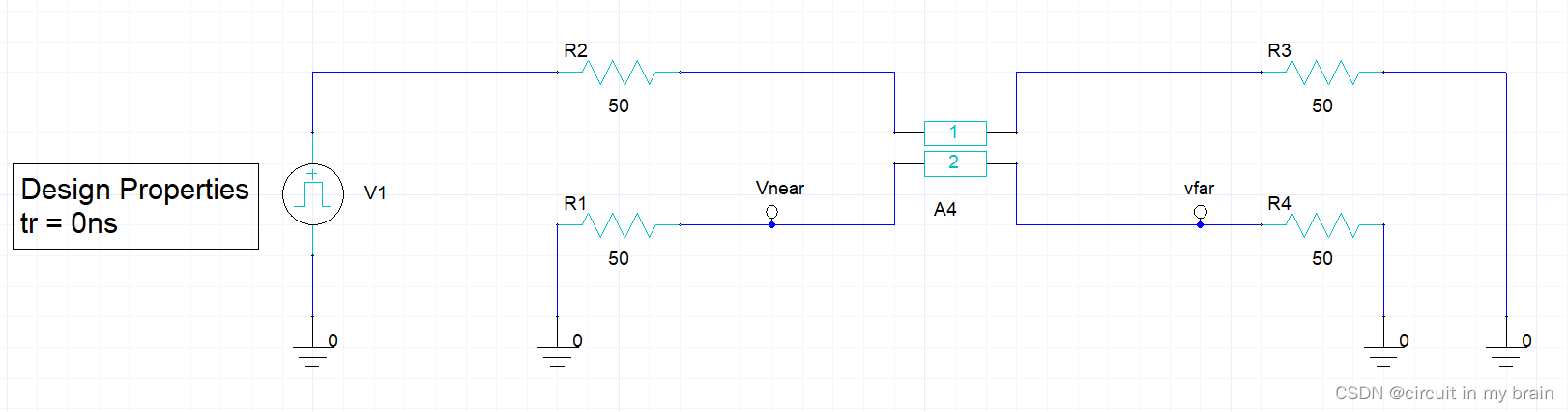

仿真电路如下图所示:

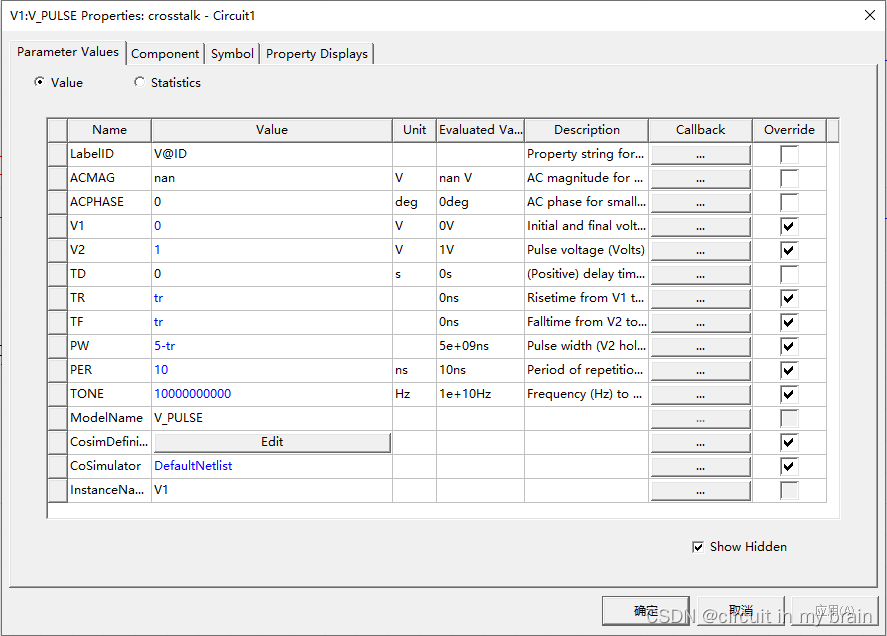

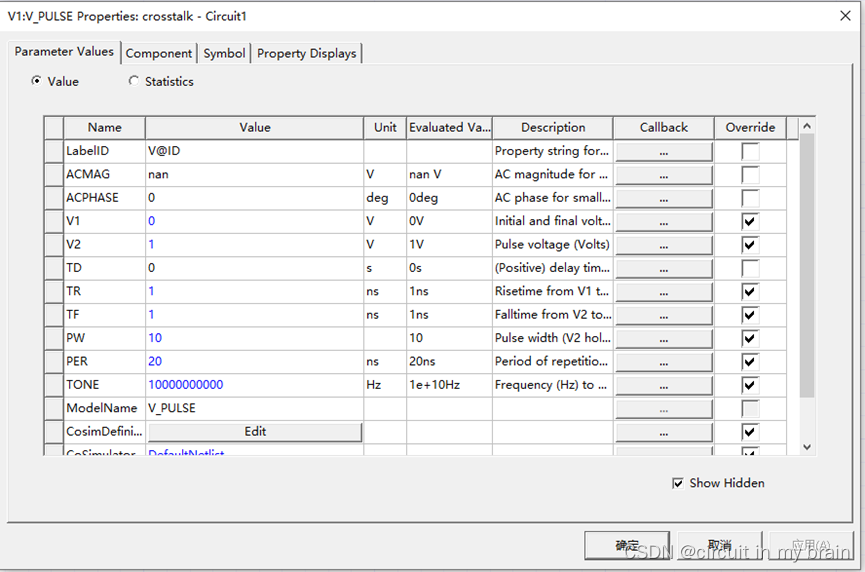

V1为V_Pulse电压源,设置如图所示:

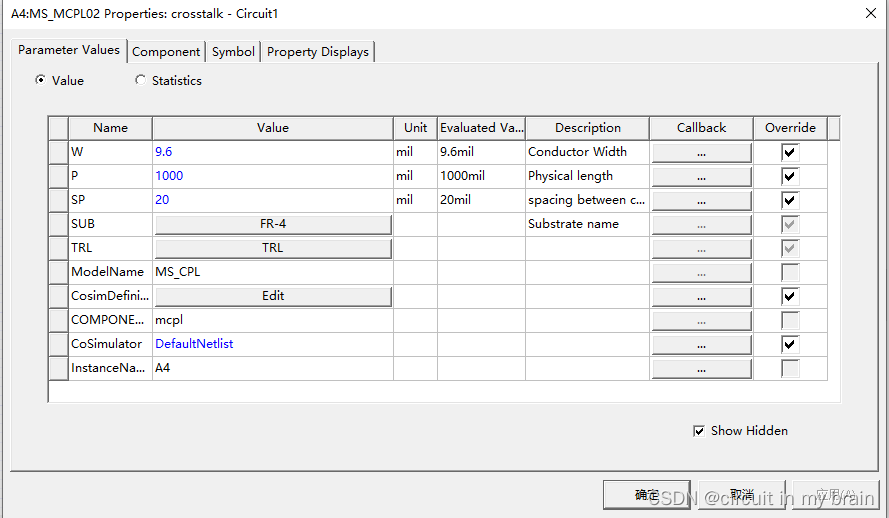

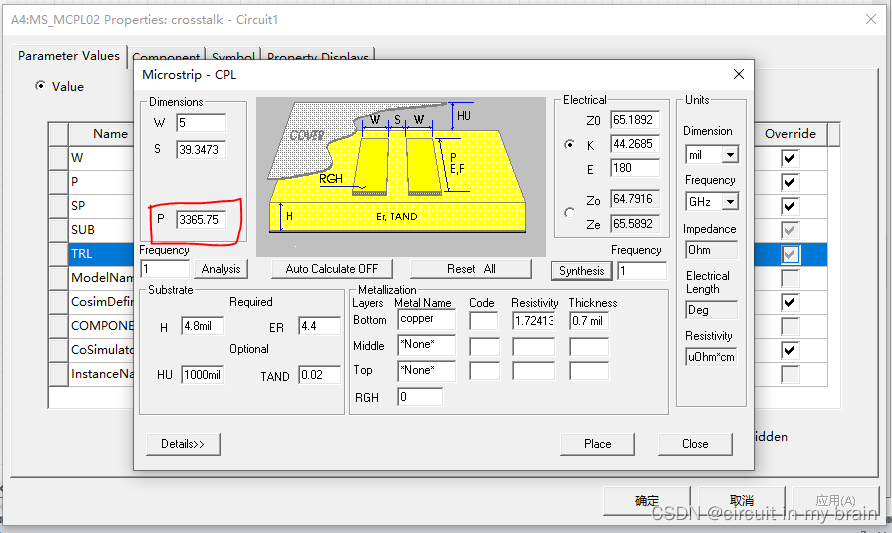

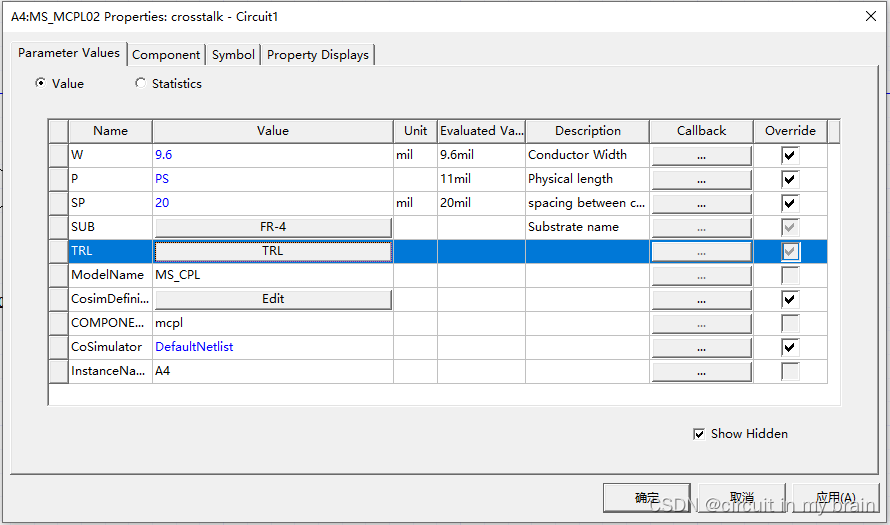

A4为耦合微带线

这里一定要设置为9.6mil,因为介质厚度我设置的是4.8mil,如果没阻抗匹配会在串扰的基础上增加信号的反射,得出的串扰波形可能就是这样的了,所以设置线宽的时候一定要根据介质厚度来做阻抗匹配。

计算饱和长度

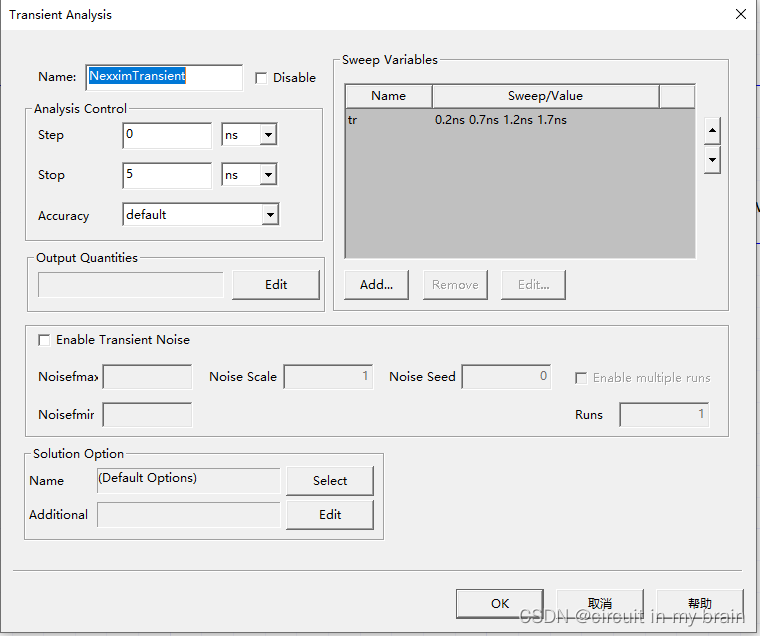

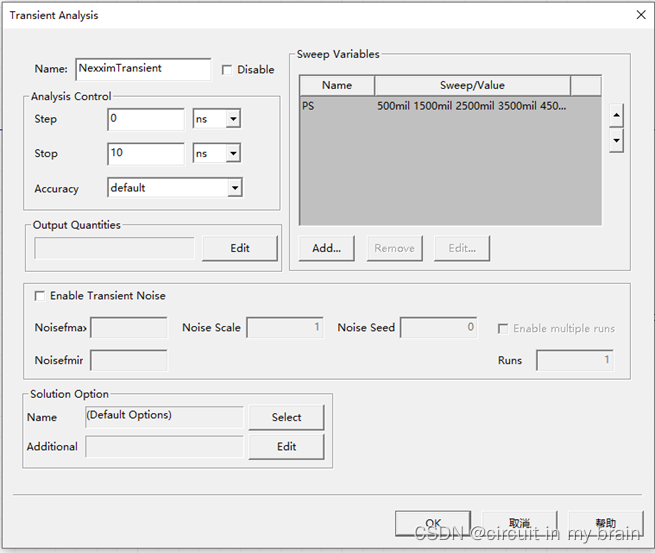

在Analysis菜单下添加边沿扫描点,0.2ns 0.7ns 1.2ns 1.7ns

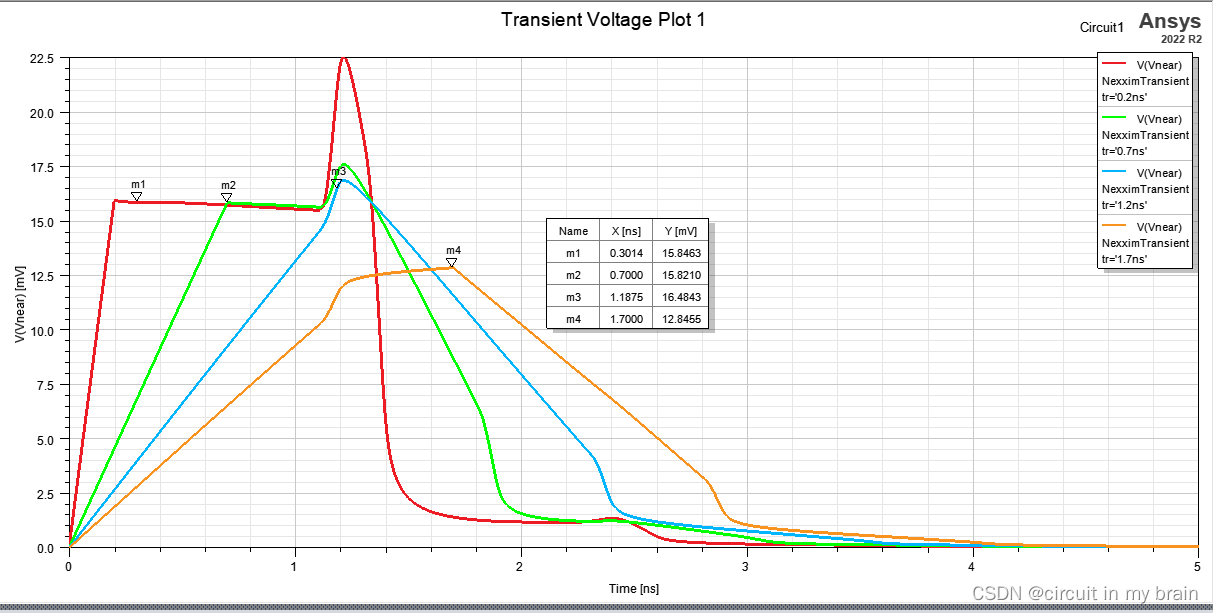

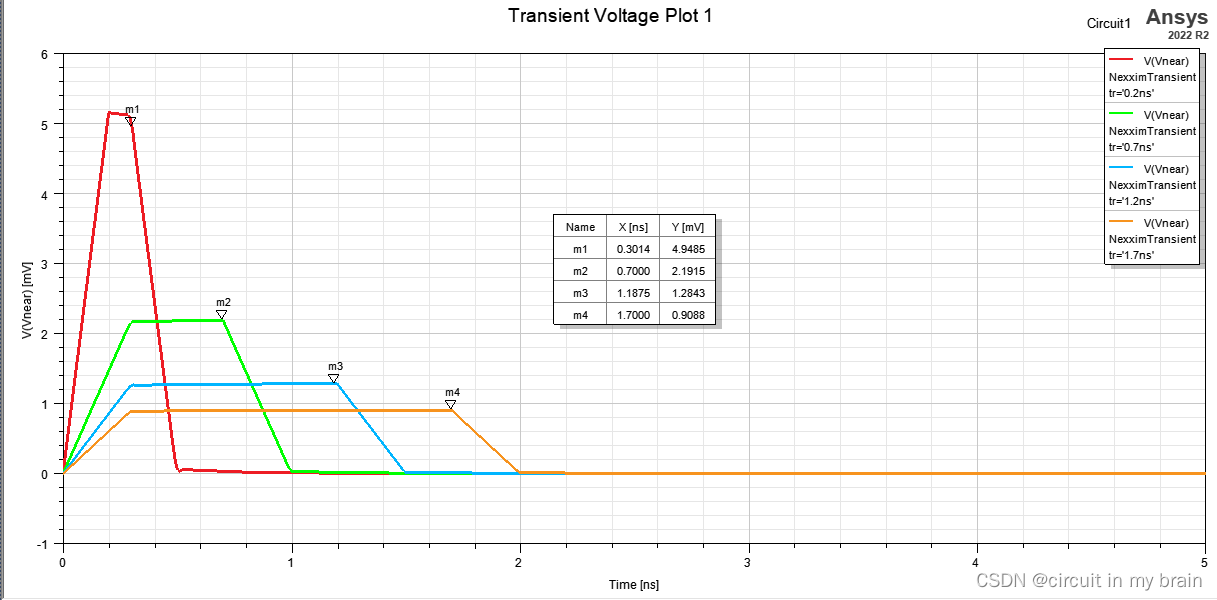

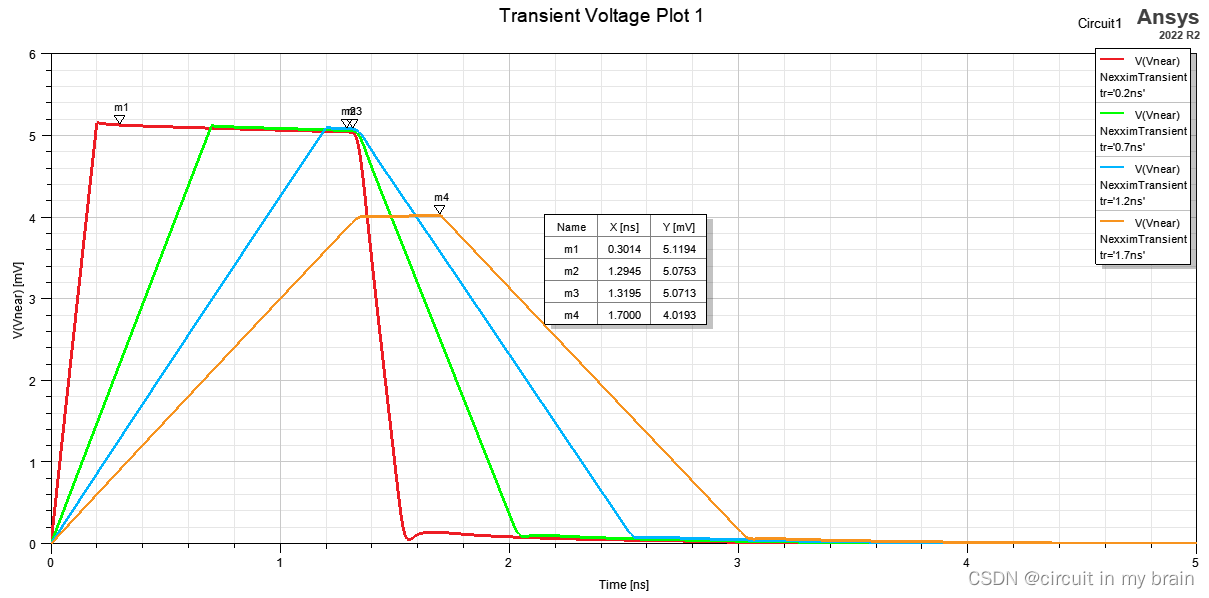

近端串扰波形:

我们耦合长度设置的为1000mil,不同边沿的饱和长度为:

0.2ns*3365.75=673.15mil

0.7ns*3365.75=2356mil

1.2ns*3365.75=4038.9mil

1.7ns*3365.75=5721.7mil

所以当耦合长度为1000mil时,只有0.2ns的边沿能够饱和。

根据上面的波形可以得出结论:

1>当饱和长度1/2*RT *v > 耦合长度PS时,近端串扰的幅度与饱和长度成反比,也就是说,信号边沿越陡,近端的串扰越大。

2>近端串扰的持续时间为2*TD, 2*TD=1000 / 3365.75 = 0.3ns,上图中0.2ns边沿的波形就是持续到了0.3ns。

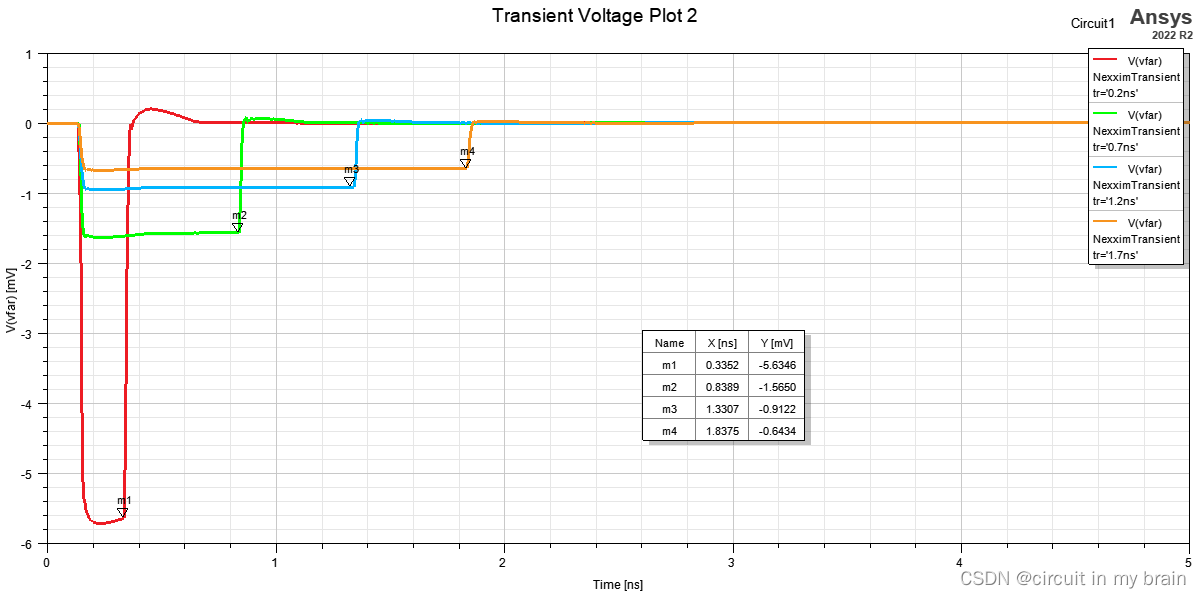

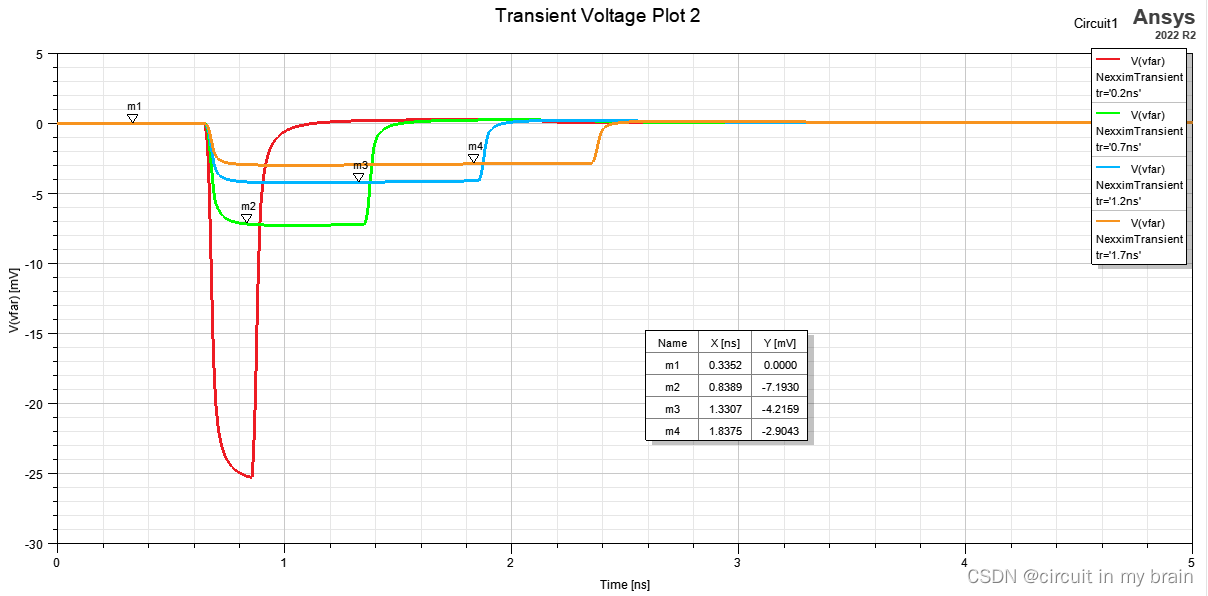

远端串扰波形:

远端串扰的结论:

信号边沿越短,远端串扰的幅度越大。

修改耦合的长度为4500mil时

近端串扰波形:

耦合长度修改为4500mil以后0.2ns 0.7ns 1.2ns这三个边沿的饱和长度都小于耦合长度了,可以看出:

1>当饱和长度1/2*RT*v < 耦合长度PS时,近端串扰的幅度与信号的上升时间没有关系了。

2>近端串扰的持续时间2*TD = 4500mil / 3365.75 =1.3ns,从上面的图中可以看出,近端串扰的持续时间确实为1.3ns。

远端串扰波形:

2、不同的耦合长度对串扰的影响

修改信号源V1把上升时间定为1ns,脉宽10ns,周期20ns。

修改耦合线A4把耦合长度修改为变量ps

在analysis菜单下增加ps的扫描变量,1ns的边沿,饱和长度为3000mil左右,我们设置500mil 1500mil 2500mil 3500mil 4500mil这几个耦合长度

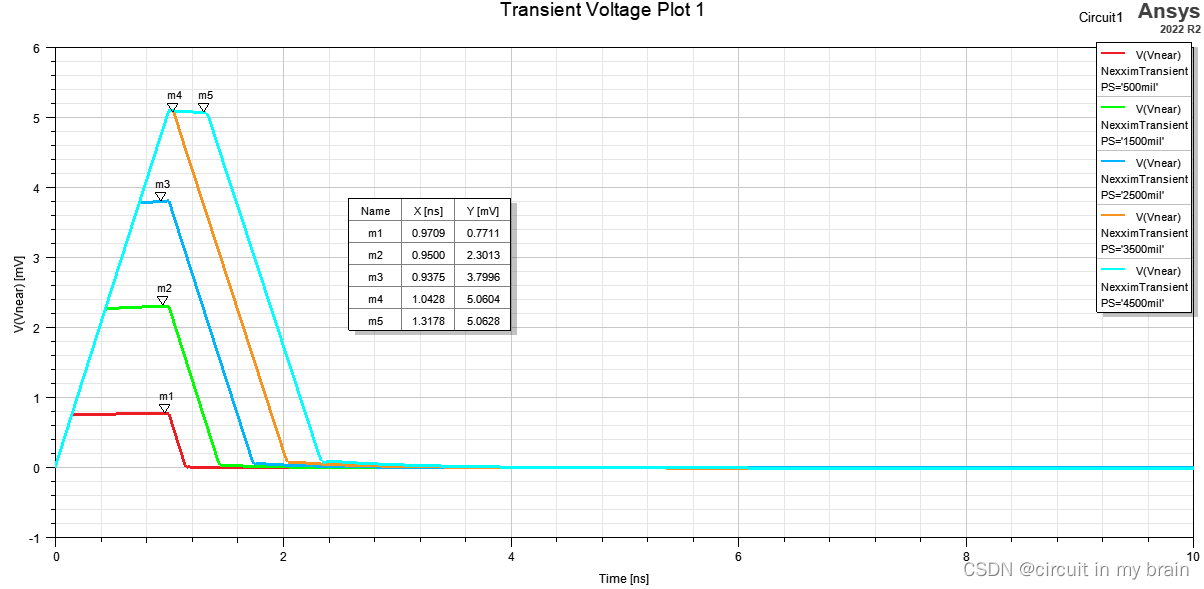

近端串扰的波形:

从仿真结果看我们可以得出这样的结论:

1>当耦合长度PS < 饱和长度 1/2*RT*V 时,耦合的越长,近端串扰的幅度就越大。

2>当耦合长度PS > 饱和长度 1/2*RT*V 时,串扰的幅度与耦合的长度就没有关系了。

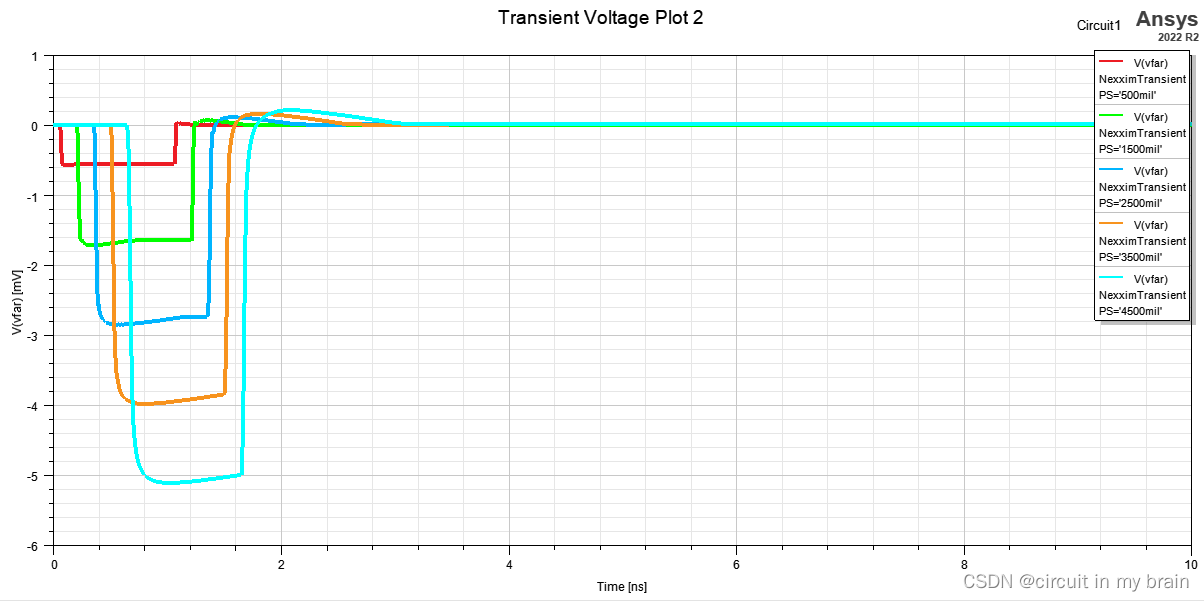

远端串扰的波形:

远端串扰的幅度和耦合长度正相关,耦合的越长,远端串扰的幅度就越大。

参考:

ANSYS_Q3D仿真激光发射的寄生电感_ansys q3d-CSDN博客

https://www.ansys.com/zh-cn/products/electronics/ansys-siwave

5093

5093

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?