DDR的技术发展

| 标准名称 | 内核时钟(MHz) | I/O时钟(MHz) | 工作电压(v) | 预取位数 | 突发长度 | 数据速率(MT/s) | 数据带宽(GB/s) | 拓扑 |

| SDRAM | 100-166 | 100-166 | 3.3 | 1 | / | 100-166 | 0.8-1.3 | T |

| DDR | 133-200 | 133-200 | 2.5 | 2n | 2 | 266-400 | 2.1-3.2 | T |

| DDR2 | 133-200 | 266-400 | 1.8 | 4n | 4 | 533-800 | 4.2-6.4 | T |

| DDR3 | 133-200 | 533-800 | 1.5 | 8n | 8 | 1066-1600 | 8.5-14.9 | Fly-by |

| DDR4 | 133-200 | 1066-1600 | 1.2 | 8n | 8 | 2133-3200 | 17-21.5 | Fly-by |

| DDR5 | ? | 1600-3200 | 1.1 | 16n | 3200-6400 | 32 | Fly-by |

DDR3之前都是内核时钟与外部IO的时钟的Prefetch预取数的倍数关系,DDR4是引入bank grounp的概念,导致与DDR3同样的预取数,但是IO时钟可以加倍,由于上下边沿采样数据,所以数据的速率又是IO时钟的2倍关系。

数据速率和带宽的关系是:数据速率*位宽 = 数据带宽

DDR4内部框图

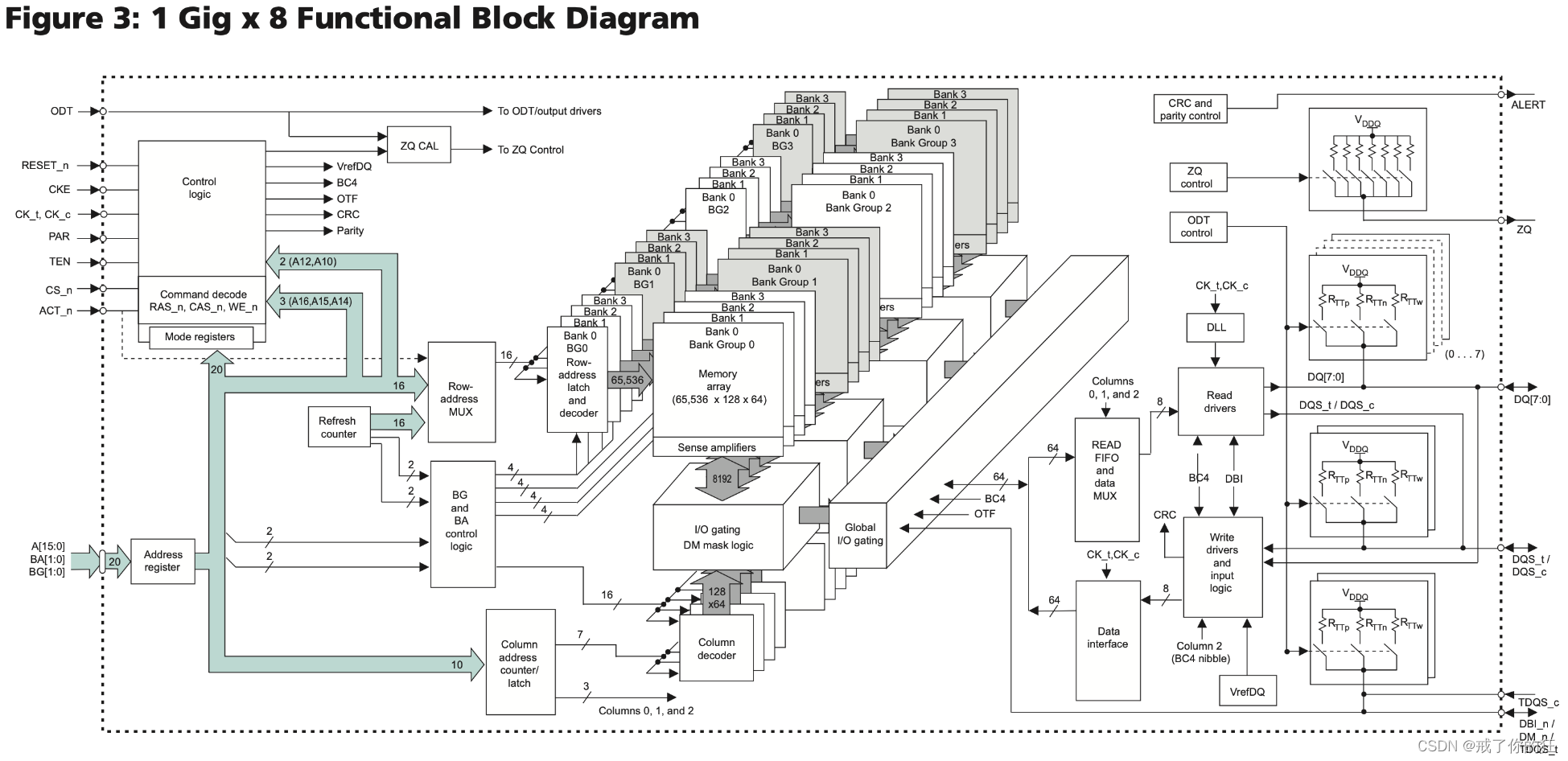

图: MT40A1G8 的内部框图

1Gx8表示SDRAM具有8位的I/O数据位宽度(参见图中右侧的DQ[7:0]信号)。所以8G也有2Gx4,4位I/O宽度,512M x 16的16位I/O数据位宽度。

每个内存阵列为65536x128x64,称为一个bank,4个bank组成一个bank组,共有4个bank组,所以总容量为65536*128*64*4*4= 8Gb。这里注意存储的最小单元就是1bit。

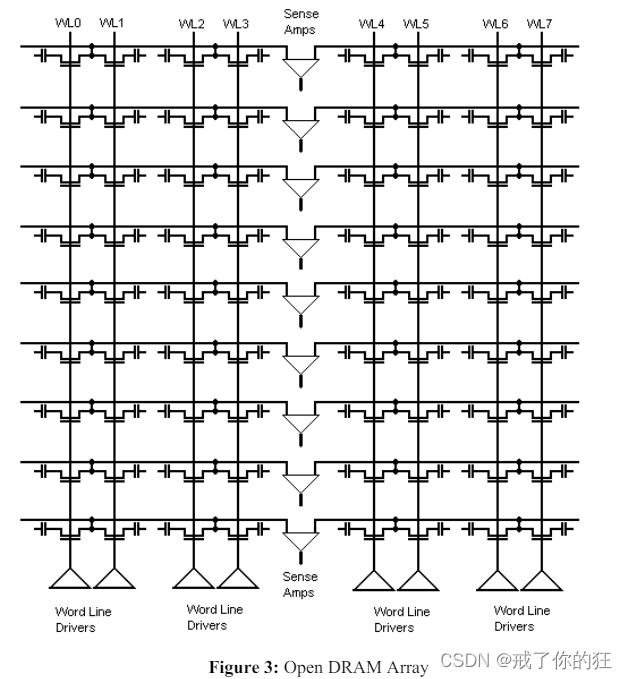

具体来说,在65536x128x64的每个存储阵列规格中,65536代表行数,每行存储128*64=8192位的数据,同时也是

图中Sense放大器与I/0栅极、DM掩码逻辑之间传输的位宽。每行有1024列,每列包含8位数据。由于DDR4预取宽度为8n,一次访问需要8列数据,即64位。所以每一行都有128个64位,这就是65536x128x64位中的128x64的来源。

DDR3内部框图

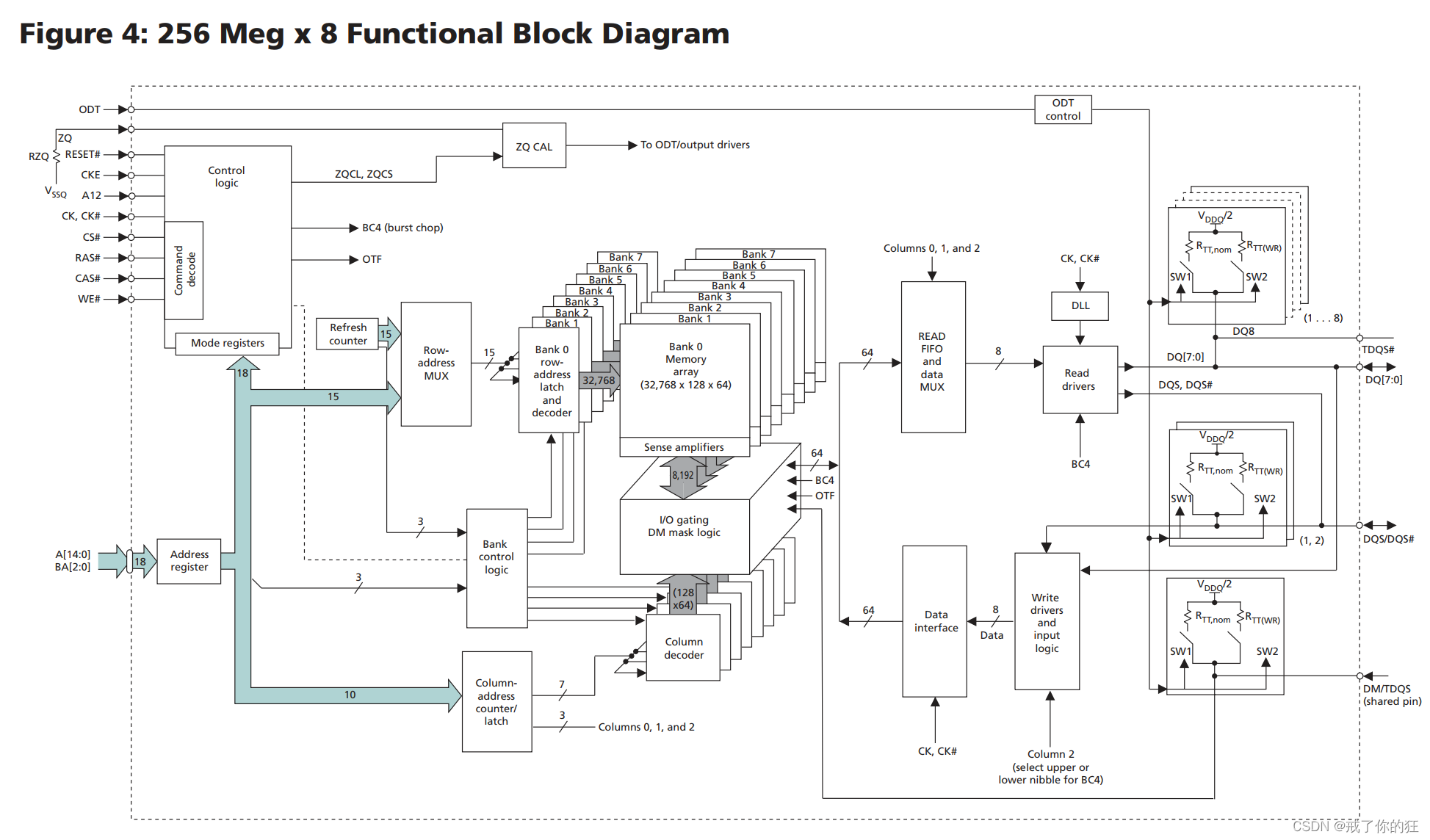

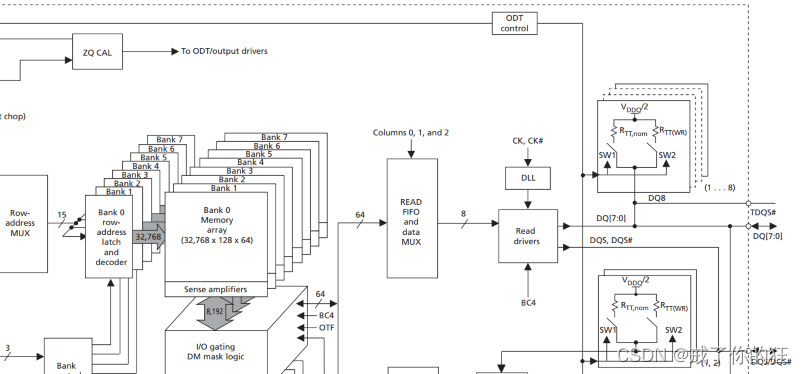

图:MT41J256M8 的内部框图

DDR3中没有bank组的概念,只有8个bank。

32768x128x64的每个存储阵列规格中,32768代表行数,每行存储128*64=8192位的数据,同时也是

图中Sense放大器与I/O栅极、DM掩模逻辑之间传输的位宽。每行有1024列,每列包含8位数据。DDR3预取宽度为8n,一次访问需要8列数据,即64位。所以每一行都有128个64位。

容量计算:

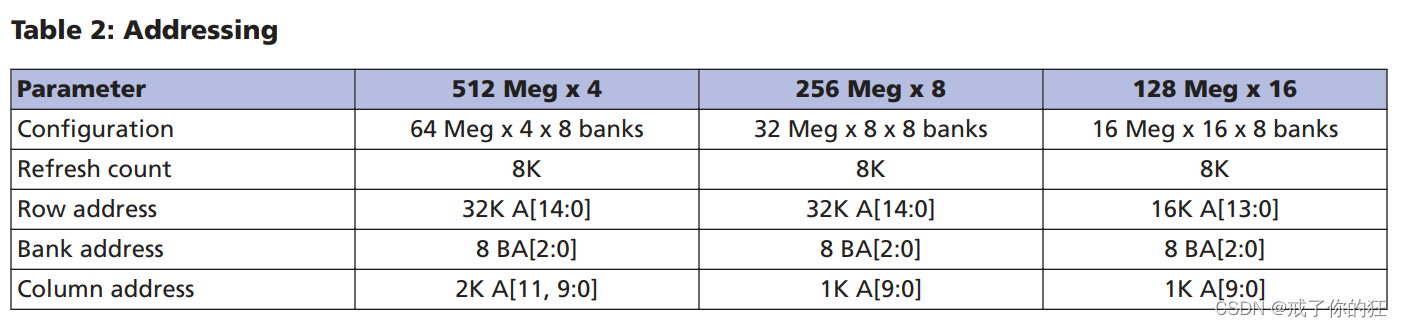

以256Meg x 8这个规格的内存计算,32k *128 * 8 *8 *8 = 2Gb,这3个8分别来自bank,位宽,prefetch。

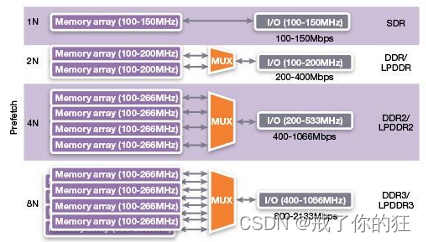

1、DDR的Prefetch预取

以下面的DDR3读取为例,下图中共有8条数据线,每一条数据线都是一个8选1模拟开关的输出,每个输出前面还有8个输入,这个8个输入分别来自8个bank,8个输入会先存在fifo中缓存,MUX读出的时钟就是内核时钟的4倍,由于DDR的时钟上下边沿采样,所以读出8个数据的时间就是1个内核时钟,8个输出就对应64个输入,prefetch的8n的n是指DQ的IO位宽,表示以位宽的8倍来预取数据,n也就是DQ的数量一般可以是4,8,16,对应预取数据就是32,64,128。

读取流程是先激活行地址,锁存行数据到Sense放大器,激活列地址,数据送到输出缓存,利用Sense放大器值刷新行数据,关闭位线,关闭行线,位线预充电。

2、DDR的bank grounp

标准型DDR的总线位宽是64bit,若进行16倍预取,总共有128Byte的数据,超过了目前主流处理器的 Cacheline size(用 于处理器缓存的基本数据单元64Byte 的数据通道,由于Cacheline的 限制,DDR4 没有将预取加倍,而是使用 Bank Group 技术,通过两个不同 Bank Group 的8倍预取来拼凑出一个16倍的预取,当DRAM获得了两份数据的读命令,并且这两份数据的内容分布在不同的Bank Group中时, 由于每个Bank Group可以独立完成读取操作,两个Bank Group 几乎可以同时准备好这两份8倍数据。然后这两份8倍数据被拼接成16倍的数据,数据的传输速度达到内部时钟频率的16倍,较DDR3提升2倍。

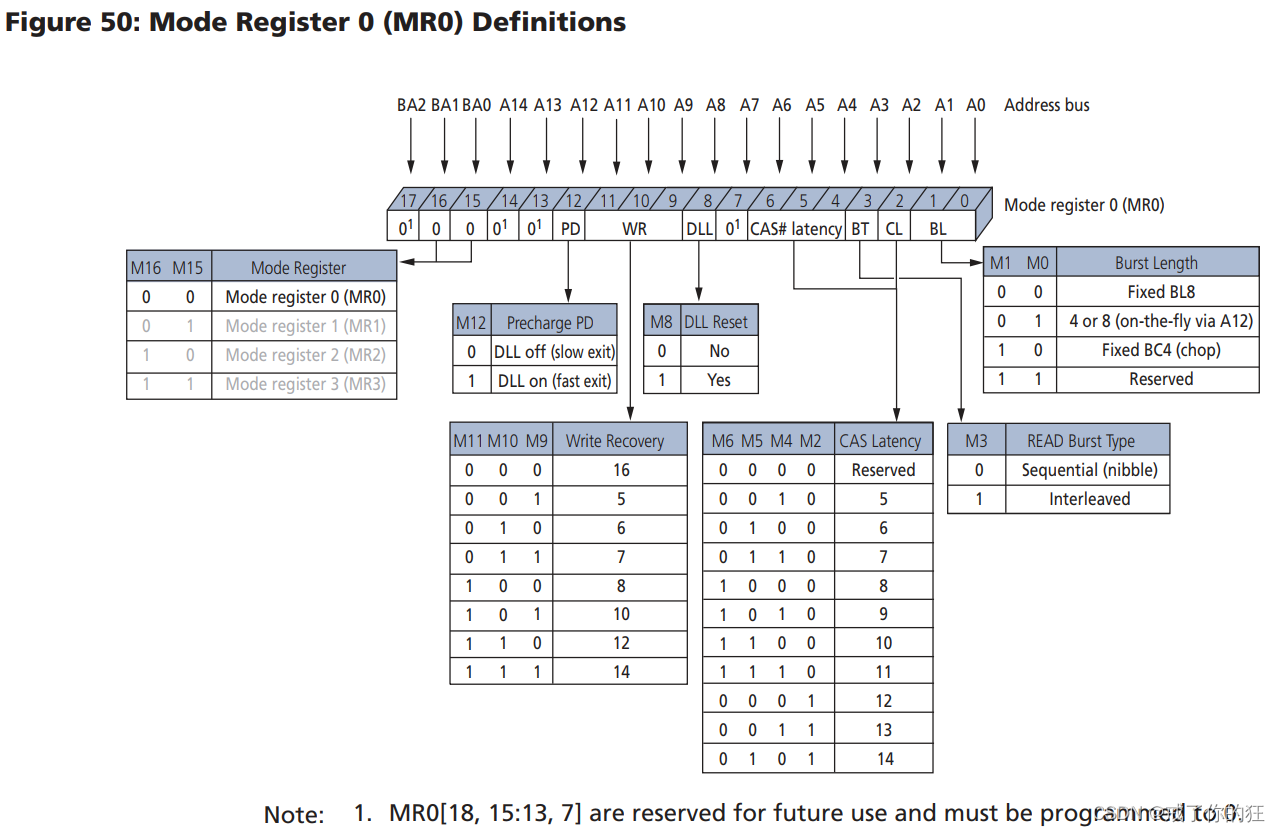

3、DDR的突发长度Burst Length

突发长度BL是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度,DDR3内部配置采用了8n prefetch(预取)来实现高速读写,这也导致了DDR3的BL一般都是8。当然也有为4的设置(BC4),是指另外4笔数据是不被传输的或者被认为无效。BL8还是BC的配置在MR0寄存器配置,这里也可以看出A0~A2是用在了burst的配置上,所以DDR3、4的列地址前三位不用做寻址。

4、预充电Precharge

预充电命令用于停用一个bank中的特定行或整个bank,在完成一次读写操作后,如果对同一个logic bank的另外一行进行寻址,就要把原来的有效工作的行关闭,重新发送行/列地址,这个重新打开行的操作就是预充电。

828

828

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?