一、建立ModelSim工程

1、打开ModelSim软件

打开ModelSim软件,如下图所示:

2、建立工程

在modelsim中建立project,选择File->New->Project,如下图所示:

弹出如下界面:

在“ Project Name”栏中填写工程名,这里的命名方式,我们建议大家最好根据仿真的文件来进行命名,时间久了,当我们记不得这个仿真工程是用来仿真什么的时候,我们看到这个工程名,就能够知道它是用来做什么的了。这里我们把工程命名为“ runled_tb”,也就是在流水灯模块名“ runled”后面添加“ _tb”。“ Project Location”是工程路径,可以根据需要把工程保存到不同的位置。因为前一步骤更改目录的时候已经做了选择,所以这里保持默认即可。下面这两部分是用来设置仿真库名称和路径的,这里我们使用默认即可。设置好工程名、工程位置,我们点击【 OK】按钮,弹出如下图所示界面:

我们可以从该图的选择窗口中看出,它共有四种操作: Create New File(创建新文件)、Add Existing File(添加已有文件)、 Create Simulation(创建仿真)和 Create New Folder(创建新文件夹)。这里我们先选择“ Add Existing File”(添加已有文件),如下图所示:

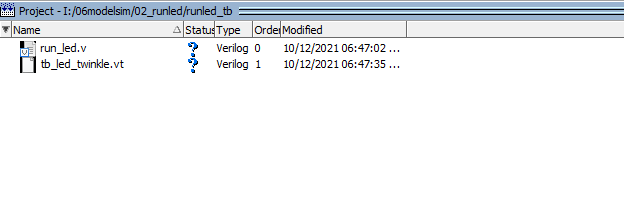

此时可以看到,两个文件“ flow_led.v”和“ flow_led_tb.v” 添加至我们的ModelSim仿真工程中,如下图所示。

二、编译仿真文件

编译的方式有两种: Compile Selected(编译所选)和Compile All(编译全部)。编译所选功能需要先选中一个或几个文件,执行该命令可以完成对选中文件的编译;编译全部功能不需要选中文件,该命令是按编译顺序对工程中的所有文件进行编译。我们可以在菜单栏【 Compile】中找到这两个命令,也可以在快捷工具栏或者在工作区中的右键弹出的菜单中找到这两个命令。下面我们单击Compile All(编译全部),如下图所示。

编译完成后,结果如下图所示:

文件编译后“ Status”列可能会有三个不同状态。除了上图的用“√”表示的通过状态外,还有两个在设计中不希望出现的状态:编译错误(显示红色的“×”)和包含警告的编译通过(对号的后面会出现一个黄色的三角符号)。编译错误即Modelsim无法完成文件的编译工作。通常这种情况是因为被编译文件中包含明显的语法错误, Modelsim会识别出这些语法错误并提示使用者,使用者可根据Modelsim的提示信息进行修改。编译结果中包含警告信息是一种比较特殊的状态,表示被编译的文件没有明显的语法错误,但是可能包含一些影响最终输出结果的因素。这种状态在实际使用中较少出现,这类信息一般在功能仿真的时候不会带来明显的影响,不过可能会在后续的综合和时序仿真中造成无法估计的错误,所以出现这种状态时推荐读者也要根据警告信息修改代码,确保后续使用的安全性。

三、配置仿真环境

编译完成后,接下来我们就开始配置仿真环境,我们在ModelSim菜单栏中找到【 Simulate】

→【 Start Simulation…】菜单并点击,弹出如下右图所示页面。

从配置仿真功能页面中我们可以看出,该页面中包含6个标签,分别是: Design、 VHDL、Verilog、 Libraries、 SDF和Others。对于这6个标签,我们用的最多的是Design、 Libraries和SDF这三个标签了,下面我们就来简单的介绍一下这3个标签,其余的标签我们一般用不到,这里我们就不再进行介绍了。

首先看一下Design标签,该标签内居中的部分是Modelsim中当前包含的全部库,可展开看到库中包含的设计单元,这些库和单元是为仿真服务的,使用者可以选择需要进行仿真的设计单元开始仿真, 此时被选中的仿真单元的名字就会出现在下方的Design Unit( s)位置。Modelsim支持同时对多个文件进行仿真,可以使用Ctrl和Shift键来选择多个文件,被选中的全部文件名都会出现在Design Unit( s)区域。在Design Unit( s)区域的右侧Resolution选项,这里可以选择仿真的时间精度。在Modelsim进行仿真的时候,有一个最小的时间单位,这个单位是使用者可以指定的,如最小单位是1ns,仿真器在工作的时候按1ns为单位进行仿真,对小于1ns发生的信号变化不予考虑或不予显示。因而这个最小时间单位也就是仿真的时间精度。这个选项一般都是设置在默认状态,这时Modelsim依照仿真设计文件中指定的最小时间刻度来进行仿真,如果设计文件中没有指定,则按1ns来进行仿真。最下方的区域是Optimization区域,可以在仿真开始的时候使能优化。接下来我们来看一下Libraries标签,如下图所示。

在该标签中,我们可以设置搜索库。 Search Libraries和Search Libraries First的功能基本一致,唯一不同的是Search Libraries First中指定的库会在指定的用户库之前被搜索。现在我们来看一下SDF标签,如下图所示。

SDF是Standard Delay Format(标准延迟格式)的缩写,内部包含了各种延迟信息,也是用于时序仿真的重要文件。 SDF Files区域用来添加SDF文件,可以选择Add按钮进行加,选择Modify按钮进行修改,选择Delete按钮删除添加的文件。

SDF Options区域设置SDF文件的warning和error信息。第一个“ Disable SDF warning”是禁用SDF警告,第二个“ Reduce SDF errors to warnings”是把所有的SDF错误信息变成警告信息。区域Multi-Source delay中可以控制多个目标对同一端口的驱动,如果有多个控制信号同时控制同一个端口或互连,且每个信号的延迟值不同,可以使用此选项统一延迟。下拉列表中可供选择的有三个选项: latest、 min和max。 latest选项选择最后的延迟作为统一值, max选项选择所有信号中延迟最大的值作为统一值, min选项选择所有信号中延迟最小的值作为统一值。

至此,这三个标签我们就介绍完了,接下来我们在Design标签页面中选择work库中的flow_led_tb模块,在Optimization一栏中取消勾选(注意一定要取消优化的勾选,否则无法观察信号波形),然后点击【 OK】就可以开始进行功能仿真了,其余标签页面中的配置我们使用默认就可以了,如下图所示。

点击【 OK】后弹出下图所示界面

鼠标右键单击“u0_flow_led” ,选择“Add Wave” 选项,如下图所示:

弹出下图所示界面,可以看到信号已经添加到窗口中。

运行后的结果如下图所示:

前面的几个放大镜模样的工具是放大、缩小和全局显示功能,鼠标放到图标上会显示出它们的快捷键,后边的黄色图标是用来在波形图上添加用来标志的黄色竖线,紧跟着的是将添加的黄色竖线对齐到信号的下降沿和上升沿。利用上述工具出来, 可以看到在仿真结果中当计时器counter计到10时, led[0]由高电平变低电平, led[1]由低电平变成高电平,且counter清零,形成了最初流水态,与预设的功能相同。

四、仿真程序源码

1、tun_led.v

// Target Devices: XC7Z020-CLG400

// Tool versions: VIVADO2017.4

// Description: water led

// Revision: V1.1

// Additional Comments:

//1) _i PIN input

//2) _o PIN output

//3) _n PIN active low

//4) _dg debug signal

//5) _r reg delay

//6) _s state machine

//

module run_led(

input sys_clk , //系统时钟

input sys_rst_n, //系统复位,低电平有效

output [1:0] led //LED灯

);

//reg define

reg [25:0] cnt ;

//*****************************************************

//** main code

//*****************************************************

//对计数器的值进行判断,以输出LED的状态

//assign led = (cnt < 26'd2500_0000) ? 2'b01 : 2'b10 ;

assign led = (cnt < 26'd5) ? 2'b01 : 2'b10 ; //仅用于仿真

//计数器在0~5000_000之间进行计数

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

cnt <= 26'd0;

// else if(cnt < 26'd5000_0000)

else if(cnt < 26'd10) //仅用于仿真

cnt <= cnt + 1'b1;

else

cnt <= 26'd0;

end

endmodule

2、tb_led_twinkle.vt

`timescale 1ns / 1ps

module tb_led_twinkle();

//输入

reg sys_clk;

reg sys_rst_n;

//输出

wire [1:0] led;

//信号初始化

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#200

sys_rst_n = 1'b1;

end

//生成时钟

always #10 sys_clk = ~sys_clk;

//例化待测设计

run_led u_run_led(

.sys_clk (sys_clk),

.sys_rst_n (sys_rst_n),

.led (led)

);

endmodule

五、打开已建立过的工程

File -> Open

在弹出的窗口中,文件类型选.mpf

然后路径指到工程所在文件夹,选择建立的.mpf文件即可

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?