DFT中的SCAN、BIST、ATPG基本概念

SCAN

定义

扫描路径法是一种针对时序电路芯片的DFT方案,目标是在不影响正常功能的情况下来能够提高可控性和可观测性。

原理

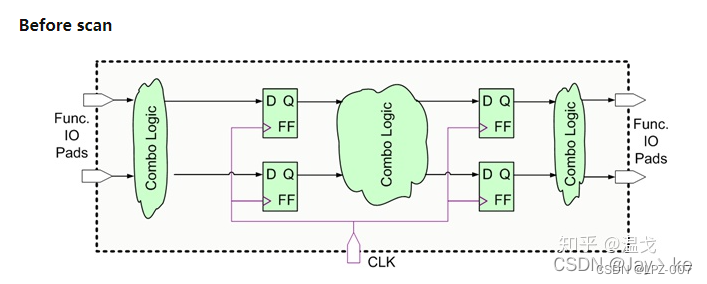

原理是将时序电路可以模型化为一个组合电路网络和带触发器(Flip-Flop,简称FF)的时序电路网络的反馈。

实现

具体实现步骤共分为两步:

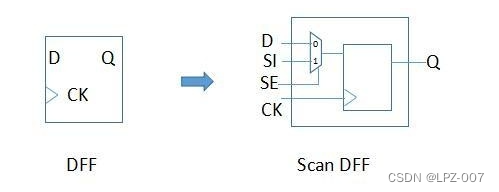

step1:DFF替换为SDFF

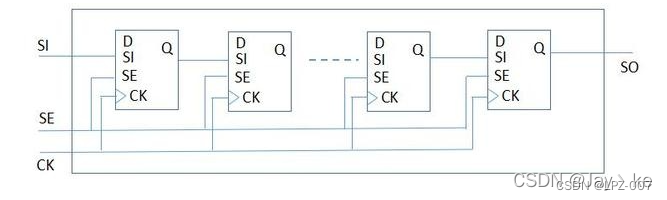

step2:将SDFF串联起来形成scan chain

示例

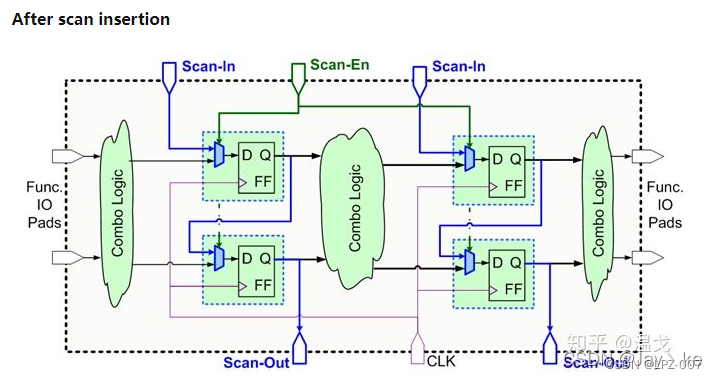

测寄存器

- Scan-En=0,关闭scan,不影响正常功能

- Scan-En=1,打开scan,驱动clk并在scan-in输入测试数据,并在scan-out检测输出数据。若输出数据与输入数据不匹配,则说明对应串联的scan chain存在故障。

测组合逻辑

- Scan-En=1,打开scan,将scan-in的输入数据送至组合逻辑的输入

- Scan-En=0,关闭scan,进行中间组合逻辑部分的计算,并将结果正常送至输出端的两个寄存器总

- Scan-En=1,打开scan,将两个输出通过scan chain移位从右侧Scan-out接口输出,并对比其余期望值是否一致。

BIST

定义

BIST(Built-in Seft Test)内建测试,是DFT的一种技术。

原理

BIST是在设计时在电路中植入相关功能电路用于提供自我测试功能的技术,以此降低器件测试对自动测试设备(ATE)的依赖程度。

实现

由三部分组成:

- TPG (test pattern generator)测试向量生成器:用来自动生成测试向量,灌入CUT(circuit under test)的输入引脚。

- ORA (output response analyzer)输出响应分析器:对待测电路的输出进行压缩对比,来确定电路是否有错误。

- BIST controller 内建自测试控制器:控制何时将什么样的数据用到被测电路上,控制被测电路的时钟并决定何时读取预期响应。

ATPG

定义

Automatic Test Pattern Generation (ATPG)是DFT(Design for Testability,可测试性设计)中常用的技术,用于自动生成测试向量。

原理

基于一定的算法,通过对电路的描述,自动生成能够检测到电路中所有故障的测试向量。前提是插好scan chain,然后才能通过ATPG来进行DFT。

实现

通过工具完成即可

注意

- SCAN、BIST通常是由工具完成,同时也需要一定的能力来进行一些手工设置。

- DFT部分做的越完善,ATE需要做的也会相对越少。

- SCAN、BIST均会带来面积方面的增加,但能够很大程度提高芯片质量。

参考链接

scan: https://zhuanlan.zhihu.com/p/201353304

bist:https://zhuanlan.zhihu.com/p/169490809

本文详细介绍了DFT中的SCAN(扫描路径法)、BIST(内建自我测试)和ATPG(自动测试模式生成)的基本概念、工作原理和实现步骤,强调了它们在提高芯片质量和减少ATE依赖中的作用,以及可能带来的面积成本。

本文详细介绍了DFT中的SCAN(扫描路径法)、BIST(内建自我测试)和ATPG(自动测试模式生成)的基本概念、工作原理和实现步骤,强调了它们在提高芯片质量和减少ATE依赖中的作用,以及可能带来的面积成本。

5533

5533

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?