1.参数理解

jesd204b主要参数及含义如下

| 参数 | 含义 |

|---|---|

| M | 每个器件的转换数(理解为每个AD或者DA的转换通道数) |

| N | 转换分辨率(即AD采样位数) |

| N’ | 所需半字节总的位数,即所需nibble数乘以4,也可称为协议的字长(word size) |

| S | 每一帧所传输的采样数 |

| L | 数据传输的通道(lane)数量 |

| F | 每一帧的字节数(octets) |

| K | 多帧情况下的帧数 |

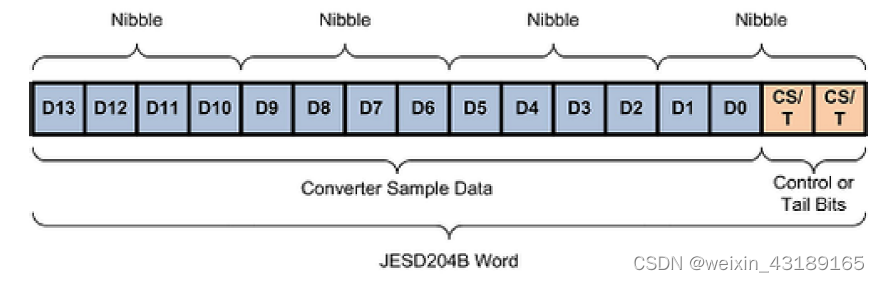

举一个简单的例子,假设一个4通道的AD芯片,分辨率是14位,则M=4,N=14。在JESD204B的标准中要求,采样的一个数据必须要分解成半字节(nibble,4bit),那么14位的AD数据,能分解成3个nibble,还余下2位。那么余下的这2位,要与控制位(CS)或尾位(T)组成一个新的nibble。所以14位采样率的AD,需要4个nibble,那么N’=16,组帧结构如下图所示,发送时先发送高位,再发送低位。同理,如果12位的AD,只需要3个nibble,不需要控制位或尾位在补充,则N’=12。所以可以得知

N

′

=

N

+

C

S

+

T

N'=N+CS+T

N′=N+CS+T。

F=2,即每一帧传输中有2个字节的数据

S表示每一帧传输的采样数,S必须是整数,以防止数据的串扰。一般而言S=1,即每一帧传输1个采样数据,这样设计还有一个好书就是使得帧时钟(frame clock,FC)与采样时钟(sample clock)同频。

2.数据传输

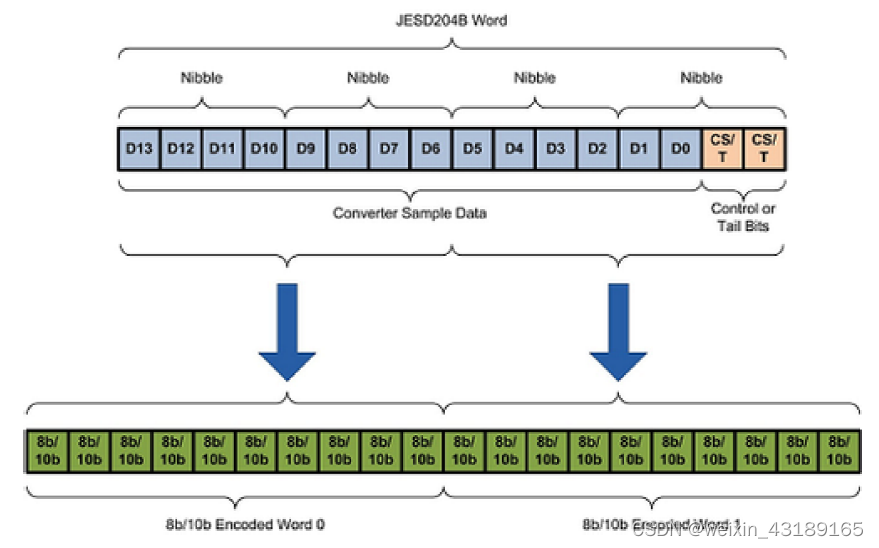

上面的例子,此时JESD204B协议的一个字长是16,即4个nibble或2个通信字节。那么这2个字节是如何进行组帧并传输的呢?首先一帧数据在发送之前,先要经过8B/10B编码,一个字节的数据经过一定的编码规则转换成10位的数据,如下图所示。

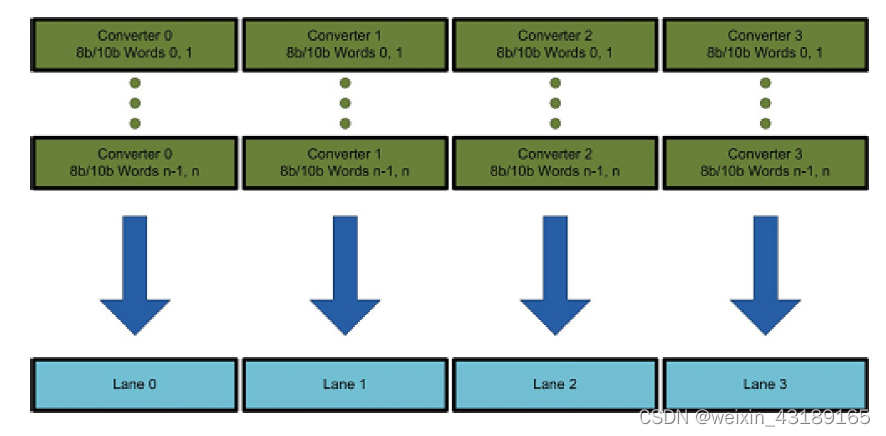

例子中的AD有4个采样通道,每一个通道的数据经过上图编码之后进入各自的传输通道,即4条通道(lanes),并且数据经过转换后都是对齐出现在各自的通道上。如下图所示显示了4个转换器器在4个传输通道上的映射关系。每一个采样经过8B/10B编码之后形成wor0和word1组成一帧数据在线路上进行串行传输。

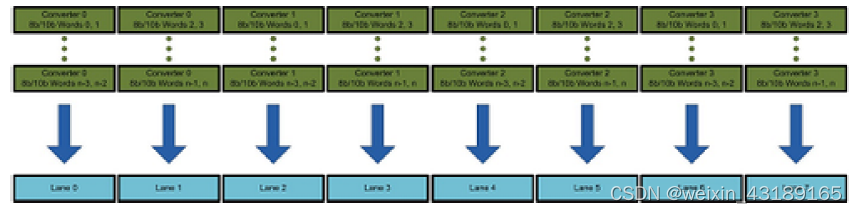

同理,如果上述AD的其他参数不变,唯独传输通道增加1倍,即8条lanes,意味着同一时刻可以传输2个采样数据(word0和word1、word2和word3),如下图所示。因为总的数据吞吐量不变,则意味着通信速率降低了一倍,从10Gb/s降为5Gb/s。在JESD204A协议中并不支持一个转换器通过两路通道传输数据的方式,直到204B才增加了这种方式的支持。总的来说速率和传输通道数的关系是,要保持低速率,则需增加通道数。

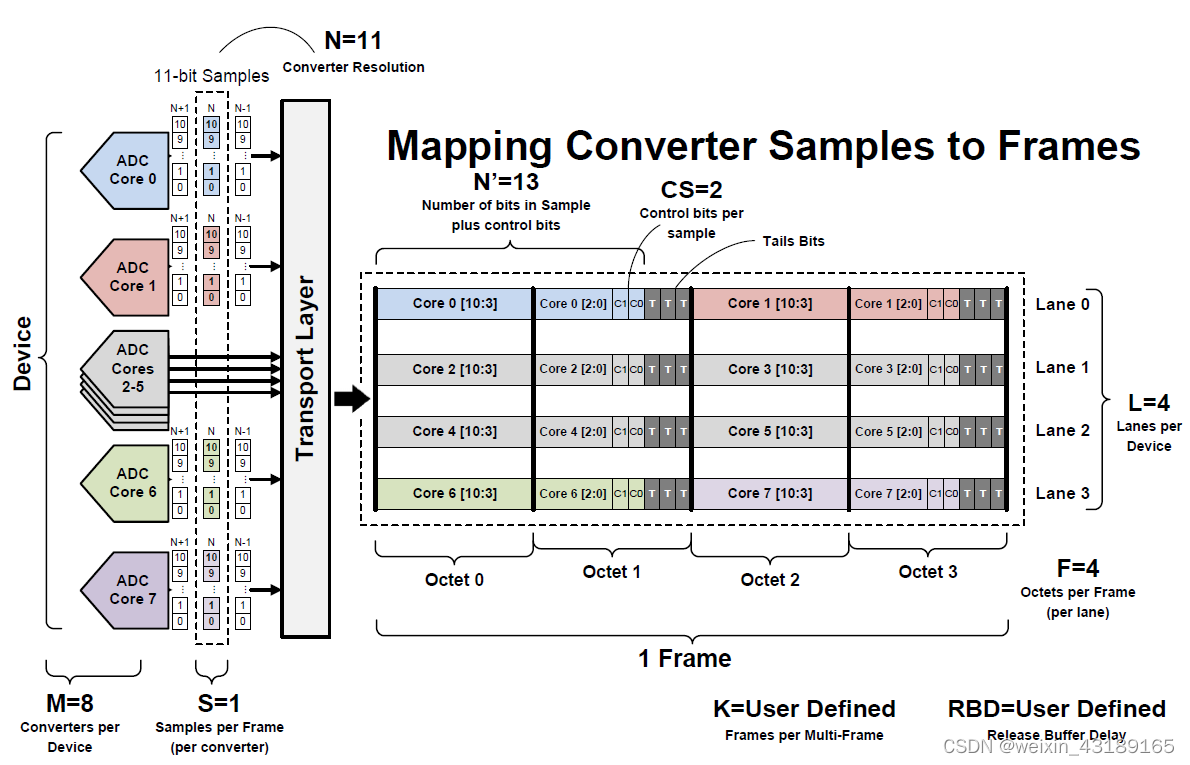

如图所示,为一个8通道采样,11位的AD,拥有4条传输通道,即M=8,N=11,L=4。根据上面的说明,N’=13(此处TI的定义和ADI的略有不同,ADI的定义下N’=16,但不影响理解),补充了2个控制位和3个尾位。要是同一帧的传输下,4条通道装下8个转换器的一个数据,需要设置F=4,即4个字节,每2个转换器共用一个传输通道,各自传输2个字节的数据。这张图一目了然的展示了连接参数对组帧方式的作用

3.链路建立

3.1代码组同步

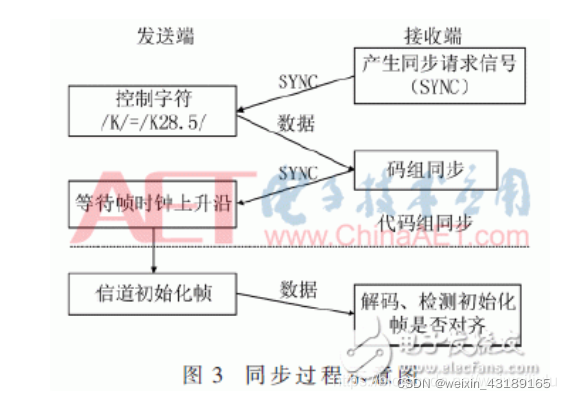

CGS:代码组同步(code group sync)当发送端检测到SYNC 信号为低电平时启动发送8B10B中的K28.5码,本数据段不进行扰码和字节替换操作,接收端检测到最少4个K28.5后可释放SYNC信号。

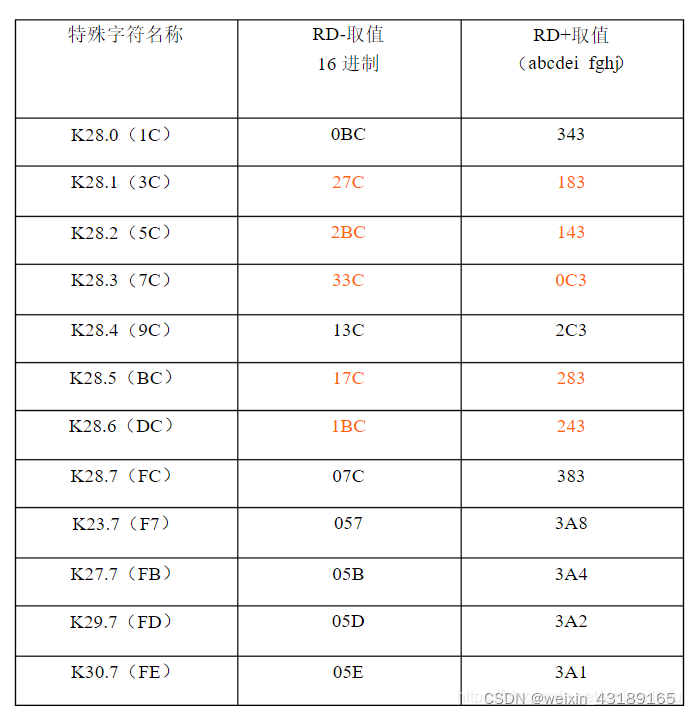

3.2特殊字符

3.3初始化多帧序列

ILA:初始化多帧序列(initial lane alignment)该阶段发送连续的4个初始化多帧(多帧是由K个帧组成,字节数为K*F),本段不进行扰码和字节替换。

-

在JESD204B中,发送模块捕捉到SYNC信号的变换,在下一个本地多帧LMFC边界上启动ILAS。

-

ILAS主要对齐链路的所有通道,验证链路参数,以及确定帧和多帧边界在接收器的输入数据中的位置。

-

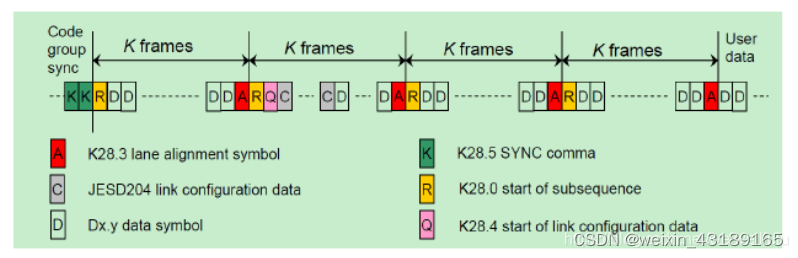

ILAS由4个多帧组成。其中,/K/=/K28.5/字符用于代码组同步;/R/=/K28.0/标志着初始化多帧的开始;/A/=/K28.3/字符标志着初始化多帧的结束;/Q/=/K28.4/字符用于指示接收端用户所配置的信息即将开始。

-

这些特定的控制字符只用于初始化通路对齐序列中,而不会在数据传输的任何其他阶段出现。CGS和ILAS阶段不加扰。

每个多帧最后一个字符是多帧对齐字符/A,第一,三,四个多帧以/R字符开始,以/A字符结束。接收器以个通道的最后一个字符/A对齐接收器内各通道内各多帧的末尾。ILA 初始化多帧以K28.0开始以K28.3结束,其中第二个多帧的第二字节是K28.4关键字用来指示当前多帧在紧跟着K28.4的后续14个字节是参数配置信息。

4.时钟要求

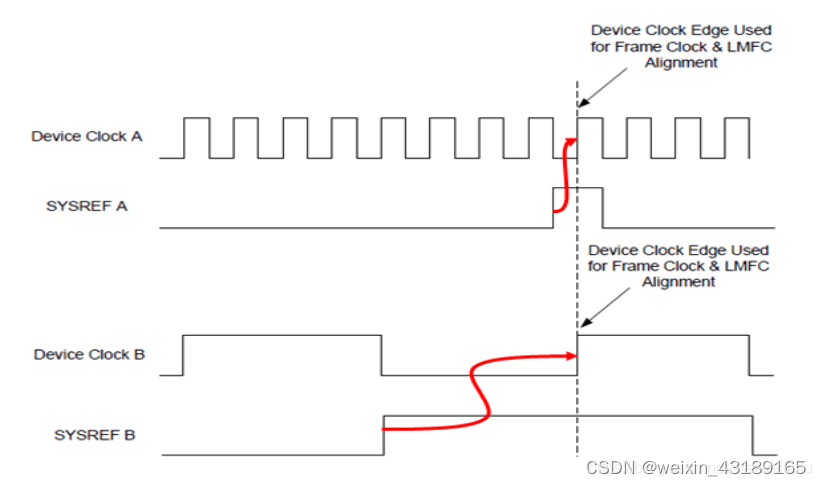

下图是典型的JESD204B系统的系统连接,device clock 是器件工作的主时钟,一般在数模转换器里为其采样时钟或整数倍频的时钟,其协议本身的帧和多帧时钟也是基于Device clock。SYSREF是用于指示不同转换器或者逻辑device clock 的沿,如下图所示,device clock和SYSREF必须满足的时序关系。SYSREF的第一个上升沿要非常容易的被device clock 捕捉到。

SYSREF可以是周期信号,或者脉冲的周期信号,也可以是单脉冲信号。只有在器件请求同步时,才产生SYSREF信号,高电平有效。一般是通过DEVICE CLOCK 的上升沿抓取,单也可以通过下降沿抓取。对于周期的SYSREF来说,其频率必须是LMFC的整数倍

SYSREF = LMFC *n(n为整数)。单脉冲模式,可以不按照LMFC整数倍计算

参考文献

原文链接:https://www.cnblogs.com/rouwawa/p/13588175.html

原文链接:https://blog.csdn.net/weiweiliulu/article/details/106495969

2028

2028

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?