一、前言

在Verilog项目开发过程中某功能是,一部分代码可能有时候用,有时候不用,为了避免全部编译占用资源,可以使用条件编译语句;尤其在大型项目中还可以节约大量的时间。

二、语法

语法书写格式:

(`define FLAG1/2/3)

`ifdef/`ifndef FLAG1

// Statements

`elsif FLAG2

// Statements

`elsif FLAG3

// Statements

`else

// Statements

`endif其中,`ifdef/`ifndef和`endif之间的`elsif和`else都是可选的。

对条件编译的理解很好理解,都是字面逻辑。唯一值得探讨的一点是,条件编译的FLAG是否必须由`define语句宏定义,可不可以在代码中自己定义?答案是必须要`define来定义,也即条件编译的使用与`define是紧密相关的。比如下面的例子尝试自定义变量在条件编译中使用,但编译工具并不支持,对比可以发现并不认同自己定义的变量。

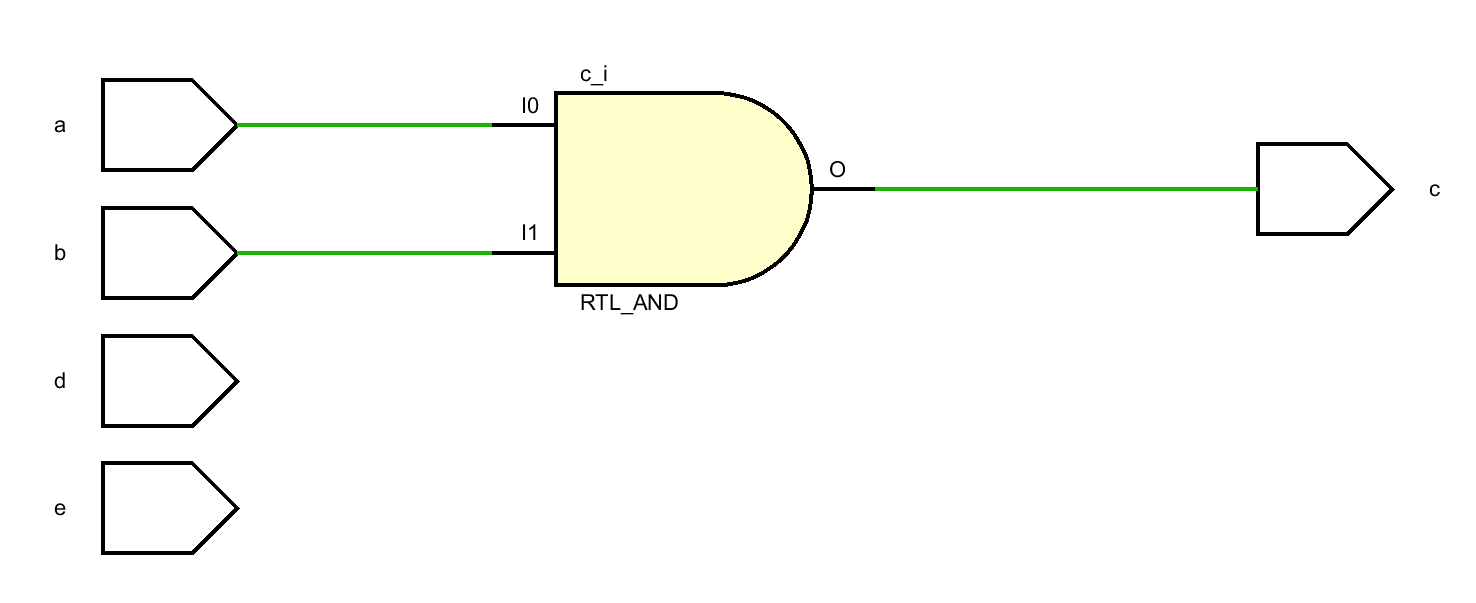

使用宏定义的:

`timescale 1ns / 1ps

`define MACRO_FLAG; //use `define

module prac_condition_compile(

input a,

input b,

output c,

input d,

input e

);

`ifdef MACRO_FLAG

assign c = a&b;

`endif

`ifndef MACRO_FLAG

assign c = d & e;

`endif

endmodule

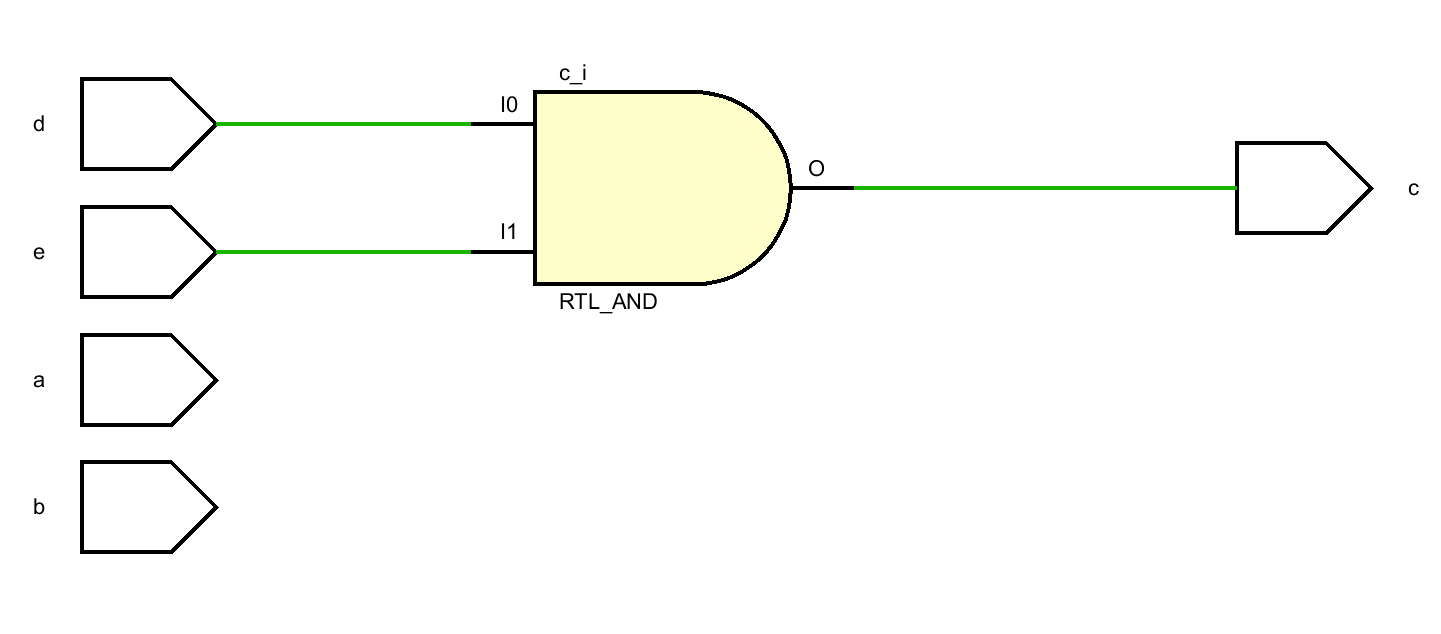

使用自己的定义的:

`timescale 1ns / 1ps

//`define MACRO_FLAG;

module prac_condition_compile(

input a,

input b,

output c,

input d,

input e

);

wire MACRO_FLAG; //do not use `define

`ifdef MACRO_FLAG

assign c = a&b;

`endif

`ifndef MACRO_FLAG

assign c = d & e;

`endif

endmodule

本文介绍了在Verilog项目开发中如何使用条件编译语句来节省资源,特别强调了条件编译依赖于`define`宏定义,而不是直接在代码中定义变量。作者通过示例展示了正确使用`ifdef`、`ifndef`等关键字的方法。

本文介绍了在Verilog项目开发中如何使用条件编译语句来节省资源,特别强调了条件编译依赖于`define`宏定义,而不是直接在代码中定义变量。作者通过示例展示了正确使用`ifdef`、`ifndef`等关键字的方法。

201

201

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?