[Synth 8-4556] 开辟的数组内存空间大小问题

[Synth 8-4556] size of variable 'out_FM_buffer' is too large to handle; the size of the variable is 1634688, the limit is 1000000

问题描述:

开发过程,开辟如下空间,综合报错[Synth 8-4556]

问题解决:

使用的TCL命令如下,修改综合时大小限制

set_param synth.elaboration.rodinMoreOptions "rt::set_parameter var_size_limit 1634688"

[Synth 8-6859] 在不同的always逻辑块中,对同一个reg变量进行了赋值

[Synth 8-6859] multi-driven net on pin group_index[0] with 1st driver pin 'group_index_reg[0]__0/Q'

问题描述:开发过程,运行实现出现错误,追溯到综合阶段发现有众多致命警告[Synth 8-6859]

问题解决:

保持一个寄存器只能在一个always块中被赋值。

[Synth 8-6859] 另外注意可能产生多驱动问题的情况,在使用generate ... for批量例化时,注意输出端口要定义为数组,如下例的mat_flag端口

// 错误写法

wire mat_flag;

genvar ii;

generate

for(ii=0;ii<ch_in_num;ii=ii+1) begin:ch_in_line_buffer

matrix_3x3_in

u_line_buffer(

.clk(clk),

.rst_n(rst_n),

.valid_in(valid_in),

.dout_r_r0d0(buffer_out_x00[ii]),

.dout_r_r0d1(buffer_out_x01[ii]),

.mat_flag(mat_flag) // 输出端口

);

MAC_3x3_mul_ch_in

u_mul_chin(

.clk(clk),

.rst_n(rst_n),

.valid_in(mat_flag),

.X00(buffer_out_x00[ii]),

.X01(buffer_out_x01[ii]),

.output_result_array(result_mul_chout[ii])

);

end

endgenerate// 正确写法

wire mat_flag_lib [ch_in_num-1:0]; // 定义为数组

genvar ii;

generate

for(ii=0;ii<ch_in_num;ii=ii+1) begin:ch_in_line_buffer

matrix_3x3_in

u_line_buffer(

.clk(clk),

.rst_n(rst_n),

.valid_in(valid_in),

.dout_r_r0d0(buffer_out_x00[ii]),

.dout_r_r0d1(buffer_out_x01[ii]),

.mat_flag(mat_flag_lib[ii])

);

MAC_3x3_mul_ch_in

u_mul_chin(

.clk(clk),

.rst_n(rst_n),

.valid_in(mat_flag_lib[ii]),

.X00(buffer_out_x00[ii]),

.X01(buffer_out_x01[ii]),

.output_result_array(result_mul_chout[ii])

);

end

endgenerate

[Place 30-58]和[Place 30-99]

[Place 30-58] IO placement is infeasible. Number of unplaced terminals (387) is greater than number of available sites (328). The following are banks with available pins: IO Group: 2 with : SioStd: LVCMOS18 VCCO = 1.8 Termination: 0 TermDir: Out RangeId: 1 Drv: 12 has only 328 sites available on device, but needs 387 sites.

[Place 30-99] Placer failed with error: 'IO Clock Placer failed'

Please review all ERROR, CRITICAL WARNING, and WARNING messages during placement to understand the cause for failure.问题描述:

开发过程,

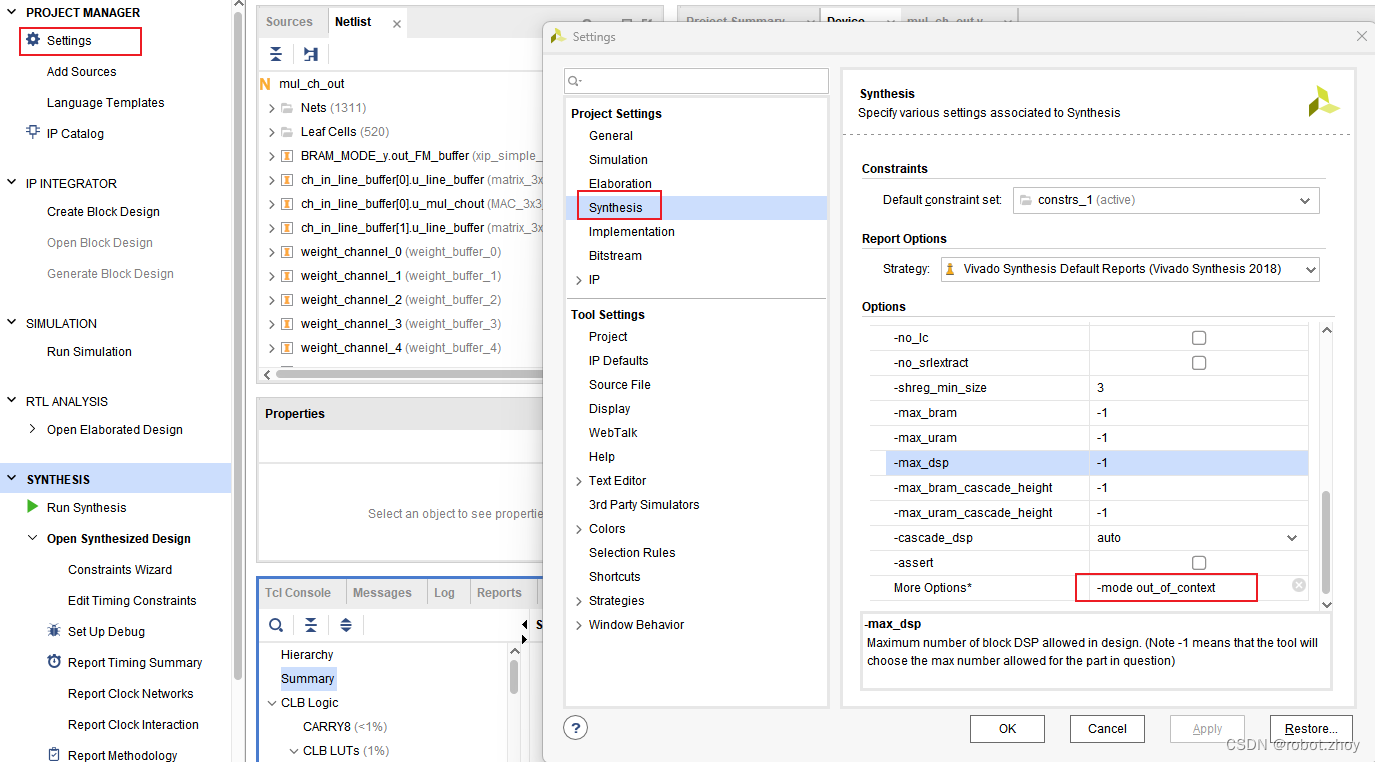

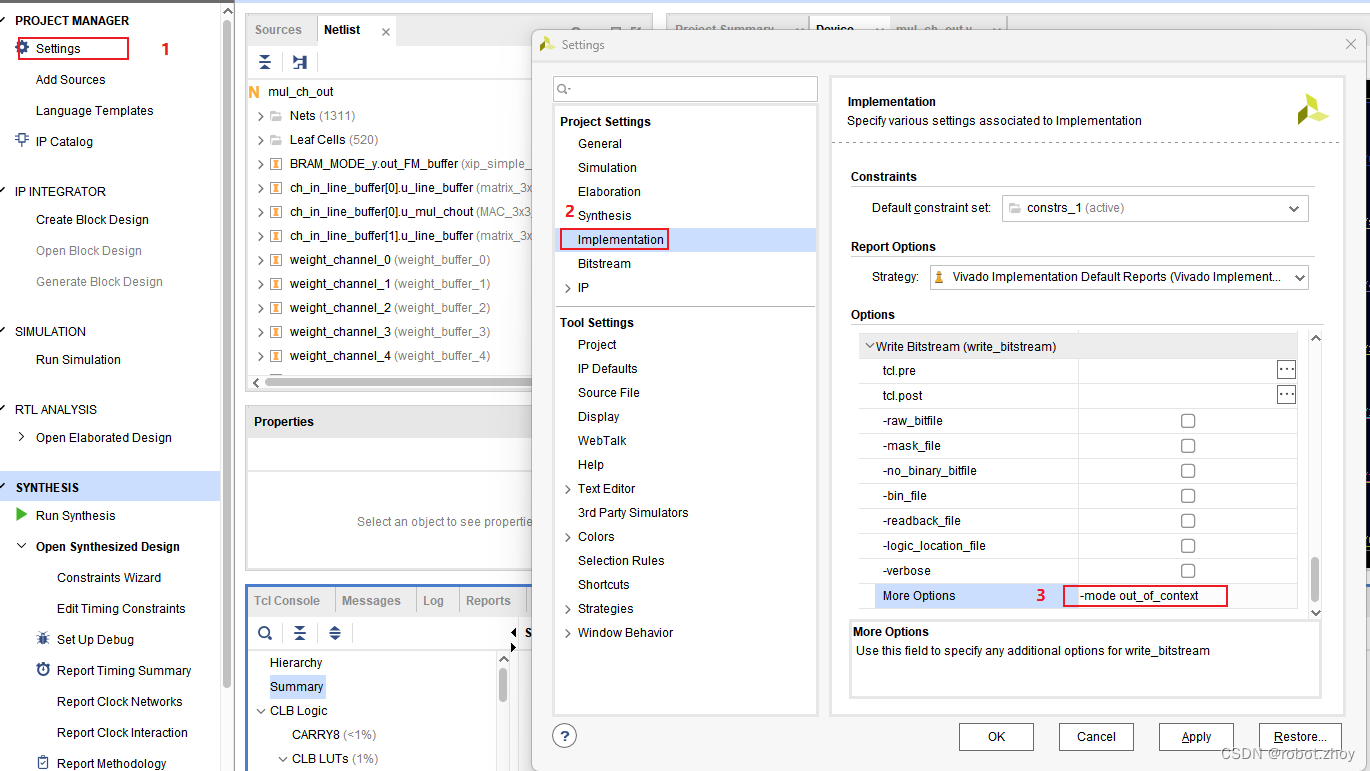

问题解决:

在综合设置中添加-mode out_of_context(在OOC综合方式下,模块可以有自己的约束文件,同时会单独生成该模块对应的DCP文件,且在综合阶段不会插入IBUF或OBUF。)

参考:OOC综合方式

综合-实现后未显示DSP、BRAM资源使用情况

问题描述:

写完verilog代码,明明用了较多DSP和BRAM资源,Report Utilization确没有这两项

问题解决:

RAM资源显示问题:一般Implementation 菜单下的Report Utilization会较准确,或者使用tcl指令,Implementation后 在Tcl Console中使用 report_utilization -hierarchical 指令查询

DSP资源显示问题:一般算法中用到的乘法器可以用Slice单元或DSP块实现,而vivado实现使用DSP的方法一般有(1)让综合器自己推断。(2)例化DSP原语两种方式。未显示,可能是综合器使用了Slice单元。

如果只是乘法使用DSP实现的话,在结果寄存器添加如下语法规则即可:

(*use_dsp = "yes"*) reg [35:0] r_mul_result_0 = 36'd0;

1906

1906

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?