`timescale 1ns/1ns

module width_8to16(

input clk,

input rst_n,

input valid_in,

input [7:0] data_in,

output reg valid_out,

output reg [15:0] data_out

);

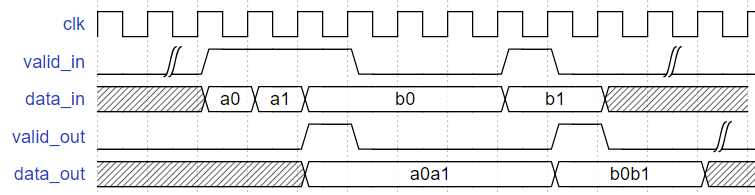

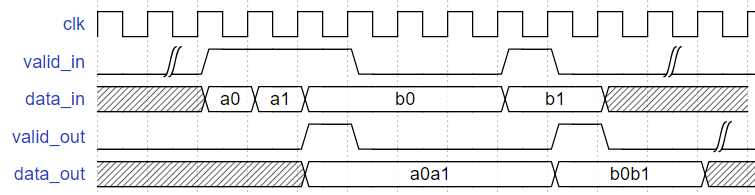

reg [7:0] data_buffer; //用于缓冲每组的第1个数

reg buffer_flag; // 缓冲就位与否标志

// 将每组的第1个数暂存进data_buffer

always @(posedge clk or negedge rst_n ) begin

if(!rst_n)

data_buffer <= 'd0;

else if(valid_in && !buffer_flag)

data_buffer <= data_in;

end

// 描述缓冲状态buffer_flag逻辑

always @(posedge clk or negedge rst_n ) begin

if(!rst_n)

buffer_flag <= 'd0;

else if(valid_in)

buffer_flag <= ~buffer_flag;

end

// 描述输出结果valid_out有效逻辑

always @(posedge clk or negedge rst_n ) begin

if(!rst_n)

valid_out <= 'd0;

else if(valid_in && buffer_flag)

valid_out <= 1'd1;

else

valid_out <= 'd0;

end

// 描述数据转换逻辑

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

data_out <= 'd0;

else if(valid_in && buffer_flag)

data_out <= {data_buffer, data_in};

end

endmodule

6815

6815

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?