AXI-Lite 学习笔记

参考

FPGA:AXI_Lite总线基础2-1]、第二节 AXI总线介绍、ZYNQ PL与PS交互专题_哔哩哔哩_bilibili AXI-Lite总线系列1 - 基础知识_哔哩哔哩_bilibili

AXI4 介绍

AXI4 是ARM公司提出的一种片内总线,描述了主从设备之间的数据传输方式。主要有AXI4_LITE、AXI4_FULL、AXI4_STREAM三种。

- AXI4_LITE:不支持突发传输,一般用于小数据量的IP初始化和嵌入式设备数据传输。

- AXI4_FULL:可称为AXI4,支持突发传输,突发长度为1~256。

- AXI4_STREAM:流数据,丢弃了地址项,用于高速数据传输。

AXI_LITE 基础知识

AXI4 中的主从关系

- 主机发起写请求,然后向从机写入数据;

- 主机发起读请求,然后从从机中读出数据;

- 主从机之间的数据传输都是由主机发起,从机是被动的,可以简单理解为主机是SOC,从机是外设。

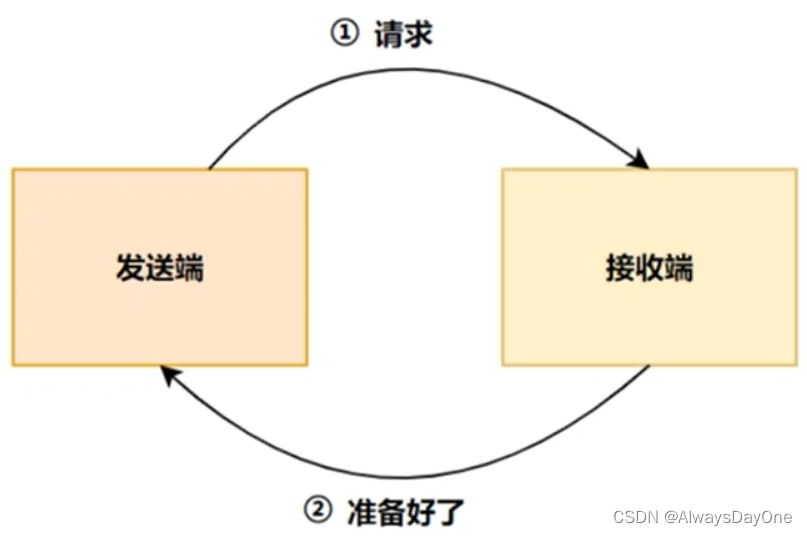

握手机制 (Handshack)

使用VALID和READY信号作为控制信号来传输数据,只有VALID与READY同时为高的时候,才可以正常的发送数据,而通常情况下,VALID信号用来表示什么时候“地址、数据、和控制信号”是有效的,而READY信号则用来表示什么时候从设备准备好采集数据了

- VALID:发送端准备好了数据,开始请求接收端接收

- READY:接收端准备好了,可以接收发送端的数据

- INFOMATION:表示发送端请求所携带的数据,最终将传输到接收端

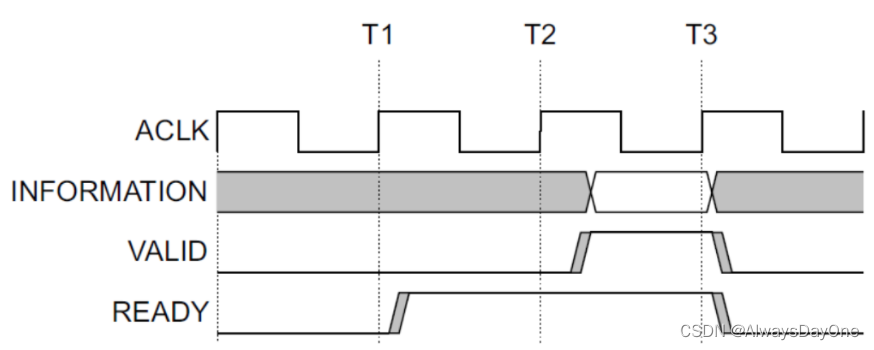

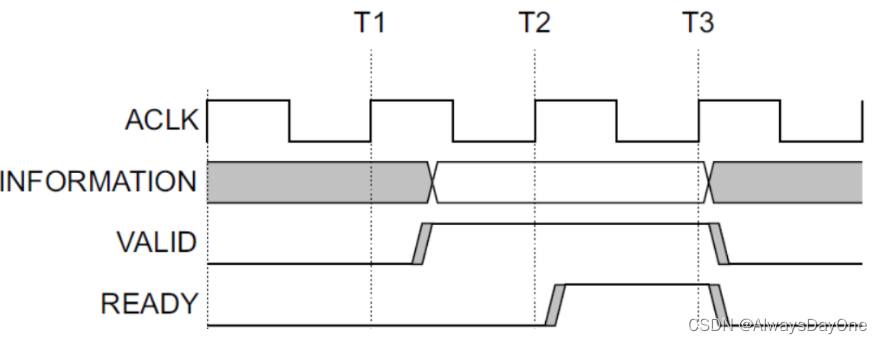

对于这三个信号,会存在以下三种情况:

- READY 信号先于VALID 信号高电平:T2 时刻READY 信号的拉高,代表从设备准备好采样了,但T2 时刻,VALID 未拉高,因此未进行采样,而T3 时刻,VALID 拉高了,完成握手,数据传输。

- VALID 和READY 信号在T2 时刻同时为高电平:数据有效的同时也可以进行采样,在T2 时刻的上升沿,采样到正确数据,握手正确,再往后二者都拉低,数据进行了正确传输。

- READY 信号晚于VALID 信号高电平:表明数据先正确,然后READY拉高表明可以进行采样,T3时刻进行了采样,完成握手,再往后二者信号都拉低,数据传输。

此外,协议规定,“VALID 信号一旦拉高,除非READY 信号拉高接收数据完成,不会主动变低”。

总结:只要主从机之间发生数据传输,就会发生“握手”过程。

Channel 通道

数据传输通过Channel 的概念来实现,Channel 包含握手机制,握手完成(即VALID、READY 信号同时为高)表示一次数据传输。

AXI_LITE 中有五个通道:读的地址、读的数据、写的地址、写的数据、写响应

可以看到特点为:读写分离,读无响应

AXI_LITE 信号组成

AXI_LITE数据传输所需要的信号主要有以下四类:

- Clock,Reset

- ADDRESS

- DATA

- 传输可靠性信号

AXI_LITE 信号端口

全局信号

读地址通道

- 地址的位宽一般根据存储的大小制定

读数据通道

- AXI_LITE 支持RDATA 位宽32bit or 64bit

写地址通道

- 地址的位宽一般根据存储的大小制定

写数据通道

- AXI_LITE 支持WDATA 位宽32bit or 64bit

- WSTRB表示写入的数据掩码,如下WSTRB为0011表示byte0 byte1 为有效的字节,byte3 byte2 为无效的字节,无效字节将不会写入。

写响应通道

BRESP 和 RRESP 信号

| BRESP[1:0]RRESP[1:0] | Response | |

|---|---|---|

| 0b00 | OKAY | |

| 0b01 | EXOKAY | AXI_LITE 不支持 |

| 0b10 | SLVERR | Slave Error |

| 0b11 | DECERR |

AXI_LITE 读写过程

读操作

- 首先,读地址通道 (Read Address Channel) 从主设备 (Master) 发送到从设备 (Slave),以便设置地址和部分控制信号。

- 然后,此地址的数据通过读数据通道 (Read data channel) 从从设备发送到主设备。

两个操作是有前后顺序的。

注意:而AXI4-Lite是不支持突发(burst)的,一次交互只有一次数据传输,上图是AXI_FULL的突发传输。

写操作

- 写地址通道:写地址通道 (Write Address Channel) 从主设备发送到从设备,以便设置地址和部分控制信号。

- 写数据通道:此地址的数据通过写数据通道 (Write data channel) 从主设备发射到从设备。

- 写响应通道:写入响应通过写响应通道 (Write Response Channel) 从从设备发送到主设备,以指示传输是否成功

注意:而AXI4-Lite是不支持突发(burst)的,一次交互只有一次数据传输,上图是AXI_FULL的突发传输。

三个操作是有三种时序情况的,主要是写地址和写数据的先后顺序:

- 写地址比写数据先发送

- 写地址比写数据晚发送

- 写地址和写数据同时发送

一般常见第3种顺序模式

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?