Retimer拓扑结构

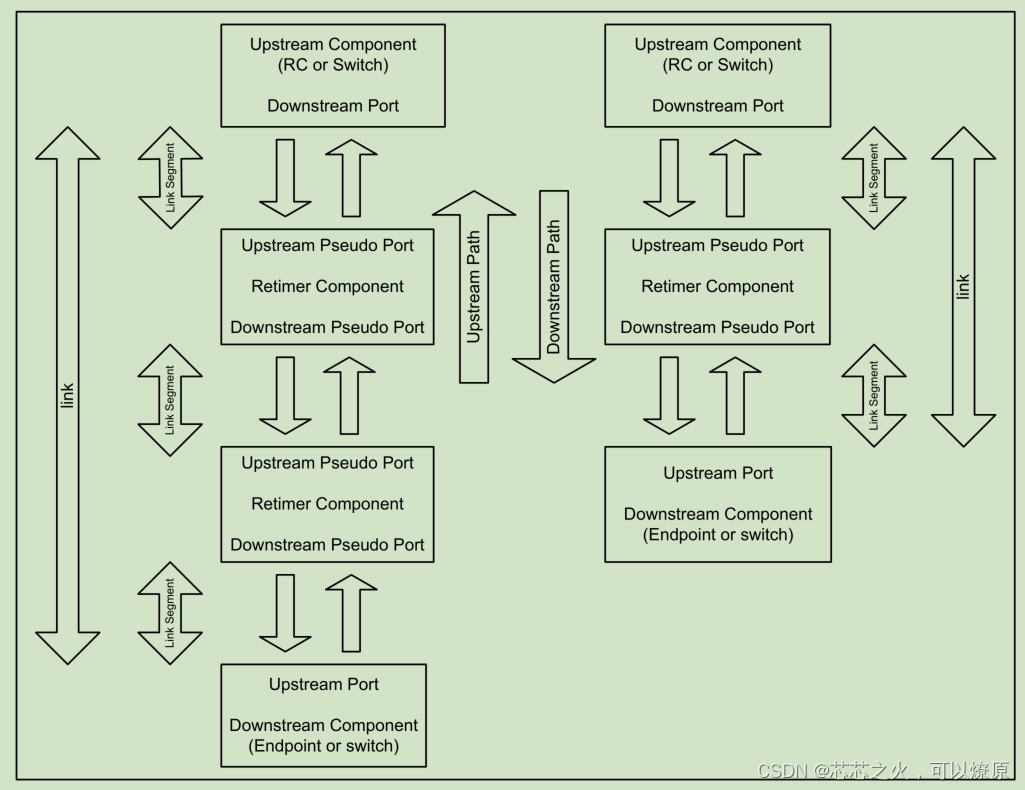

在PCIe系统当中,Retimer支持的拓扑结构如下所示:

在一条PCIe链路上,DSP和USP之间可能会有一个或者两个Retimer,对于每一个Retimer,它都有两个伪端口,可以实现动态的切换downstream和upstream方向。在Forwarding模式下,每个Retimer都有一个upstream path和一个downstream path,两个伪端口必须工作在同样的速率下。

Retimer工作模式

Forwarding mode

Symbols,EIOS,EIEOS可以在上游通道和下游通道上进行转发。

Execution mode

在该工作模式下,上游伪端口作为一个USP,下游伪端口作为一个DSP,该模式运用场景如下:

1 Polling.Compliance。

2 Equalization的Phase 2和Phase 3。

3 Slave Loopback(可选)。

Retimer重要变量

在完成基本复位之后或者当Retimer在所有的lane上收到连续的两个Link Number和Lane Number为PAD的TS2后(从第一条lane的第二个TS2的最后一个symbol到最后一条lane的第二个TS2的最后一个symbol大概1us的时间窗口之内)。以下变量需要设置成固定的数值:

RT_port_orientation = undefined

RT_captured_lane_number = PAD

RT_captured_link_number = PAD

RT_G3_EQ_complete = 0b

RT_G4_EQ_complete = 0b

RT_G5_EQ_complete = 0b

RT_LinkUp = 0b

RT_next_data_rate = 2.5 GT/s

RT_error_data_rate = 2.5 GT/s

参考书籍

1 PCI Express® Base Specification Revision 5.0 Version 1.0

本文详细介绍了PCIe系统中Retimer的拓扑配置,包括可能存在的多个Retimer及其伪端口在Forwarding模式下的功能,以及Execution模式的应用场景。重点讨论了Retimer的重要变量设置,如在初始状态下的固定值。

本文详细介绍了PCIe系统中Retimer的拓扑配置,包括可能存在的多个Retimer及其伪端口在Forwarding模式下的功能,以及Execution模式的应用场景。重点讨论了Retimer的重要变量设置,如在初始状态下的固定值。

102

102

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?