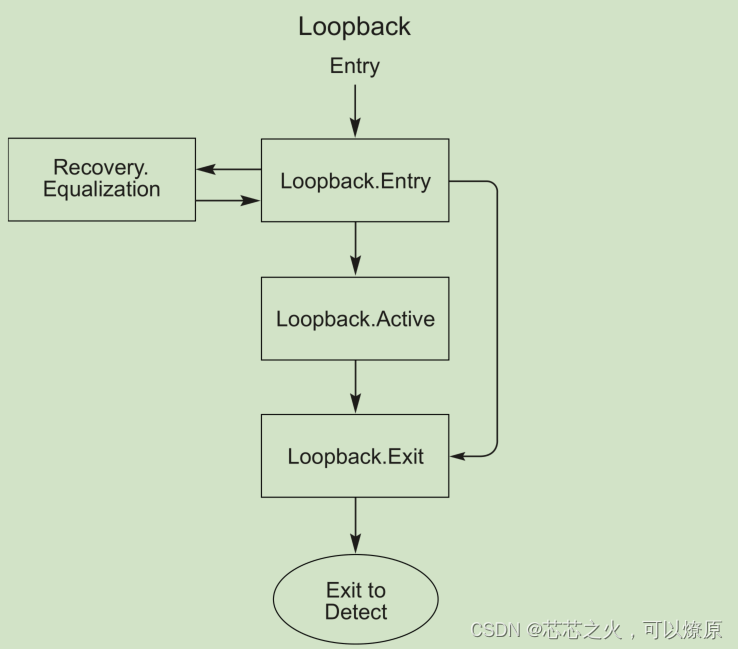

1.1 Loopback状态转换图

Loopback状态转换图如下所示:

1.2 Loopback解析

Loopback状态的作用是测试和故障隔离,SPEC中只指定Loopback的进入和退出,至于一些其他的细节取决于设计的实现。Loopback既可以在单独的Lane上进行,也可以在配置好的Link上进行。Loopback Master指的是发起Loopback请求的组件,Loopback Slave指的是回传数据的组件。

1.2.1 Loopback.Entry

1 LinkUp=0b。

2 在该子状态下,Rx收到的TS1/2中的Link Number和Lane Number都会被忽略。

3 Loopback Master的要求如下:

(1) 如果Loopback.Entry是从Configuration.Linkwidth.Start进入的,确定Master支持的最高速率并且在任意的Lane上Rx连续接收的两个TS1中解析的速率也是该最高速率,这个时候Master会进入Loopback.Entry。如果当前的速率不是双方支持的最高速率,则:

- Tx发送16个连续的带有Loopback bit=1的TS1并且随后跟着一个EIOS,然后进入电气空闲状态1ms,在处于电气空闲状态的期间,将速率切换到双方支持的最高速率。

- 如果双方支持的最高速率为2.5GT/s,Slave的Tx De-emphasis是通过设置TS1中的Selectable De-emphasis bit数值实现的。(1b = -3.5 dB, 0b = -6 dB)

- 如果双方支持的最高速率为5.0GT/s及以上,Master可以根据实现方式设置自己的Tx不管它传给Slave的Tx设置是什么。

注:如果进入Loopback是在LinkUp=1之后,有可能一个Port是从Recovery进入Loopback,另一个Port是从Configuration进入Loopback。如果发生这种情况,结果是不确定的,所以SPEC建议避免这种情况的发生。

(2)Tx发送Loopback bit=1的TS1。

- 如果Loopback.Entry是从Recovery.Equalization状态进入的,则发送的TS1的EC需要设置成00b。

- 当处于Loopback.Entry状态时,Master也可以将TS1中的Compliance Receive bit置1,包括在速率改变之前发送的数据。如果在Loopback.Entry状态下将TS1中的Compliance Receive bit设置成1,则不允许再次在此状态下将其设置成0。

(3)如果Tx发送的TS1的Compliance Receive bit置1,则在2ms后进入Loopback.Active。

(4)如果当前的速率切到了32GT/s并且在任意的Lane上发送了16个连续的带有Enhanced Link Behavior Control bits=01b的TS1,则进入 Recovery.Equalization状态。

- perform_equalization_for_loopback变量需要设置成1。

(5)如果Loopback.Entry是从Recovery.Equalization进入并且被测试的Lane上收到了连续两个带有Loopback bit=1的TS1,则进入Loopback.Active状态。

(6)如果Tx发送的TS1的Compliance Receive bit为0并且特定实现的Lanes上收到了连续两个带有Loopback bit=1的TS1,则进入Loopback.Active状态。

注:如果速率改变了并且32.0GT/s的EQ没有做,在进入Loopback.Active状态之前,Master需要考虑Slave处于电气空闲状态的时间并且需要发送足够多的TS1给Slave去实现Symbol Lock或者Block Alignment。

(7)在小于100ms特定实现的超时后,则进入Loopback.Exit状态。

4 Loopback Slave的要求如下:

(1)如果Loopback.Entry是从Configuration.Linkwidth.Start进入的,确定Slave支持的最高速率并且从连续接收的两个TS1中解析的速率指示Slave进入该状态,如果当前的速率不是双方支持的最高速率,则:

- Tx发送一个EIOS,然后进入电气空闲状态2ms。在电气空闲状态期间,将速率切换到双方支持的最高速率。

- 如果此时是Full Swing模式并且双方最高支持的速率为5.0GT/s,将Tx发送的指示Slave进入该状态的TS1的Selectable De-emphasis bit数值,用来设置Tx的De-emphasis。(Selectable De-emphasis bit为1代表-3.5dB;Selectable De-emphasis bit为0代表-6dB)

- 如果双方最高支持的速率为8.0GT/s及以上,将Tx发送的指示Slave进入该状态的TS1的Preset数值,用来设置Tx的Preset。如果双方最高支持的速率为8.0GT/s及以上但是是标准的TS1指示Slave进入该状态,则Slave允许使用默认的Tx参数设置。

(2)如果Loopback.Entry是从Configuration.Linkwidth.Start进入的,并且双方最高支持的速率为32GT/s,并且Tx发送的指示Slave进入该状态的TS1的Enhanced Link Behavior Control bits=01b,则进入Recovery.Equalization状态:

- perform_equalization_for_loopback变量设置成1b。

- 如果Tx发送的指示Slave进入该状态的TS1的Transmit Modified Compliance Pattern in Loopback bit=1b,则 transmit_modified_compliance_pattern_in_loopback变量设置成1b。

- 当Recovery.Equalization是从Loopback.Entry进入的时候,在Configuration.Linkwidth.Start状态下接收到两个连续的带有Enhanced Link Behavior Control bits=01b的TS1的Lane将作为Loopback和Recovery.Equalization的测试通道。

- Slave必须根据特定的实现方式选择一个有效的Link Number。

(3)如果Tx发送的指示Slave进入该状态的TS1的Compliance Receive bit=1,则进入Loopback.Active状态。

- Slave不需要在任何边界上转换到传输回环数据状态,它可以截断任何的OS。

(4)如果上述三个条件都不满足,则Slave的Tx会发送Link Number和Lane Number为PAD的TS1。

- 如果Loopback.Entry是从Recovery.Equalization进入,则发送的TS1的EC字段需要设置成00b。

- 如果Loopback.Entry是从Recovery.Equalization进入并且测试的Lane上Rx收到了两个连续的带有Loopback bit=1b的TS1,则进入Loopback.Active。

- 如果速率为2.5GT/s或者5.0GT/s并且所有的Lane上都获得了Symbol Lock,则进入Loopback.Active。

- 如果速率为8.0GT/s及以上并且在所有的Lane上Rx收到了两个连续的TS1,则进入Loopback.Active。

- 当使用8b/10b编码方式的时候,Slave的Tx需要在一个Symbol的边界上转换到发送回环数据状态,但是可以截断任何的OS;当使用128b/130b编码方式的时候,Slave的Tx不需要在一个边界上转换到发送回环数据状态,同时可以截断任何的OS。

1.2.2 Loopback.Active

1 Master必须发送有效的编码数据。Master不能发送EIOS除非退出Loopback状态。

2 如果transmit_modified_compliance_pattern_in_loopback设置为1,从Recovery.Equalization进入Loopback.Active的Slave必须在所有的Lane上除开测试的Lane(Lane under test)上发送Modified Compliance Pattern,否则这些Lane必须进入电气空闲状态。测试的Lane(Lane under test)需要符合下面Loopback Slave的行为。

3 Slave被要求去将接收到的数据以相应的Polarity(Polling状态下决定)重新发送出去,与此同时,会进行相应的时钟补偿:

(1)SKP可以在独立的Lane上实现增加或者减少,并不需要在所有的Lane上同步进行增加或者减少。

(2)Slave对接收到的编码数据不能进行更改(除开Polling状态下决定的Polarity Inversion),即使Slave收到的数据是无效的编码数据也不允许进行修改。

4 如果满足以下的其中一个条件,Slave的下一个状态是Loopback.Exit。

(1)如果PCIe上层指示进入Loopback.Exit或者在任意的Lane上收到了连续的4个EIOS。

(2)可选的:如果当前的速率为2.5GT/s并且收到了一个EIOS或者在任意的Lane上检测或推测出电气空闲状态。

(3)Slave必须可以在Slave接收EIOS的1ms时间内任意的Lane上检测到电气空闲状态。

5 如果PCIe上层指示进入Loopback.Exit,Master的下一个状态是Loopback.Exit。

1.2.3 Loopback.Exit

1 对于仅仅支持2.5GT/s的Port,Loopback Master发送一个EIOS;对于支持速率大于2.5GT/s的Port,Loopback Master发送8个连续的EIOS;并且所有的Lanes进入电气空闲状态2ms。

(1)在发送完最后一个EIOS的时候,Loopback Master所有的Lanes必须在“TX-IDLE-SET-TO-IDLE”时间内转换到一个有效的电气空闲状态。

2 Loopback Slave所有的Lanes必须进入电气空闲状态2ms。

(1)在进入电气空闲状态之前,Loopback Slave必须将收到的所有数据进行回传。这个可以确保当Loopback Master看到EIOS时,将Loopback行为结束的标志传递给相应的发送逻辑和比较逻辑。

3 Loopback Master和Loopback Slave的下一个状态是Detect。

1.3 参考书籍

1 PCI Express® Base Specification Revision 5.0 Version 1.0

2 PCI Express Technology Comprehensive Guide to Generations 1.x, 2.x, 3.0

102

102

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?