标题:A Novel SiC Trench MOSFET with Improved Short-circuit Capability through an Integrated JFET Region

阅读日期:2023.7.16

研究了什么

该文章研究了一种新型SiC沟槽栅MOSFET,其具有集成JFET区域(IJ-TMOS),通过减少饱和区的漏极电流来改善其短路容限能力。该提出的结构将峰值短路电流密度降低了23.2%,并将600 V直流母线电压下的短路耐受时间从9.5微秒提高到13微秒(提高了36.8%)(针对1200 V级电压水平设计)。

文章创新点

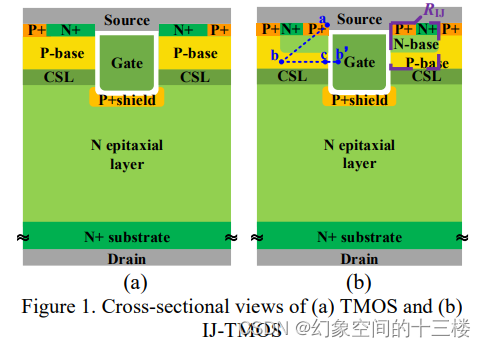

·提出了一种新型SiC沟槽栅MOSFET,其具有集成JFET区域(IJ-TMOS),通过减少饱和区的漏极电流来改善其短路容限能力。

·集成的JFET由N+源区中的额外P+源区和嵌入P型基区的N型基区组成。

·提出的结构将峰值短路电流密度降低了23.2%,并将600 V直流母线电压下的短路耐受时间从9.5微秒提高到13微秒(提高了36.8%)(针对1200 V级电压水平设计)。

文章的研究方法

该文章的研究方法是使用Sentaurus TCAD模拟来获得所提出的IJ-TMOS结构的电特性。与传统的沟槽MOSFET(TMOS)进行比较,验证了IJ-TMOS的优越短路性能。

文章得出的结论

·提出的新型SiC沟槽栅MOSFET,其具有集成JFET区域(IJ-TMOS),通过减少饱和区的漏极电流来改善其短路容限能力。

·集成的JFET区域将峰值短路电流密度降低了23.2%,并将600 V直流母线电压下的短路耐受时间从9.5微秒提高到13微秒(提高了36.8%)(针对1200 V级电压水平设计)。

·提出的IJ-TMOS结构与传统的TMOS相比具有更低的饱和漏极电流密度(Jdsat)和略微降低的阈值电压(Vth)。

·引入的JFET区域不会影响短路条件下的温度分布。

研究提出了一种新型SiC沟槽栅MOSFET,名为IJ-TMOS,通过集成JFET区域增强了短路承受能力。利用SentaurusTCAD模拟,IJ-TMOS显示出比传统TMOS更低的饱和漏极电流和更高的短路耐受时间,提升了设备的安全性和效率。

研究提出了一种新型SiC沟槽栅MOSFET,名为IJ-TMOS,通过集成JFET区域增强了短路承受能力。利用SentaurusTCAD模拟,IJ-TMOS显示出比传统TMOS更低的饱和漏极电流和更高的短路耐受时间,提升了设备的安全性和效率。

2636

2636

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?