自从学习FPGA以来,按照惯例,都是使用VIVADO调用ModelSim来仿真,这样可以在仿真的同时继续修改代码,并且根据同组的人说,ModelSim仿真貌似还快一点(虽然用ModelSim+ i9-9900k,有时候仿真跑一天也跑不完(๑′ᴗ‵๑)❤)

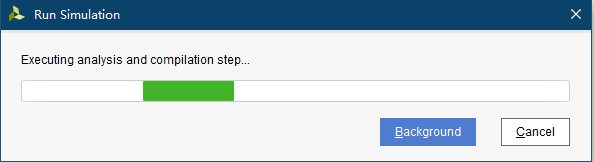

但是有调用,就有调用失败的时候,有的时候会报错,那就很简单了,根据报错进去看看log文件,按照log文件修改就好了,但是有的时候一直卡在下面这里,绿色小条条一直来回转悠,错也不报:

断断续续这种问题遇到小半年了,有时候不知道怎么捅咕捅咕就好了。最近下定决心整明白它,下次自己在遇到问题还能回来看看。

下面给一点排查建议,同时给出解释,建议慢慢看,学习心急不得

最开始的排查:打开最下面的TCL console窗口

看看跑到哪一步了,如果是显示如下图所示:

modelsim >

那证明你确实遇到了问题,否则建议慢慢等待,根据你实现的复杂程度,调用也会有快慢之分。

如果确实遇到问题

第一个建议:右键run simulation,选择reset behavior simulation(/斜眼笑)

解释:有的时候我会在VIVADO simulater和ModelSim中切换,切换中很容易遇到不能调用ModelSim这种情况,这时reset一下就可以了。建议遇到不能调用第一时间reset,反正不亏,没准就可以解决了呢

第二个建议:一个一个注释掉自己调用的模块、保存、run simulation。

如果注释掉某一个模块后ModelSim调用成功了,恭喜你!!!那就证明是这个模块的问题,可以往下进行了。

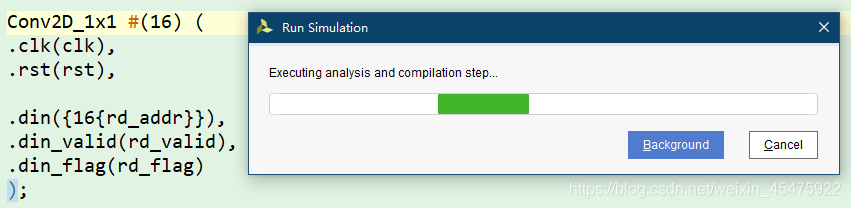

第三个建议:看看自己例化模块的时候是不是没写模块名称?

解释:有的时候你例化模块不写例化名字,他也不会报错,而是给你个warning,但是我写代码习惯不好,每次都有几百个warning,有一次我一个一个查才看到这个报警,算是帮大家排雷了。(我经常犯这个错误,如下图捂脸(/ω\) )

第四个建议:看看自己调用的模块有没有语法错误

解释:有的时候,你顶层模块调用的模块如果有语法错误等(红色小波浪线),他在run simulation的时候是不会给你报出来的,而是卡在上面这个图的位置一直等待,这个错误也很常见。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?