1. 设计特性

1.1 面向可综合设计的主要优化

1.1.1 过程语句块新特性

always语句块被细分为了:

- 组合逻辑语句块always_comb

- always_comb可以自动嵌入敏感列表。

- always_comb可以禁止共享变量,即赋值左侧的变量无法被另一个过程块所赋值。

- 软件工具会检查该过程块,如果其所表示的不是组合逻辑,那么会发出警告。

- always_comb在仿真0时刻会自动触发一次,无论在0时刻是否有敏感信号列表中的信号发生变化。

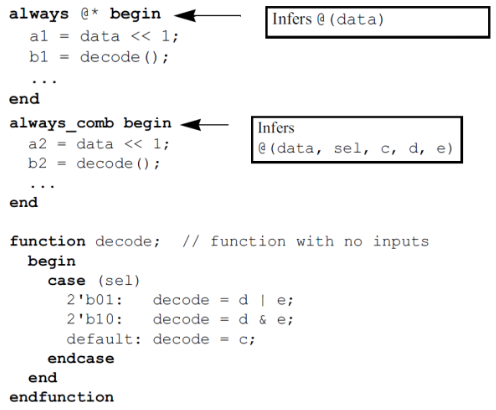

- 与Verilog @* 的敏感列表声明方式不同处

- @* 不要求可综合的建模要求,但always_comb则会限制其他过程块对同一变量进行赋值。

- @* 的敏感列表可能不完全,@* 只会将该函数的形式参数自动声明到敏感列表,而不会将该函数展开。

- always_comb则将被调用函数中可能参与运算的其它信号也声明到敏感列表中。

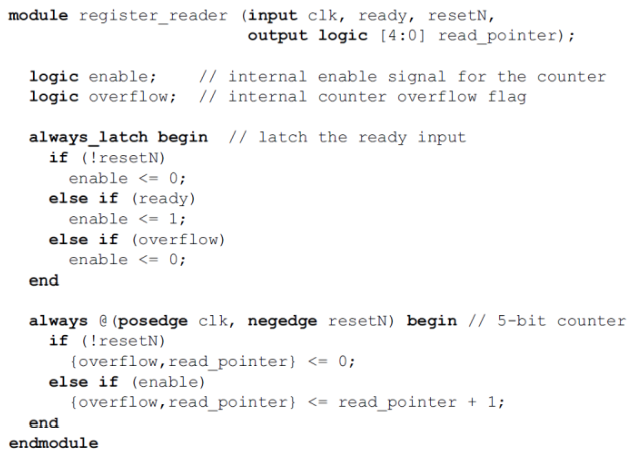

- 锁存逻辑语句块always_latch

- always latch表示锁存逻辑,且自动插入敏感列表。

- EDA工具会检查always_latch过程块是否真正实现了锁存逻辑。

- 时序逻辑语句块always_ff

- always_ff用来表示时序逻辑。

- 敏感列表必须指明posedge或者negedge(综合要求),从而使得EDA工具实现同步或者异步的复位逻辑。

- EDA工具也会验明always_ff过程块语句是否实现了时序逻辑。

1.1.2 赋值操作符

- SV可以通过’0,'1,'z和′x来分别填充0,1,z和x。

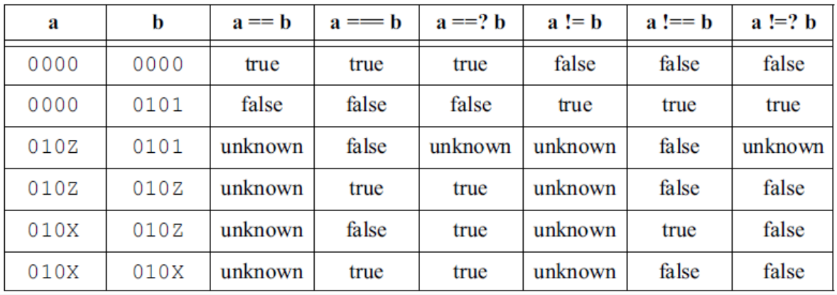

- SV在比较数据时,可以通过== ?来进行通配比较。在比较操作符的右侧操作数,如果在某些位置有X或者Z,那么它表示的是在该位置上会与左侧操作数的相同位置的任何值相匹配。

- SV添加了inside操作符,用来检查数值是否在一系列值的集合当中。

1.1.3 增强的case与语句

仿真和综合可以会将case语句做不同的翻译。Verilog定义case语句在执行时按照优先级,而综合编译器则会优化case语句中多余的逻辑。为了保持仿真与综合的一致性,SV提供了unique和priority的声明,结合case,casex和casez来进一步实现case对应的硬件电路。

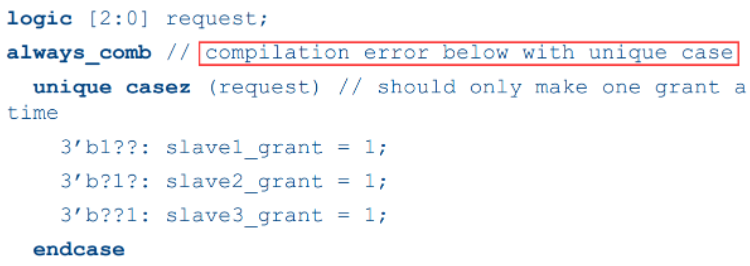

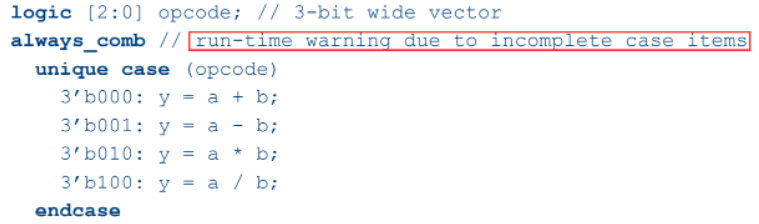

- unique case

- unique case要求每次case选择必须只能满足一条case选项

- unique case不能有重叠的选项,即多个满足条件的选项

- unique case可以并行执行,并且case选项必须完备

- priority case

- priority case则表示必须至少有一个case选项满足要求。如果有多个case选项满足时,第一个满足的分支将会被执行

- priority case的逻辑同if…else的逻辑一致。

2. 接口

SV添加了新的抽象端口类型interface。interface允许多个信号被整合到一起用来表示一个单一的抽象端口。多个模块因此可以使用同一个interface,继而避免分散的多个端口信号连接。

2.1 接口的内容

- 接口不单单可以包含变量或者线网,它还可以封装模块之间通信的协议。

- 接口中可以嵌入与协议有关的断言检查、功能覆盖率收集等模块。

- 接口不同于模块(module)的地方在于,接口不允许包含设计层次,即接口无法例化module,但是接口可以例化接口。

- 接口中可以进一步声明modport来约束不同模块连接时的信号方向。

2.2 接口的声明

- 接口的定义同模块定义类似。

- 接口也可以有端口,例如外部接入的时钟或者复位信号。

- 接口内部可以声明所有的变量或者线网类型。

2.3 接口的例化

- 接口的例化方式同模块例化一致。

- 模块的端口如果声明为input、output或者inout,那么在例化时可以不连接。

- 模块的端口如果声明为interface,那么在例化时则必须连接到一个接口实例,或者另外一个接口端口。

- 如果一个模块拥有一个接口类型端口,那么要索引该接口中的信号,需要通过以下方式进行:

<port_name>.<internal_interface_signal_name>

always @(posedge bus.clock , negedge bus.resetN)

2.4 modport

- 接口中的变量或者线网信号,对于连接到该接口的不同模块则可能具备这不同的连接方向。接口引入了modport来作为module port的缩写,表示不同的模块看到同一组信号时的视角(连接方向)。

- 在接口中声明modport,需要指明modport中各个信号的方向。

- 当一个模块在例化时,可以选择连接到interface端口中具体的某一个modport。这种方式可以降低方向连接错误的可能,进而避免信号多驱动的情况。

3. 问答题

1.结构体和接口之间的联系和差别有哪些地方?

答:

同:①均可以声明变量或线网类型;②结构体同样可以集合一些变量

异:结构体中不能指定信号方向,接口中用modport来约束不同模块连接时的信号方向。

2.模块和接口之间的相近的地方有哪些?又有哪些差别?

答:

同:①接口的定义同模块定义类似;②接口的例化方式同模块例化一致;③均可以声明变量或线网类型。

异:①接口不同于模块(module)的地方在于,接口不允许包含设计层次,即接口无法例化module,但是接口可以例化接口。②接口中可以进一步声明modport来约束不同模块连接时的信号方向。③接口不单单可以包含变量或者线网,它还可以封装模块之间通信的协议。④接口中还可以嵌入与协议有关的断言检查、功能覆盖率收集等模块。

3.将DUT, Interface,TB在顶层连接起来时,要完成哪些步骤?

答:①声明变量;②例化Interface,TB,DUT;③将TB,DUT与Interface连接;

760

760

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?