相关阅读

静态时序分析![]() https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12567571.html?spm=1001.2014.3001.5482

静态时序分析有两种模式:PBA(Path Based Analysis)和GBA(Graph Based Analysis),PBA是基于路径的分析模式而GBA则是基于图的分析模式。在Design Compiler中,时序分析是使用GBA模式;而在PrimeTime中,既可以使用默认的GBA模式也可以使用PBA模式进行时序分析。下面将详细讨论这两种模式的区别与联系。

时序路径和时序弧

首先我们需要知道一条时序路径是由时序弧组成的,组成时序路径的时序弧分为单元内部时序弧(Cell Arc)和线网时序弧(Net Arc)两种(需要注意的是,不是所有时序弧都是是时序路径的一部分,比如一个触发器时钟引脚到该触发器数据输入引脚的时序检查时序弧)。Cell Arc指的是从单元的一个输入引脚到一个输出引脚的时序弧,而Net Arc指的是单元之间的互连时序弧,下面将举例说明。

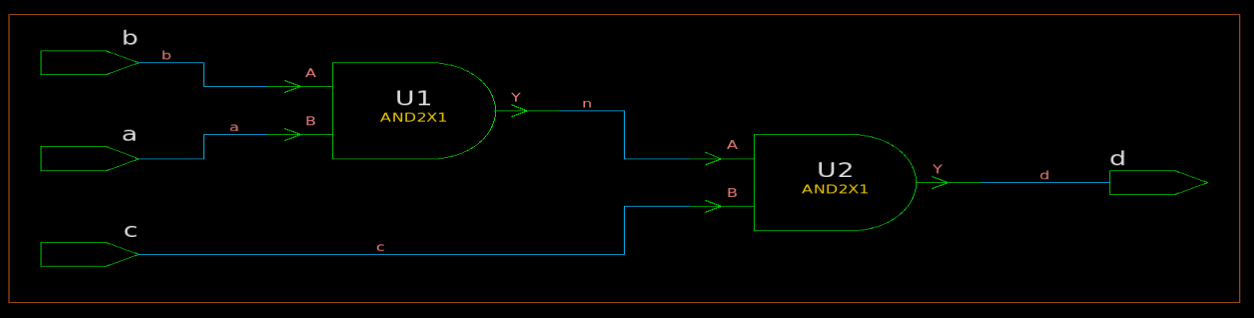

图1 一个简单的例子

图1是一个简单的例子,其中有两个标准单元两输入与门U1和U2。图中一共存在九条时序弧,分别为:输入端口b到U1的输入引脚A的Net Arc、输入端口a到U1的输入引脚B的Net Arc、U1的输入引脚A到U1的输出引脚Y的Cell Arc、U1的输入引脚B到U1的输出引脚Y的Cell Arc、U1的输出引脚Y到U2的输入引脚A的Net Arc、输入端口c到U2的输入引脚B的Net Arc、U2的输入引脚A到U2的输出引脚Y的Cell Arc、U2的输入引脚B到U2的输出引脚Y的Cell Arc、U2的输出引脚Y到输出端口d的Net Arc。

时序路径是由上面的九条时序弧组成的,时序路径的起点一般是输入端口或寄存器引脚,时序弧的终点一般是输出端口或寄存器输入引脚。因此图1中存在三条时序路径,分别为:

- 输入端口b到输出端口d的时序路径,它由输入端口b到U1的输入引脚A的Net Arc、U1的输入引脚A到U1的输出引脚Y的Cell Arc、U1的输出引脚Y到U2的输入引脚A的Net Arc、U2的输入引脚A到U2的输出引脚Y的Cell Arc和U2的输出引脚Y到输出端口d的Net Arc这五条时序弧组成。

- 输入端口a到输出端口d的时序路径,它由输入端口a到U1的输入引脚A的Net Arc、U1的输入引脚A到U1的输出引脚Y的Cell Arc、U1的输出引脚Y到U2的输入引脚A的Net Arc、U2的输入引脚A到U2的输出引脚Y的Cell Arc和U2的输出引脚Y到输出端口d的Net Arc这五条时序弧组成。

- 输入端口c到输出端口d的时序路径,它由输入端口c到U2的输入引脚B的Net Arc、U2的输入引脚B到U2的输出引脚Y的Cell Arc和U2的输出引脚Y到输出端口d的Net Arc这三条时序弧组成。

GBA模式和PBA模式决定了在时序分析时,每条时序路径是半独立地进行分析还是完全独立地进行分析,下面我们首先说明时序路径大致是如何分析的。

用第一条时序路径举例,在Design Compiler进行时序分析时,首先会在输入端口b给出一个理想的上升沿和理想的下降沿(它们是默认的),并将这个翻转沿着时序路径传播,在传播过程中,不在路径中的单元的其他输入引脚需要取一组特定的值以使翻转传播(对于非单调的时序弧,需要取更多组特定的值,因为其在不同情况下有多种单调性),例如对于与门U1,其输入引脚B在进行分析时需要取1;对于与门U2,其输入引脚B在进行分析时也需要取1。传播过程中,要注意各单元时序弧的单调性(见上一章静态时序分析:时序弧以及其时序敏感(单调性)-CSDN博客)由于U1/U2是正单调的,输入端口的上升\下降沿会导致输出的上升/下降沿,因此这条时序路径的翻转情况可能是两种:输入端口b上升沿,一路沿时序路径传播导致输出端口d上升沿;输入端口b下降沿,一路沿时序路径传播导致输出端口d下降沿。注意,这个取值并不一定会真实能取到(即不考虑逻辑),只是为了分析时序路径,例如图2所示的情况。

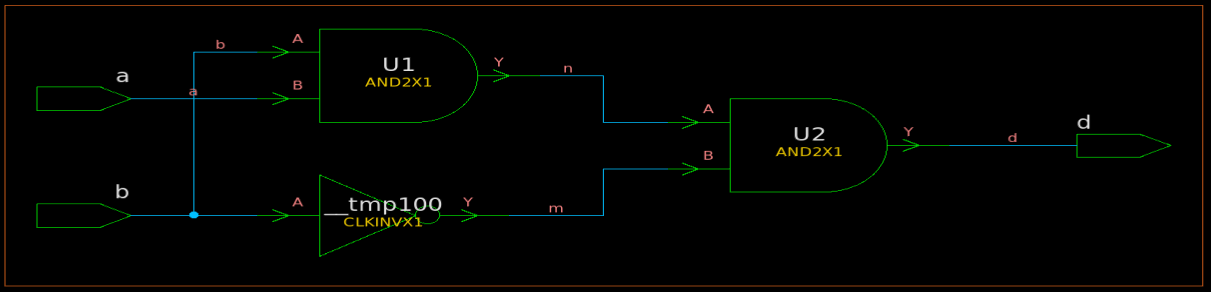

图2 一个愚蠢的例子

在图2中分析从输入端口a到输出端口d的时序路径时,U1和U2的B端口根本不可能同时取1,甚至可以发现输出d恒为0(d=abb'),但是Design Compiler依然会傻傻地将输入端口a的上升/下降沿传播至输出端口d并进行时序分析(在这里,我们假设Design Compiler不会对此进行逻辑优化)。

PBA模式

在使用PBA模式分析图1中的第一条时序路径时,假设输入端口b给出理想上升沿(转换时间为0),上升沿翻转沿线网b传播至U1的输入引脚A,此时延迟为0(假设没有线网延迟),转换时间为0(假设没有转换时间衰减)。Design Compiler根据单元库中的U1器件的非线性延迟模型(NLDM)查表得出U1的单元延迟(从输入引脚A到输出引脚Y,假设为0.5ns)和输出引脚Y的转换时间(假设为0.1ns),接着上升沿翻转从U1的输出引脚Y传播至U2的输入引脚A,此时延迟为0.5ns,翻转时间为0.1ns,Design Compiler根据单元库中的U2器件的非线性延迟模型(NLDM)查表得出U2的单元延迟(从输入引脚A到输出引脚Y,假设为0.4ns)和输出引脚Y的转换时间(假设为0.05ns),最终翻转从U2的输出引脚Y传播至输出端口d。因此这条时序路径的延迟为0.5+0.4=0.9ns,而输出的转换时间为0.05ns。对于输入a是下降沿的情况,也是如此分析。我们可以注意到,第一条时序路径的分析是和其他时序路径无关的,这就是PBA模式的特点。

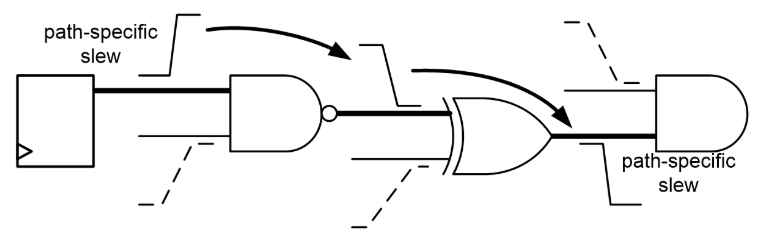

图3展示了上面描述的PBA模式中转换时间的计算过程。

图3 PBA模式下转换时间的计算过程

GBA模式

在使用GBA模式分析图1中的第一条时序路径时,大部分过程与PBA模式是一样的,但是不同的是,引脚Y的转换时间不只取决于U1的输入引脚A,而是与输入引脚B也有关。假设进行的是最大延迟分析(一般情况下,如果不开启on_chip_variation,这指的是建立时间检查),Design Compiler会选择引脚A和引脚B导致的最慢的转换时间作为Y引脚的转换时间,即Y引脚的上升翻转时间是A引脚的上升沿导致的Y引脚的上升翻转时间和B引脚的上升沿导致的Y引脚的上升翻转时间中最大的那个。对于输入端口b的下降沿在传播时也是如此分析,即Y引脚的下降翻转时间是A引脚的下降沿导致的Y引脚的下降翻转时间和B引脚的下降沿导致的Y引脚的下降翻转时间中最慢的那个。B引脚的上升沿和下降沿相关的数据是在输入端口a到输出端口d的时序路径即第二条时序路径的计算中得到的。如果进行的是最小延迟分析(一般情况下,如果不开启on_chip_variation,这指的是保持时间检查),Design Compiler会选择引脚A和引脚B导致的最小的转换时间作为Y引脚的转换时间。

图4展示了上面描述的GBA模式中转换时间的计算过程(最大延迟分析)。

图4 GBA模式下转换时间的计算过程(最大延迟分析)

顺带一提,之前版本的PrimeTime提供了timing_slew_propagation_mode变量,它可以指定为worst_arrival或worst_slew,其中worst_slew指的是上面的情况,worst_arrival指的是选择最差到达时间(即对于最大延迟分析,选择最晚到达的信号导致的转换时间;对于最小延迟分析,选择最早到达的信号导致的转换时间)进行计算(最新版本的PrimeTime已废弃,统一使用worst_slew的情况)。

验证手段

如何验证上述原理呢?可以在Design Compiler中使用report_delay_calculation命令报告U1的输入引脚A和B到输出引脚Y的转换时间的计算过程,并使用report_net命令报告线网n即U1的输出引脚Y的转换时间。其实当使用report_net命令时就可以发现,线网n会存储两组上升沿\下降沿转换时间,分别用于建立时间和保持时间的时序分析,即使用GBA模式。而如果是PBA模式,线网n需要为每个输入引脚保存一组上升沿\下降沿转换时间(在此例中是两组),这在线网扇入大时会显著提升分析难度与时间。

PBA的子模式

对于PrimeTime而言,PBA模式还有一些子模式,比如path、exhaustive和ml_exhaustive,它们的区别在本文中不详细解释,具体参考PrimeTime User Guide中的"Path-Based Analysis Modes"一节。

总结

综上所述,GBA模式和PBA模式中,PBA模式更为准确但耗时长(PBA模式下的时序裕量不可能差于GBA模式),而GBA模式更保守但更快。但其实,动态时序分析(时序仿真)才是最准确的时序分析方式。

特殊情况

对于Design Compiler而言,在完成了CTS并使用set_propagated_clock命令创建传播时钟后,传播时钟在时钟路径的延迟是使用PBA模式分析的(需要注意的是,最终触发器时钟端的转换时间还是由GBA模式得到的,也就是说最终触发器时钟端到输出端的延迟以及输出端的转换时间是按照GBA模式计算的),所以当使用report_delay_calculation命令报告时钟路径上的延迟时,会产生如下警告。

Warning: the specific arc is in clock path, report_delay_calculation result may not match with timing report or clock skew report for this arc. (TIM-213)这意味着report_delay_calculation命令依然是使用GBA模式计算延迟,这会导致时序分析报告与该命令的计算结果不一致。

特殊情况的举例说明

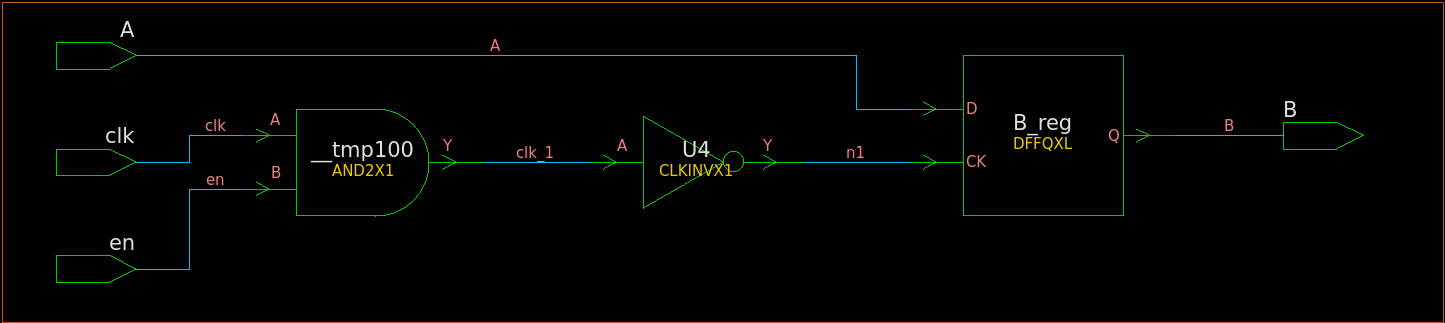

图5 特殊情况的例子

对于图5所示的例子,使用以下SDC约束命令进行约束。

create_clock -period 5 clk

set_propagated_clock clk

set_input_transition 5 en

set_input_transition 0 clk # 这是不必要的,只是为了直观

set_input_delay 0.5 A -clock clk

set_output_delay 0.5 B -clock clk下面使用report_delay_calculation命令,分别报告与门两个输入引脚到输出引脚的转换时间的计算(其中只截取了报告中转换时间相应部分)。

dc_shell> report_delay_calculation -from __tmp100/A -to __tmp100/Y

Warning: the specific arc is in clock path, report_delay_calculation result may not match with timing report or clock skew report for this arc. (TIM-213)

Transition calculations

Transition rise

transition = 0.0178

Table is indexed by

(X) input_pin_transition = 0.0000

(Y) output_net_total_cap = 0.0016

Relevant portion of lookup table:

(X) 0.0120 (X) 0.0200

(Y) 0.0014 (Z) 0.0171 (Z) 0.0171

(Y) 0.0031 (Z) 0.0247 (Z) 0.0247

Z = A + B*X + C*Y + D*X*Y

A = 0.0109 B = 0.0021

C = 4.3777 D = -0.4290

Z = 0.0178

scaling result for operating conditions

multiplying by 1 gives 0.0178

Transition fall

transition = 0.0177

Table is indexed by

(X) input_pin_transition = 0.0000

(Y) output_net_total_cap = 0.0016

Relevant portion of lookup table:

(X) 0.0120 (X) 0.0200

(Y) 0.0014 (Z) 0.0171 (Z) 0.0171

(Y) 0.0031 (Z) 0.0230 (Z) 0.0230

Z = A + B*X + C*Y + D*X*Y

A = 0.0125 B = -0.0048

C = 3.3124 D = 1.6452

Z = 0.0177

scaling result for operating conditions

multiplying by 1 gives 0.0177dc_shell> report_delay_calculation -from __tmp100/B -to __tmp100/Y

Warning: the specific arc is in clock path, report_delay_calculation result may not match with timing report or clock skew report for this arc. (TIM-213)

Transition calculations

Transition rise

transition = 0.1630

Table is indexed by

(X) input_pin_transition = 5.0000

(Y) output_net_total_cap = 0.0016

Relevant portion of lookup table:

(X) 0.2320 (X) 0.4600

(Y) 0.0014 (Z) 0.0232 (Z) 0.0298

(Y) 0.0031 (Z) 0.0303 (Z) 0.0368

Z = A + B*X + C*Y + D*X*Y

A = 0.0105 B = 0.0300

C = 4.2069 D = -0.5170

Z = 0.1630

scaling result for operating conditions

multiplying by 1 gives 0.1630

Transition fall

transition = 0.1728

Table is indexed by

(X) input_pin_transition = 5.0000

(Y) output_net_total_cap = 0.0016

Relevant portion of lookup table:

(X) 0.2320 (X) 0.4600

(Y) 0.0014 (Z) 0.0249 (Z) 0.0320

(Y) 0.0031 (Z) 0.0300 (Z) 0.0370

Z = A + B*X + C*Y + D*X*Y

A = 0.0135 B = 0.0314

C = 3.0154 D = -0.3464

Z = 0.1728

scaling result for operating conditions

multiplying by 1 gives 0.1728

下面使用report_timing命令报告触发器到输出端口B的时序路径,注意-path full_clock选项和-transition_time选项的使用。

dc_shell> report_timing -to { B } -path full_clock -delay max -nworst 1 -max_paths 1 -transition_time -significant_digits 7 -sort_by group

****************************************

Report : timing

-path full_clock

-delay max

-max_paths 1

-transition_time

-sort_by group

Design : test

Version: W-2024.09-SP2

Date : Mon Mar 17 14:34:09 2025

****************************************

Operating Conditions: fast Library: fast

Wire Load Model Mode: top

Startpoint: B_reg (rising edge-triggered flip-flop clocked by clk')

Endpoint: B (output port clocked by clk)

Path Group: clk

Path Type: max

Point Trans Incr Path

-----------------------------------------------------------

clock clk' (rise edge) 2.5000000 2.5000000

clk (in) 0.0000000 0.0000000 2.5000000 f

__tmp100/Y (AND2X1) 0.0177344 0.0333066 2.5333066 f

U4/Y (CLKINVX1) 0.0148552 0.0130653 2.5463719 r

B_reg/CK (DFFQXL) 0.0148552 0.0000000 2.5463719 r

B_reg/CK (DFFQXL) 0.0424689 0.0000000 2.5463719 r

B_reg/Q (DFFQXL) 0.0212743 0.0746608 2.6210327 f

B (out) 0.0212743 0.0000000 2.6210327 f

data arrival time 2.6210327

clock clk (rise edge) 5.0000000 5.0000000

clock network delay (propagated) 0.0000000 5.0000000

output external delay -0.5000000 4.5000000

data required time 4.5000000

-----------------------------------------------------------

data required time 4.5000000

data arrival time -2.6210327

-----------------------------------------------------------

slack (MET) 1.8789673可以看出,在时钟路径上计算反相器U4的延迟时,使用的输入转换时间不是最慢的0.1728,而是0.0177,这是PBA模式的特点。但最终触发器时钟端的转换时间从PBA模式0.0148552调整为GBA模式得到的0.0424689(目前笔者也尚不清楚对触发器时钟端的转换时间进行调整的目的),触发器的延迟因此也是由GBA模式计算得到0.0747,如下所示。

dc_shell> report_delay_calculation -from B_reg/CK -to B_reg/Q

****************************************

Report : delay_calculation

Design : test

Version: W-2024.09-SP2

Date : Mon Mar 17 14:44:04 2025

****************************************

From pin: B_reg/CK

To pin: B_reg/Q

Main Library Units: 1ns 1pF 1kOhm

Operating Conditions: fast Library: fast

Wire Load Model Mode: top

Library: 'fast'

Library Units: 1ns 1pF 1kOhm

Library Cell: 'DFFQXL'

arc sense: rising_edge

arc type: cell

Rise Delay

cell delay = 0.0688

Table is indexed by

(X) input_pin_transition = 0.0425

(Y) output_net_total_cap = 0.0000

Relevant portion of lookup table:

(X) 0.0340 (X) 0.0620

(Y) 0.0003 (Z) 0.0689 (Z) 0.0738

(Y) 0.0007 (Z) 0.0711 (Z) 0.0760

Z = A + B*X + C*Y + D*X*Y

A = 0.0614 B = 0.1754

C = 5.3262 D = 0.0874

Z = 0.0688

scaling result for operating conditions

multiplying by 1 gives 0.0688

Fall Delay

cell delay = 0.0747

Table is indexed by

(X) input_pin_transition = 0.0425

(Y) output_net_total_cap = 0.0000

Relevant portion of lookup table:

(X) 0.0340 (X) 0.0620

(Y) 0.0003 (Z) 0.0752 (Z) 0.0799

(Y) 0.0007 (Z) 0.0779 (Z) 0.0827

Z = A + B*X + C*Y + D*X*Y

A = 0.0674 B = 0.1707

C = 6.6224 D = 0.7002

Z = 0.0747

scaling result for operating conditions

multiplying by 1 gives 0.0747

Cell Delay

rise: 0.0688

fall: 0.0747

Transition calculations

Transition rise

transition = 0.0127

Table is indexed by

(X) input_pin_transition = 0.0425

(Y) output_net_total_cap = 0.0000

Relevant portion of lookup table:

(X) 0.0340 (X) 0.0620

(Y) 0.0003 (Z) 0.0148 (Z) 0.0148

(Y) 0.0007 (Z) 0.0177 (Z) 0.0177

Z = A + B*X + C*Y + D*X*Y

A = 0.0127 B = 0.0000

C = 7.1024 D = 0.0000

Z = 0.0127

scaling result for operating conditions

multiplying by 1 gives 0.0127

Transition fall

transition = 0.0213

Table is indexed by

(X) input_pin_transition = 0.0425

(Y) output_net_total_cap = 0.0000

Relevant portion of lookup table:

(X) 0.0340 (X) 0.0620

(Y) 0.0003 (Z) 0.0232 (Z) 0.0232

(Y) 0.0007 (Z) 0.0260 (Z) 0.0260

Z = A + B*X + C*Y + D*X*Y

A = 0.0212 B = 0.0007

C = 6.8004 D = -1.5765

Z = 0.0213

scaling result for operating conditions

multiplying by 1 gives 0.0213这种特殊情况在PrimeTime中不会发生,PrimeTime默认使用GBA模式计算时钟路径的延迟,如下所示。

****************************************

Report : timing

-path_type full_clock

-delay_type max

-max_paths 1

-group **async_default** **clock_gating_default** **default** clk

-transition_time

-sort_by group

Design : test

Version: W-2024.09-SP2

Date : Mon Mar 17 14:48:52 2025

****************************************

Startpoint: B_reg (rising edge-triggered flip-flop clocked by clk')

Endpoint: B (output port clocked by clk)

Path Group: clk

Path Type: max

Point Trans Incr Path

-----------------------------------------------------------------------------

clock clk' (rise edge) 2.5000000 2.5000000

clock source latency 0.0000000 2.5000000

clk (in) 0.0000000 0.0000000 2.5000000 f

__tmp100/Y (AND2X1) 0.1727631 0.0333065 2.5333065 f

U4/Y (CLKINVX1) 0.0424689 0.0301300 2.5634365 r

B_reg/CK (DFFQXL) 0.0424689 0.0000000 2.5634365 r

B_reg/Q (DFFQXL) 0.0212779 0.0699280 2.6333644 f

B (out) 0.0212779 0.0000000 2.6333644 f

data arrival time 2.6333644

clock clk (rise edge) 5.0000000 5.0000000

clock network delay (propagated) 0.0000000 5.0000000

clock reconvergence pessimism 0.0000000 5.0000000

output external delay -0.4000000 4.6000000

data required time 4.6000000

-----------------------------------------------------------------------------

data required time 4.6000000

data arrival time -2.6333644

-----------------------------------------------------------------------------

slack (MET) 1.9666356

本文详细比较了静态时序分析中的PBA(路径基于分析)和GBA(图基于分析)模式,解释了它们在DesignCompiler和PrimeTime等工具中的应用,以及分析时序路径的方法。强调了PBA的准确性但耗时较长,GBA的保守但速度快,动态时序分析的准确性最高。

本文详细比较了静态时序分析中的PBA(路径基于分析)和GBA(图基于分析)模式,解释了它们在DesignCompiler和PrimeTime等工具中的应用,以及分析时序路径的方法。强调了PBA的准确性但耗时较长,GBA的保守但速度快,动态时序分析的准确性最高。

4283

4283

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?