相关阅读

SDC命令详解![]() https://blog.csdn.net/weixin_45791458/category_12931432.html?spm=1001.2014.3001.5482

https://blog.csdn.net/weixin_45791458/category_12931432.html?spm=1001.2014.3001.5482

目录

DC工具在使用set_drive和set_driving_cell命令建模输入端口驱动能力时,会自动计算输入端口的转换时间,以及由于电阻或驱动单元带来的额外输入端口延迟,而set_input_transition命令允许设计者直接指定输入端口的转换时间(设置了端口对象的min_transition_fall、min_transition_rise、max_transition_fall、max_transition_rise属性),这会覆盖set_drive和set_driving_cell命令计算得到的转换时间,如果想要移除转换时间,使用remove_attribute命令。

本文针对Design Compiler,但该命令同样存在于PrimeTime、IC Compiler等工具中,它们大致相同,略有差别。set_input_transition命令的BNF范式(有关BNF范式,可以参考以往文章)为:

set_input_transition

transition port_list

[-rise] [-fall] [-min] [-max]

-clock clock_name -clock_fall //该选项在SDC 2.1中被废除

//注:该命令的port_list参数一定要放在transition参数后 指定端口转换时间

transition是一个非负的转换时间,越大表示驱动能力越弱,越小表示驱动能力越强,它的单位要与工艺库中指定的时间单位一致。

指定端口列表

指定一个端口列表,包含输入端口或输入输出双向端口,如果有多于一个端口,需要使用引号或大括号包围。

简单使用

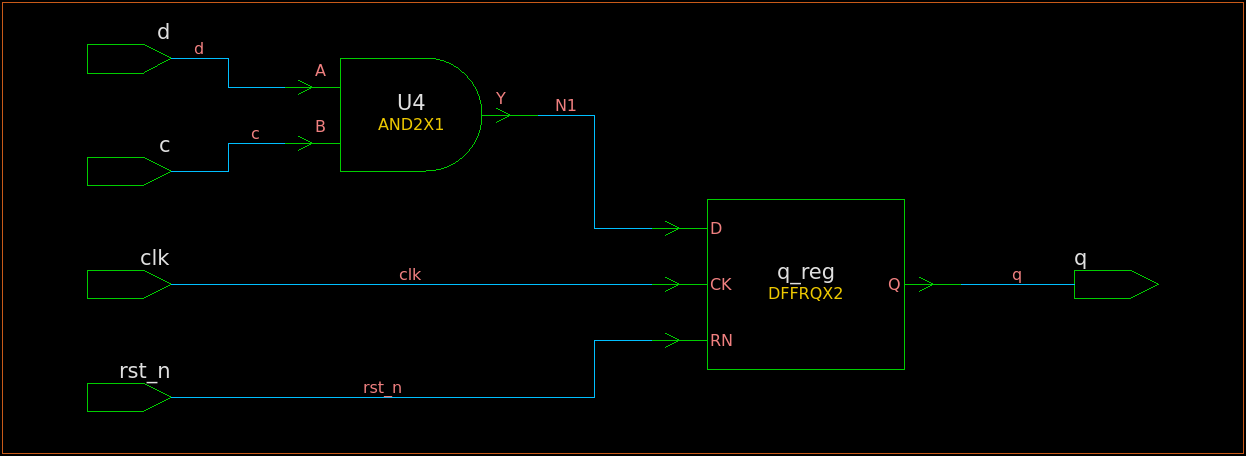

以图1所示的电路图为例,首先在输入端口clk定义一个时钟。

create_clock -period 10 [get_ports clk]

图1 一个简单的例子

接着在输入端口d、c上分别定义两个输入延迟,参考时钟为clk。

set_input_delay 0.5 -clock clk [get_ports d]

set_input_delay 0.5 -clock clk [get_ports c]下面的set_input_transition命令在输入端口d上设置了端口转换时间。

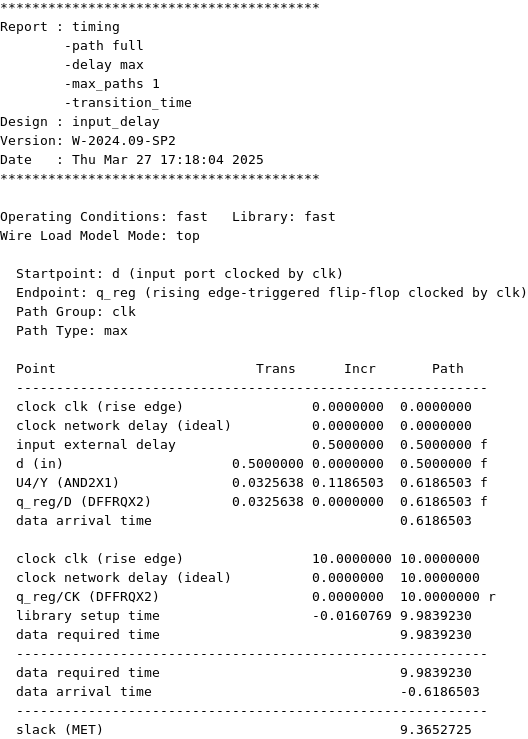

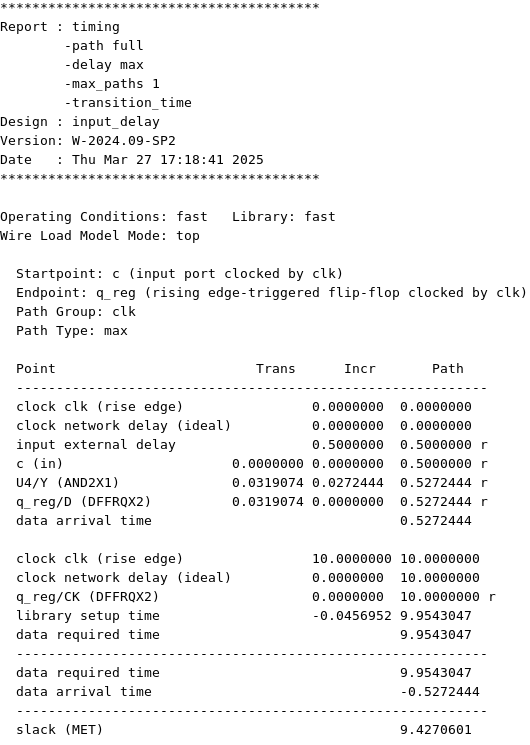

set_input_transition 0.5 [get_ports d]最后使用report_timing命令分别报告输入端口d、c到触发器的时序路径,记得使用-transition_time选项,结果如图2、图3所示。

图2 输入端口d的建立时间时序报告

图3 输入端口c的建立时间时序报告

从对比图4、图5可以看到,设置了驱动电阻的输入端口d的输入转换时间不再是0,而是0.5,并且输入端口d、c没有因为设置驱动而引入额外的延迟。

指定上升、下降沿

-rise选项用于指定驱动作用于端口的上升沿、-fall选项用于指定驱动作用于端口的下降沿。如果这两个选项都没有指定,延迟同时作用于时钟的上升沿和下降沿(相当于它们同时指定)。

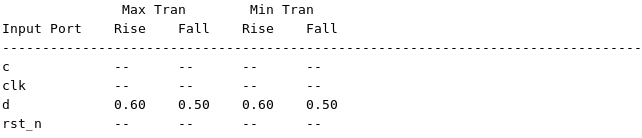

下面的命令指定了端口d的上升沿转换时间为0.6,下降沿转换时间保持为0.5。

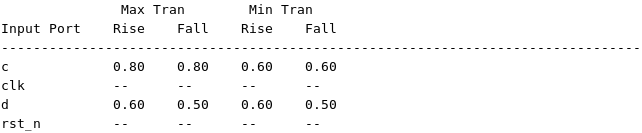

set_input_transition -rise 0.6 [get_ports d]可以使用report_port -verbose命令报告端口的驱动设置情况,如图4所示。

图4 端口转换时间报告

指定最大、最小条件

-max选项用于指定转换时间作用于最大延迟分析(一般情况下,如果不开启on_chip_variation,这指的是建立时间检查),-max选项用于指定转换时间作用于最小延迟分析(一般情况下,如果不开启on_chip_variation,这指的是保持时间检查)。如果这两个选项都没有指定,转换时间同时作用于最大延迟和最小延迟分析(相当于它们同时指定)。

下面的命令设置最小延迟的输入端口c的转换时间为0.6,最大延迟的输入端口c的转换时间为0.8,如图5所示。

set_input_transition -max 0.8 [get_ports c]

set_input_transition -min 0.6 [get_ports c]

图5 端口转换时间报告

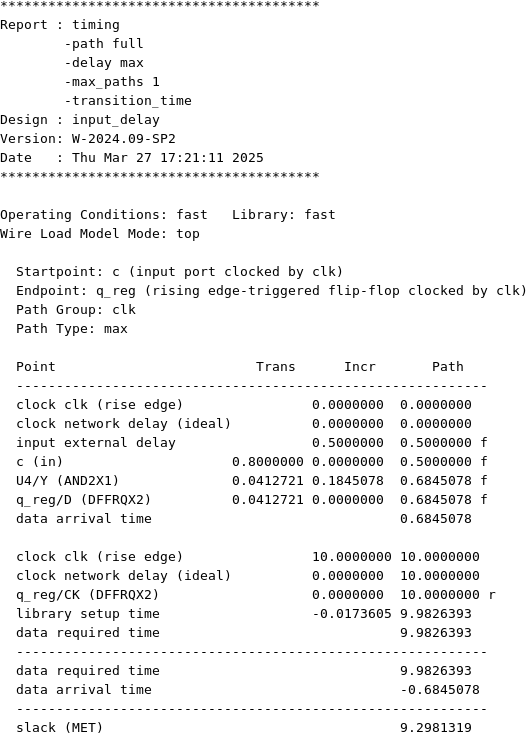

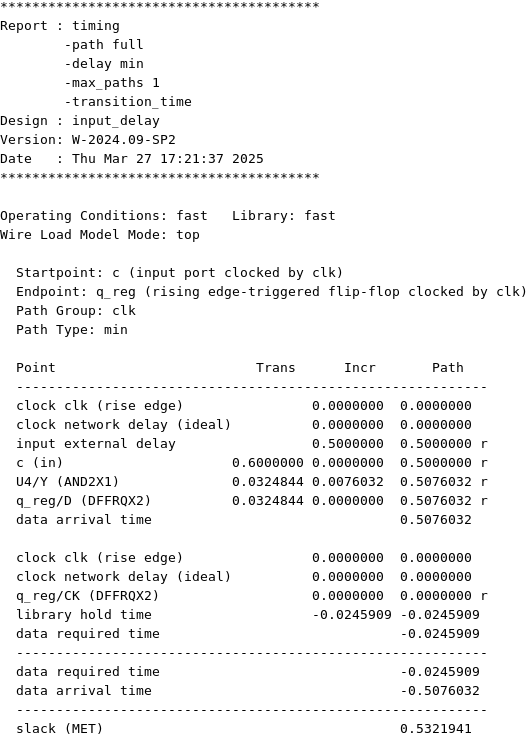

使用report_timing命令分别给出输入端口c的建立时间和保持时间的时序分析报告,如图6和图7所示。

图6 输入端口c的建立时间时序报告

图7 输入端口c的保持时间时序报告

与set_clock_transition命令的区别

在之前的文章中,我们使用了set_clock_transition命令对时钟转换时间建模,其实这是在预布局阶段(pre-layout),即时钟树综合(CTS)前对时钟转换时间的一种估计。此时DC会忽略任何时钟路径上的延迟,直接使用set_clock_transition命令的指定值当做触发器时钟引脚处的转换时间。

而一旦时钟树综合完成,使用set_propagated_clock命令将理想时钟变成传播时钟后,可以在时钟输入端口使用set_input_transition命令,并让DC自动计算时钟路径上的延迟。

写在最后

-clock clock_name和-clock_fall选项已经被废除,不要在设计中使用它们。

本文详细介绍了DC工具中的set_input_transition命令,用于直接指定输入端口的转换时间,包括指定转换时间、端口列表、上升/下降沿及最大/最小路径分析,并与set_clock_transition命令进行了对比。

本文详细介绍了DC工具中的set_input_transition命令,用于直接指定输入端口的转换时间,包括指定转换时间、端口列表、上升/下降沿及最大/最小路径分析,并与set_clock_transition命令进行了对比。

3321

3321

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?