AlphaFold2在线预测蛋白

colab 提供了一个网页接口可以调用alphafold预测蛋白结构

前提条件:

自己能访问到外网,并且有谷歌账号

1、访问下面地址:

https://colab.research.google.com/github/sokrypton/ColabFold/blob/main/AlphaFold2.ipynb

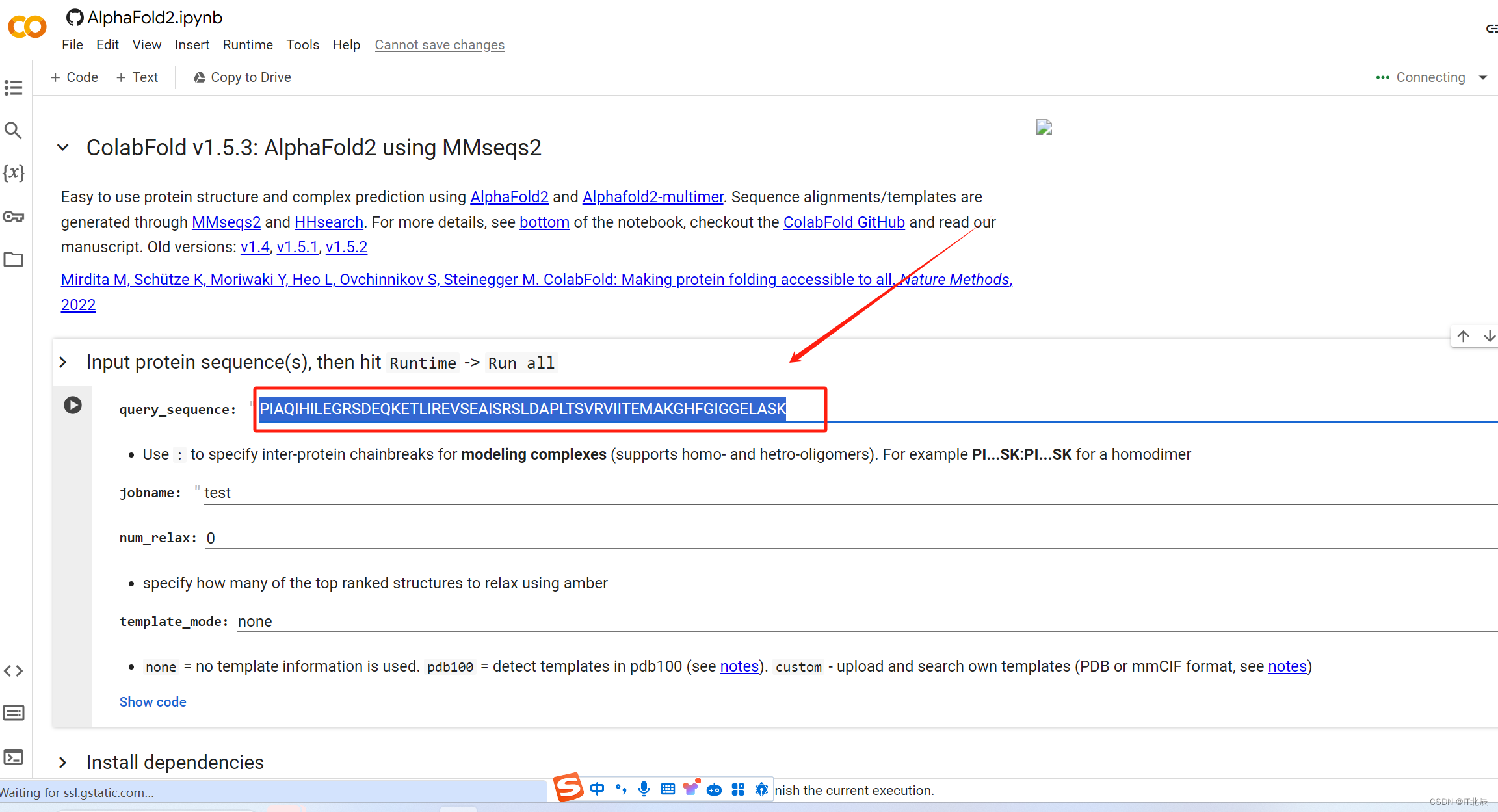

2、在query_sequence中输入自己的蛋白序列。

测单个蛋白序列直接输入就行,多个蛋白序列需要用冒号(:)来连接。

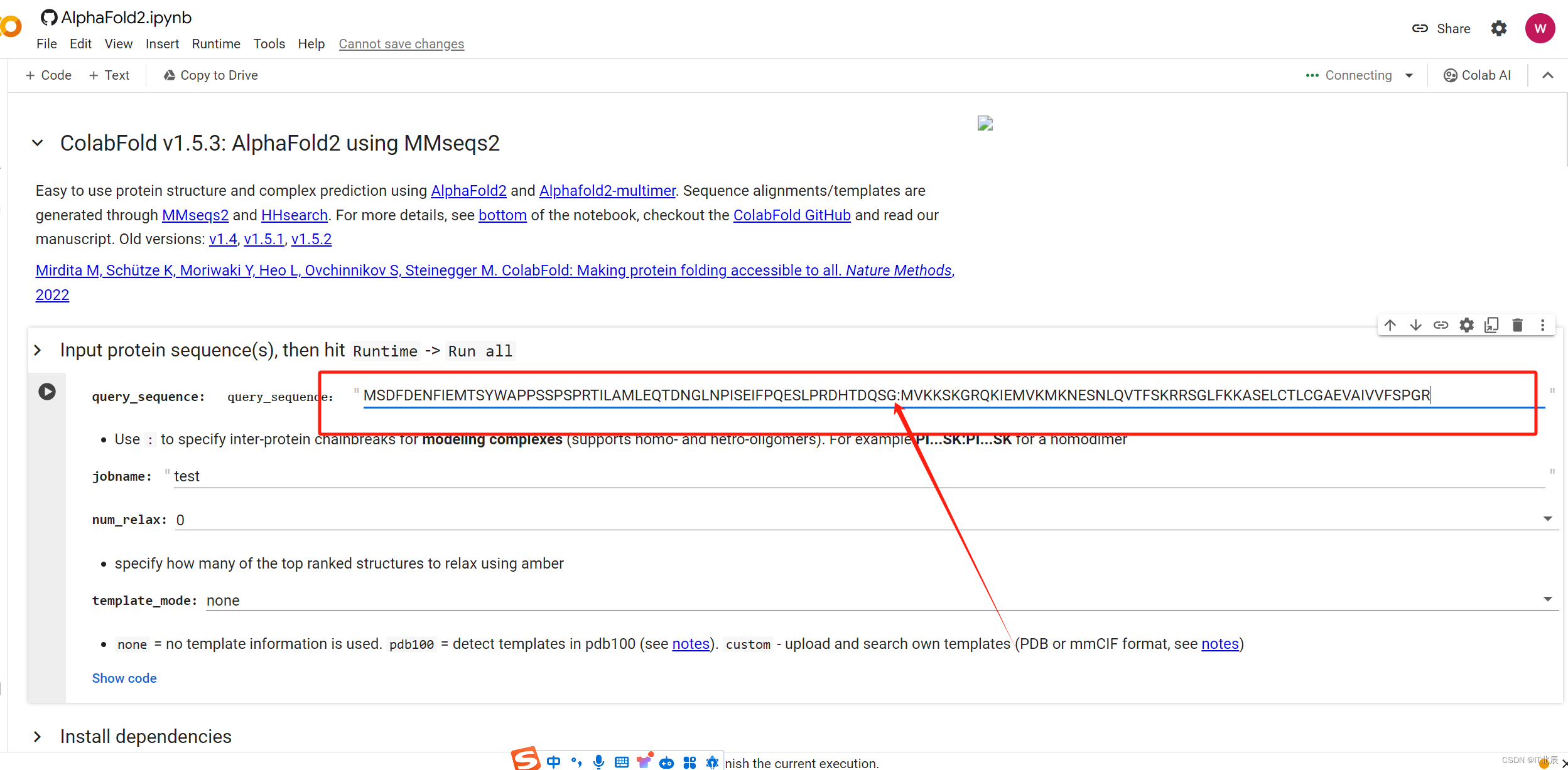

比如我的是这2个蛋白序列:

erIN:

MSDFDENFIEMTSYWAPPSSPSPRTILAMLEQTDNGLNPISEIFPQESLPRDHTDQSG

AGL88:

MVKKSKGRQKIEMVKMKNESNLQVTFSKRRSGLFKKASELCTLCGAEVAIVVFSPGR

在query_sequence中 输入内容就是这样的:

MSDFDENFIEMTSYWAPPSSPSPRTILAMLEQTDNGLNPISEIFPQESLPRDHTDQSG:MVKKSKGRQKIEMVKMKNESNLQVTFSKRRSGLFKKASELCTLCGAEVAIVVFSPGR

注:erIN和AGL88 用冒号:来连接!!!!

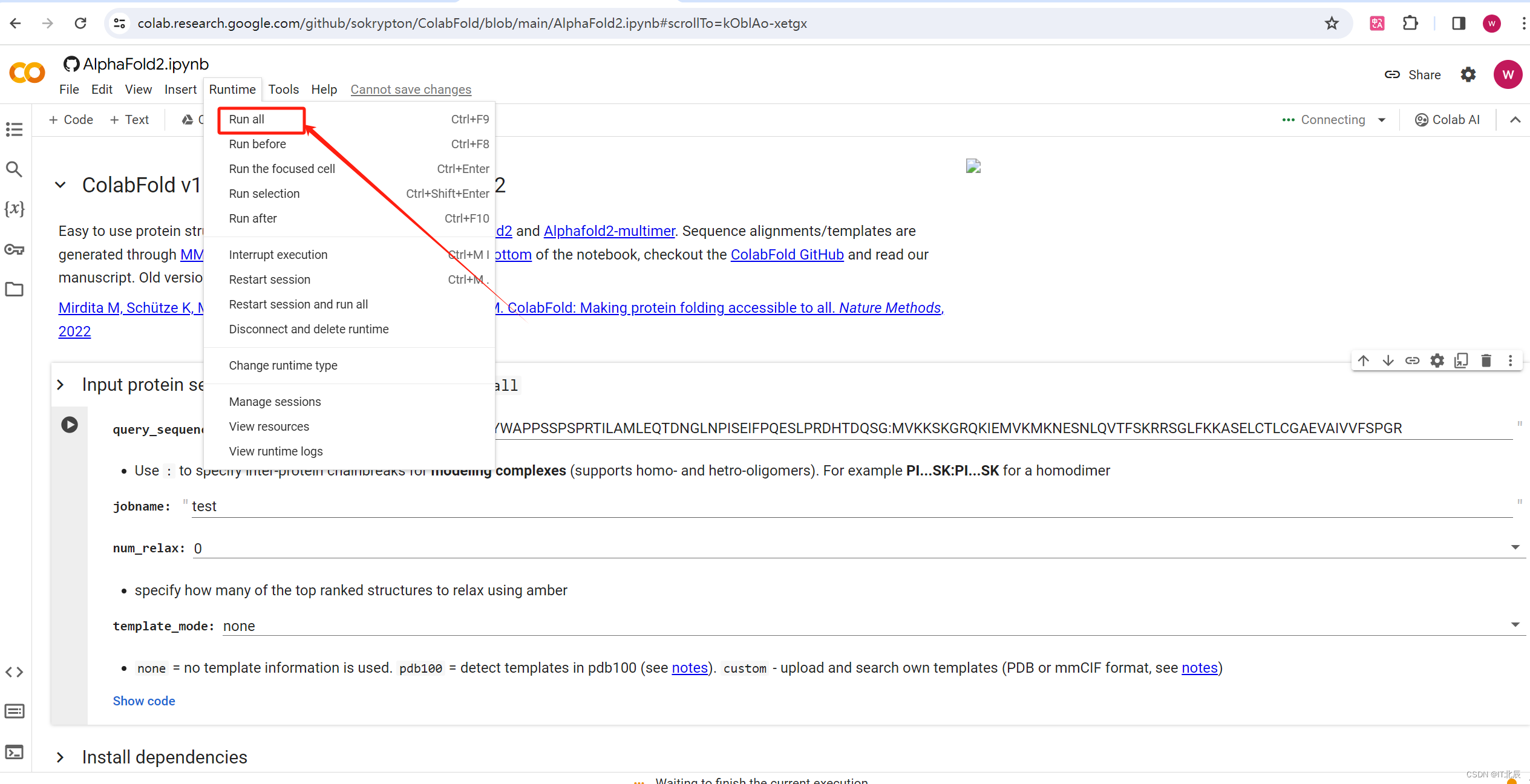

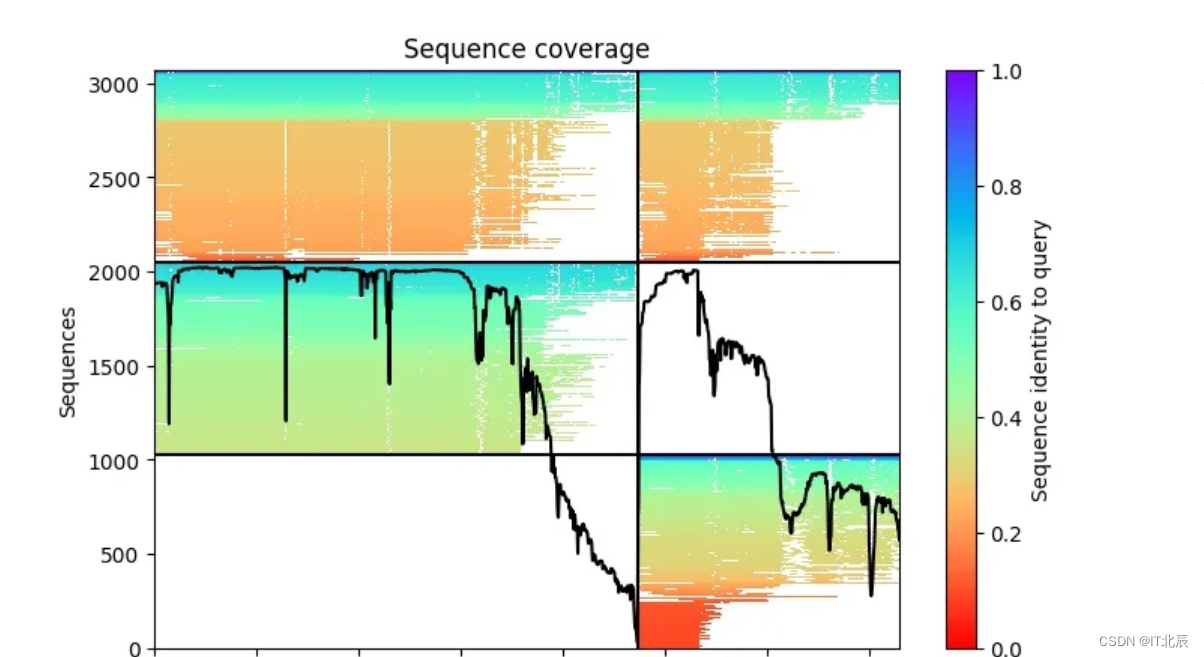

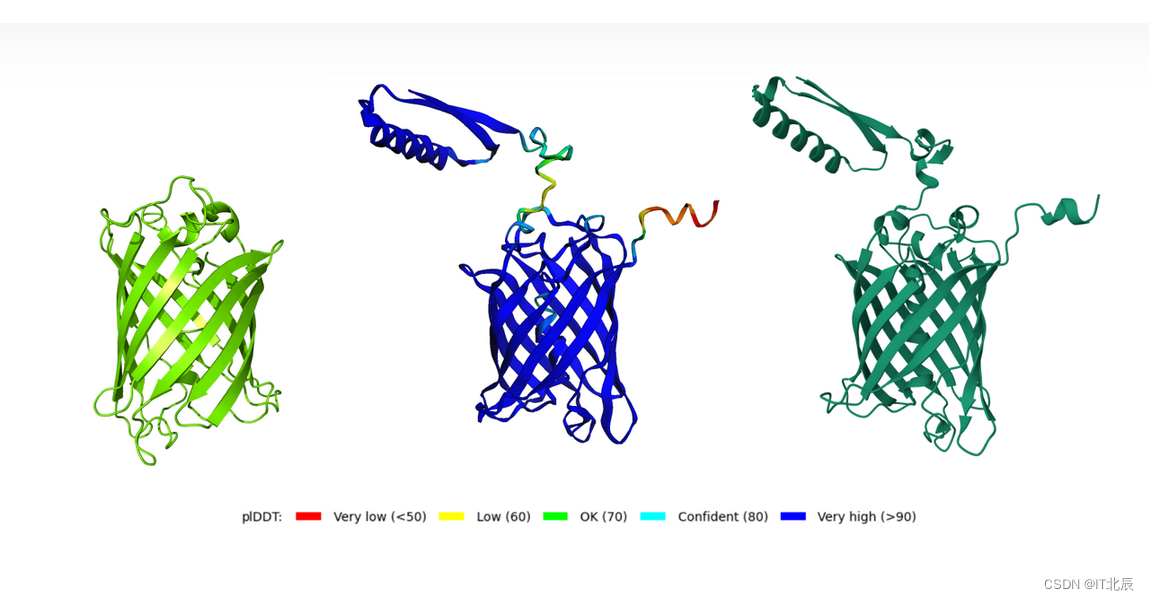

3、然后点击运行->全部运行,大约30min-1hour可以完成计算,会显示自己的序列图

3、然后点击运行->全部运行,大约30min-1hour可以完成计算,会显示自己的序列图

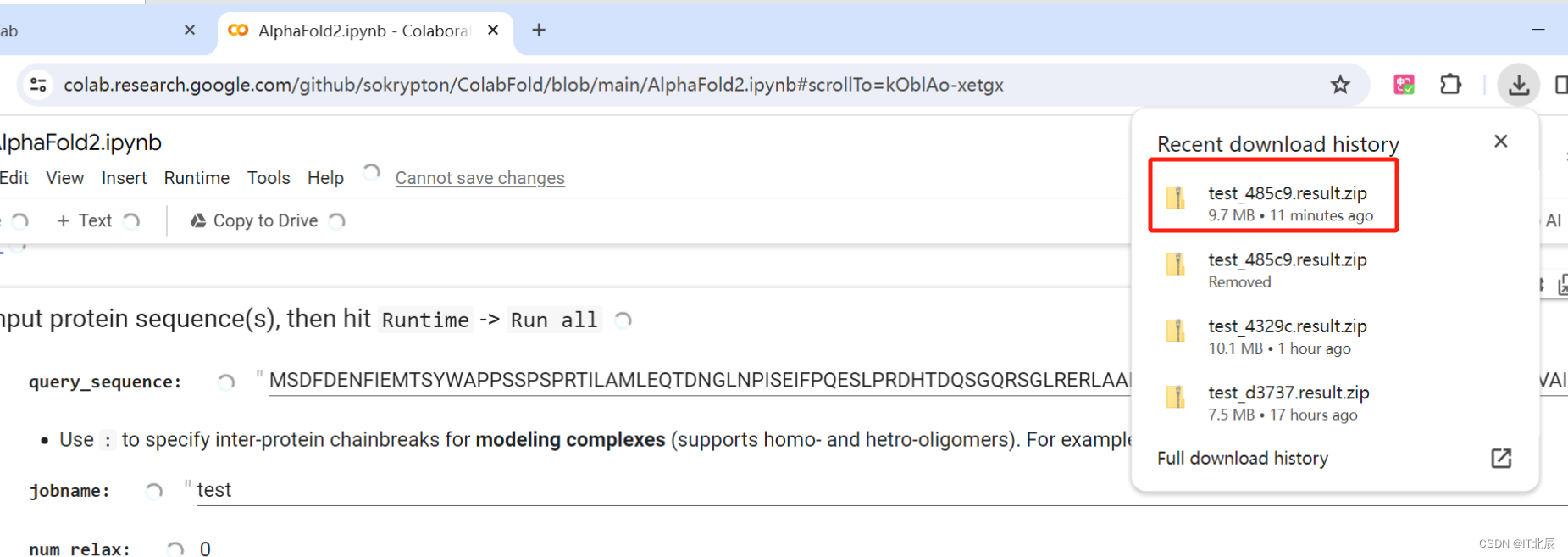

4、最后最后会自己下载压缩文件给你。

4、最后最后会自己下载压缩文件给你。

今天的分享就到这里了。有收获的小伙伴,记得点赞、收藏、分享哦!

如果您对本次分享的内容感兴趣的话,记得关注关注哦!不然下次找不到喽!

关注不迷路哦!“好记性不如烂笔头”,IT小本本 —— 记录IT知识,分享打工人真实的日常操作笔记!!!

😝有需要的小伙伴,可以V扫描下方二维码免费关注哦!

13万+

13万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?