串口收发之ROM存储

前言

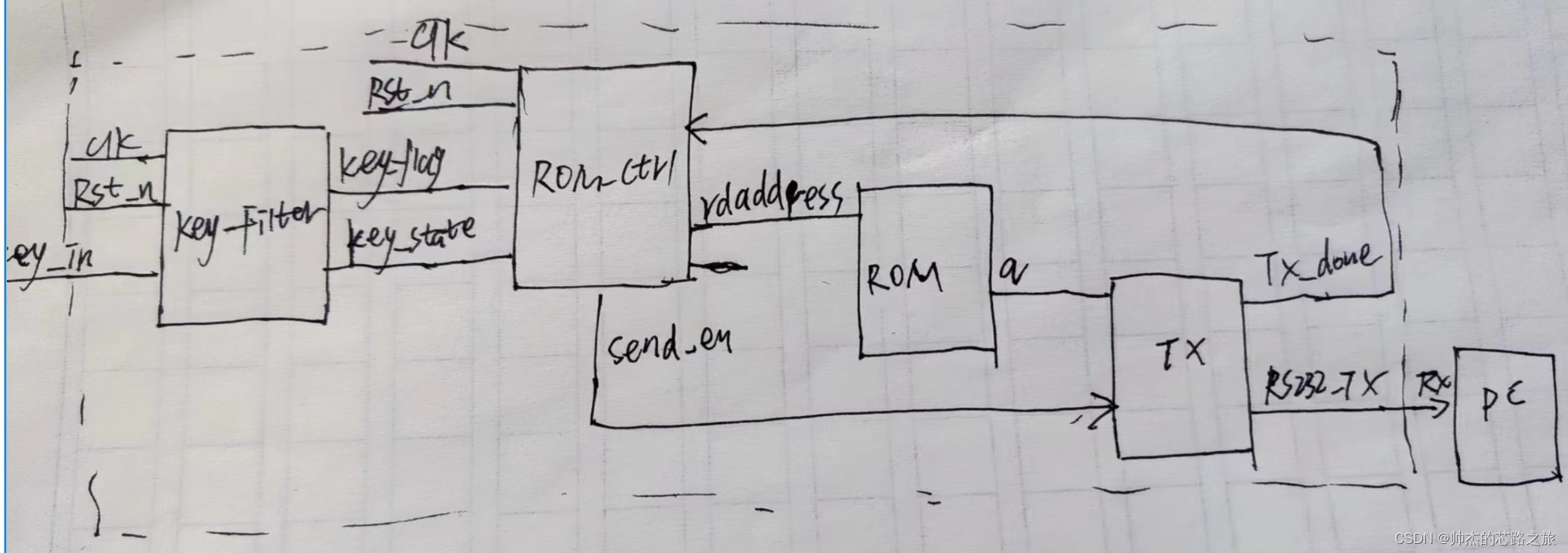

将ROM中的数据读取出来,通过串口发送到上位机。

整体设计

模块划分

1、按键消抖模块

2、ROM控制器模块

3、创建ROM IP核模块

4、串口发送模块

前面已经设计好了串口发送模块和按键消抖模块,还剩ROM IP的创建和控制ROM模块的设计。

读ROM控制模块设计:

1、address:读地址端口

2、q:读数据端口

3、设置单时钟模式clock来控制所有寄存器

如何读ROM?

只要当前时刻给出写地址rdaddress,ROM输出端q就是对应地址的存储单元中的数据。

在什么时刻发送数据?

一开始rdaddress为0,q是地址为0的存储单元中的数据,第一次按下按键,使能Send_en,发送数据,然后产生Tx_done标志信号,作为写地址自加的条件,同时又使能Send_en,

这样就实现了q端数据始终等于当前输入到ROM中的rdaddress对应的存储单元中的数据。

ROM IP核

ROM:只读存储器,只能读出事先所存的数据,一旦存储无法改变且掉电不丢失。

事实上在FPGA中通过IP核生成的ROM调用的都是FPGA内部的RAM资源,掉电数据丢失。

用IP核生成的ROM模块与RAM模块相比只是不能写数据而已,提前添加了数据文件(.mif格式),对ROM中的数据进行初始化。

ROM的读操作与单端口RAM配置中的读操作相同。

-

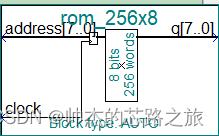

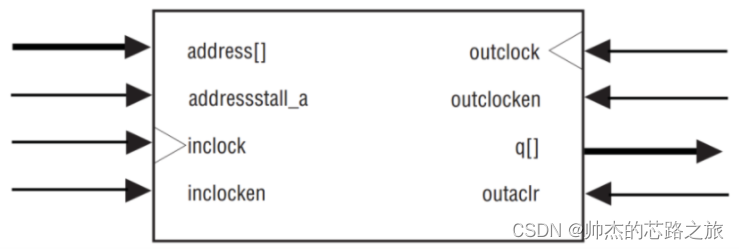

单端口ROM:提供一个读地址端口和一个读数据端口,只能进行读操作。

address:读地址端口

q:读数据端口

addressstall_a:地址使能控制,为高电平时,有效地址时钟会保持之前的地址【创建IP时可选】;

inclock、outclock:支持输入与输出时钟模式和单时钟模式;

在输入与输出时钟模式下,输入时钟控制读地址寄存器;输出时钟控制数据q输出寄存器。

在单时钟模式下,没有inclock、outclock,只有一个clock信号,可以通过单时钟以及时钟使能clockena来控制M9K存储器模块中所有寄存器。

inclocken、outclocken:使能输入时钟和输出时钟;

outaclr:异步复位信号。

ROM模式没有写使能、字节使能、数据输入寄存器,写地址寄存器。 -

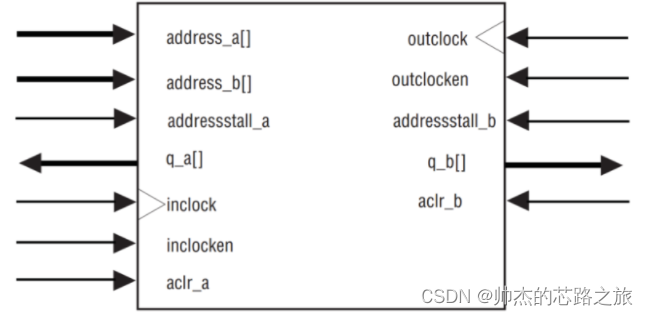

双端口ROM:与单端口ROM类似,区别是提供两个读地址和两个读数据端口,看成两个单端口ROM的合并。

这里只进行单端口ROM IP核的创建,实现对ROM中数据简单的读取就行。

创建单端口ROM IP核

.mif格式文件的制作:

ROM中提前添加mif文件,对ROM中的数据进行初始化。

文件格式如下:

一般mif格式文件的创建使用脚本进行转换,比如实现串口传图显示,将图像像素值数据存到ROM中;对应想测试对ROM中数据进行读取,使用Quartus II软件可以创建mif文件。

1、mif格式文件中生成的数据位宽是8bit,这里设置数据位宽为8bit;

设置存储容量为256个数据,即256个8bit数据;

选择单时钟模式,控制读地址寄存器和读数据寄存器;【若是双时钟模式,输入时钟控制读地址寄存器,输出时钟控制读数据寄存器】

2、输出端口q是否需要寄存一拍,一般不选择;

ROM模式没有写使能;

这里也不勾选时钟使能信号、ROM异步复位信号aclr;

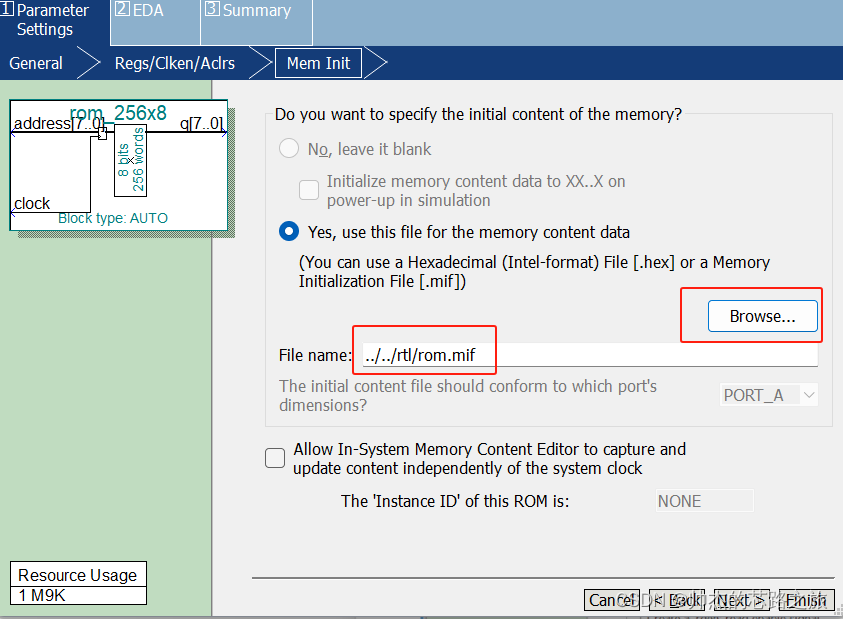

3、加载数据文件,添加之前生成的mif格式文件

2590

2590

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?