1、ic全流程:

- 结构及电学特性规范

- RTL编码

- 为包含存储单元的设计插入 DFT memory BIST。(在Memory周围加上激励,MBIST检测到Memory有问题后将有问题的cell映射到冗余的好的cell上去,MBIST激励是自己生成的)。

- 动态仿真

- DC综合

- 形式验证,将综合后的网表和RTL进行对比

- 使用PT进行STA和后仿(动态时序仿真)

- 布局工具进行时序约束前的前标注,具有时序驱动单元布局、时钟树插入和全局布线的初始布局划分,将时钟树转换到驻留在DC中的原始设计。

- 在 DC 中进行设计的布局优化

- 使用 Formality 在综合网表和时钟树插入的网表之间进行进行形式验证

- 从全局布线得到的估计时间数据反标注到 PT,使用全局布线后提取的估计延时数据在 PT 中进行静态时序分析和后仿(动态时序仿真)

- 设计的详细布局

- 提取来自详细布局设计的实际时间延迟,实际提取时间数据反标注到 PT,使用 PT 进行布局后的静态时序分析

- 布局后的门级功能仿真(如果需要的话)

- 在 LVS 和 DRC 验证之后交货。

https://picture.iczhiku.com/resource/convert/6b24e376d53c49df9d4e503bdec43594.pdf

2、逻辑综合就是先将rtl利用gtech库转化为dc内部格式,后再转化为门级网表。物理综合还需要floorplan的信息。

3、retiming,当组合逻辑太复杂时,RTL中只需要在输出Y连续打三拍,综合时compile_ultra-retiming,工具会自动拆分复杂的组合逻辑OP为op1,op2,op3,并插入寄存器,最大程度上保证均匀的插入流水线。长指令中的综合就是用的此逻辑。

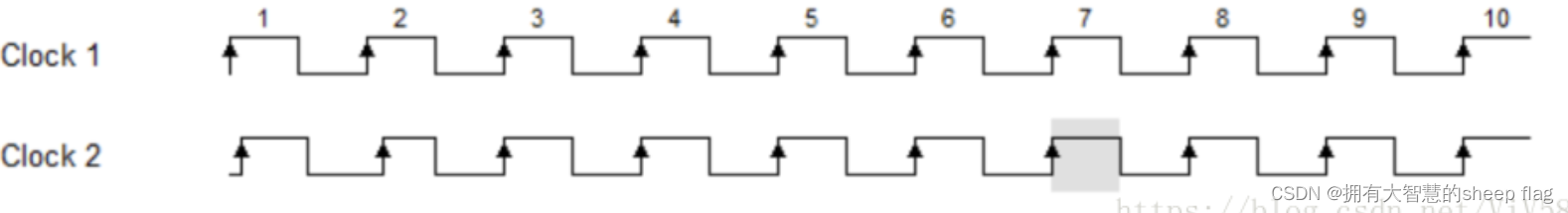

4、时钟jetter(0.05) 由于晶振本身稳定性,电源以及温度变化等原因造成了时钟频率的变化,指的是时钟周期的变化。也即相对于理想时钟沿产生的不随时间积累的、时而超前、时而滞后的偏移。它指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。这个值需要问pll。

由于晶振本身稳定性,电源以及温度变化等原因造成了时钟频率的变化,指的是时钟周期的变化。也即相对于理想时钟沿产生的不随时间积累的、时而超前、时而滞后的偏移。它指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关,布线对其没有影响。这个值需要问pll。

它使setup timing更严格,但是对hold timing无影响(hold check 是同沿检查)。

setup和hold检查逻辑_hold time为什么同沿检查-CSDN博客

clock jitter是否对hold time有影响?(文末有福利)-CSDN博客

5、clock_skew(0.1):

同一时钟到达不同触发器的clk端之间的差异。在cts之后可以由工具算出,在pre-cts阶段,一般设置成最高频率的百分之5到百分之10。

6、通过设置clock uncertainty 来给 design 预留 margin:

Pre-cts 阶段 clock_uncertainty -setup = clock jitter + 预估 clock skew + setup_margin

clock_uncertainty -hold = 预估 clock skew + hold_margin(一般不关注hold_check)

Post-cts 阶段 clock_uncertainty = clock jitter +setup_margin (此时 clock skew 已经确定)

hold_uncertainy = hold_margin

7、关于时钟的transition?

指的是clock的slew时间,跟时钟上升沿和下降沿有关,一般设置clock周期的0.1到0.2(时钟周期长,爬坡要慢一点),但是如果这个值超过了lib里面的max transition,就按照max transition设置。

list_libs可以查看工艺库,report_lib可以查看库的具体内容,吃进去的是db文件。

DC综合库(时序库)和DC的设计对象-腾讯云开发者社区-腾讯云

查看slew_lower_thresshold_pct_rise, slew_upper_thresshold_pct_rise, slew_lower_thresshold_pct_fall,slew_upper_thresshold_pct_fall的值。

8、为什么要设置虚拟时钟?

在接口时序约束中为什么设置虚拟时钟(virtual clock)? - 知乎

9、最大最小input_delay和output_delay?注意这个要相对于vclk

set_input_delay/set_output_delay-CSDN博客

input_delay:时钟沿多久后信号到达模块。

output_delay:输出信号在后级模块时钟沿前多久准备好。

max一般设置为时钟周期的70%。

min的设置一般是为了防止出现大量的hold violation,从而在auto fix hold时插入大量buffer。

10、set_input_transition 和set_output_transition 的设置:

建议在cts之前设置set_clock_transition,在cts之后设置set_input_transition。越大表示驱动能力越强,越小表示驱动能力越弱。他和set_clock_transition的区别在于set_clock_transition所指定的transition value会apply到整个clock network上,而不是在不同的点重新去计算.set_input_transition只会作用于指定的port,对于这个port的logic core上的其他点,transition value会根据前一级进行计算。

https://juejin.cn/post/7123460897737015303

11、setup time和hold time

setup time是指在时钟有效沿(下图为上升沿)之前,数据输入端信号必须保持稳定的最短时间。

hold time是指在时钟有效沿(下图为上升沿)之后,数据输入端信号必须保持稳定的最短时间。

建立时间(setup time)和保持时间(hold time)详析 - 知乎

12、将路径分组:一般指定以下3组,clk组会自动分配。

#输出一组(-weight:对某条路径加重优化)

group_path -name output -weight 5 -to [all_outputs]#除去clk之外的输入一组

group_path -name input -from [remove_from_collection [all_inputs] $ports_clock_root]#所有输入信号到所有输出信号的路径

group_path -name in2out -from [remove_from_collection [all_inputs] $ports_clock_root] -to [all_outputs]#CLK :包含起点、终点均在Design内部的时序路径。当在sdc中创建了名为“CLK”的时钟,便会自动形成“CLK”分组,终点clk为准。如果Design中有多个时钟,则会分属于不同名字的Path Group。

额外的:

#*clock_gating_default** : 将包含clock gate(工具自动插入)的路径额外分成一组。DC则会单独优化包含clock gate的路径,在报告中单独呈现,intergrated clock gating cell(ICG)。

自动插入ICG:

compile_ultra -gate_clock -scan

将其单分成一组:

set timing_separate_clock_gating_group true注意ICG容易出现setup_violation:

后端Timing基础概念之:为何ICG容易出现setup violation? - 知乎

#**default** : 未划分到以上分组的默认分组,比如设置时序例外的路径(如multi-cycle path)。

【IC知识小站】DC Timing Path Group - 知乎

#mem到寄存器或者寄存器到mem(库文件的lib有相关信息吧)。

group_path -from [get_cells -hier * -filter "@is_memory_cell== true"] to [all_registers] -name m2r

group_path -from [all_registers] -to [get_cells -hier * -filter "@is_memory_cell== true"] -name r2m13、关于set_false_path:

不希望工具分析的路径。

14、写约束(constraints.tcl):

//路径分组

create_clock -period ${clock_period} [get_ports sys_clk]

group_path -name input -from [remove_from_collection [all_inputs] $ports_clock_root]

group_path -name in2out -from [remove_from_collection [all_inputs] $ports_clock_root] -to [all_outputs]

//创建时钟

create_clock -period ${clock_period} [get_ports sys_clk]

//时钟uncertainty

set_clock_uncertainty -setup [expr ${skew} +${jetter} + ${setup_margin}] [get_clocks sys_clk]

set_clock_uncertainty -hold [expr ${skew} + ${setup_margin}] [get_clocks sys_clk]

//时钟transition

set_clock_transition -max -rise 0.1 [get_clock sys_clk]

set_clock_transition -max -fall 0.1 [get_clock sys_clk]

set_clock_transition -min -rise 0.1 [get_clock sys_clk]

set_clock_transition -min -rise 0.1 [get_clock sys_clk]

//设置虚拟时钟

create_clock -name VCLK -period ${clock_period}

set_clock_uncertainty -setup [expr ${skew} +${jetter} + ${setup_margin}] [get_clocks {VCLK}]

set_clock_uncertainty -hold [expr ${skew} + ${setup_margin}] [get_clocks {VCLK}]

//设置clk有无穷大的驱动能力

set_ideal_network sys_clk

//false_path

set_flase_path -hold -from [all_inputs]

set_false_path -hold -to [all_outputs]

//设置最大最小输入延迟 set_input_delay一般用虚拟时钟

set_input_delay $delay_num -max -clock VCLK $inputs

set_input_delay 0.0 -min -clock VCLK $input

//设置最大最小输出延迟

set_output_delay $delay_num -max -clock VCLK $outputs

set_output_delay 0.0 -min -clock VCLK $output

15、通常情况下,综合工具会把以下几种cell库都吃进去,然后根据timing约束,由综合工具在满足timing约束的情况下自动选择使用什么cell,大部分情况下三种cell都会使用,在timing比较吃紧的path上会大量使用LVT cell,timing裕量比较大的地方使用HVT/SVT cell。若为了节省功耗拿掉LVT很可能造成由于时序不收敛而使得综合工具插入大量buffer,既增大了面积又增加了功耗,使结果不尽如人意。器件单元库:

-

HVT cell:阈值电压高,但是功耗低,速度慢

-

LVT cell:阈值电压低,但是功耗高(漏电流大),速度快

-

SVT cell:介于两者之间

数字后端知识点扫盲——HVT/SVT/LVT cell_hvt svt lvt-CSDN博客

16、器件库位置

- 一般sram在techology/tsmc28nm/mv

- svt在techology/tsmc28nm/std/tcbn....190a/TSMCHOME/digital

- lvt在techology/tsmc28nm/std/tcbn....lvt_190a/TSMCHOME/digital/

- hvt在techology/tsmc28nm/std/tcbn....hvt_190a/TSMCHOME/digital/

- /Front_End/timing_power_noise/CCS/

- 一般dc吃进去的是db文件,list_libs可以查看工艺库,report_lib可以查看库的具体内容。

17、综合后产生的文件

- set_svf ${design_name}.svf,给svf文件一个名字,默认综合工具会产生一个svf文件,用于形式验证。

- write -format ddc -hierarchy -output ${design_name}_compila_ultra.ddc,保存了综合后的所有信息,包括timing ,db,lib等,dc_shell里面read_ddc,就可以读取保存的信息。

- write_sdc -nosplit ${design_name}_synthesis.sdc,标准延时约束文件,里面包含对面积、输入输出delay、maxfanout, maxtransition,等约束,由DC产生,需要给到后端。

- .sdf:主要包含了网表中所有器件的延迟信息,用于时序仿真;PT 会结合后端工具生成的一个更为精确的sdf ,所以,通常会用PT的sdf 文件做后仿真。

- write -f verilog -hierarchy -o ${design_name}_synthesis.v 产生网表文件。

- 其中.ddc,.sdc和网表文件需要给后端做icc。

综合&后端各种类型文件都是干嘛的?持续更新~_fram 由lef产生的-CSDN博客

https://www.cnblogs.com/lanlancky/p/17416788.html

- check_design -multiple_designs >check_design,检查设计是否有问题。

- check_timing > check_timing,要对所有的路径添加约束,若跨时钟域则添加false_path,此命令可以检查是否漏掉。

- report_qor > qor,绝大部分信息在qor文件里面:(1)在timing path group “sys_clk”里面需要关注:levels of logic:指最深的逻辑深度;critical path length:最长路径的arrival时间。critical path slack:最差路径的时序裕量。critical path clk period:时钟周期。total negative slack:将为负值的总的时序裕量加起来。No. of hold violation:时序违规的总条数。关于hold的很少关注。(2)在cell_count里需要关注:combinational cell count:组合逻辑cell数量;sequential cell count:时序逻辑cell数量;Macro count:mem数量。(3)在area里面需要关注:cell area:设计单元所占总面积;macro box area:mem所占总面积。可以通过(cell area-mem area)/面积利用率反推总面积(大概50%~70%),而mem的利用率要高于逻辑电路(大概80%~90%)。【芯片前端】第一次看DC综合报告时看些什么内容_dc综合面积报告怎么看-CSDN博客

- report_timing -delay max -max_paths 10 -nosplit -path full_clock_expanded -nets -transition_time -input_pins > timing-max 报告时序延迟最大值的10条路径,每组10个。代表了setup。

- report_timing -delay min -max_paths 10 -nosplit -path full_clock_expanded -nets -transition_time -input_pins > timing-min 与上面相反,代表了hold。

- report_area > area,报告面积。会将自动插入的clk_gate的面积显示出来,面积的单位是微米。

- report_constraint -all_violators -nosplit > constraint_violators,报告所有的违规

- report_clock_gating -multi_stage -verbose -gate > clock_gating,报告插入的clock_gating

15、一些脚本语言

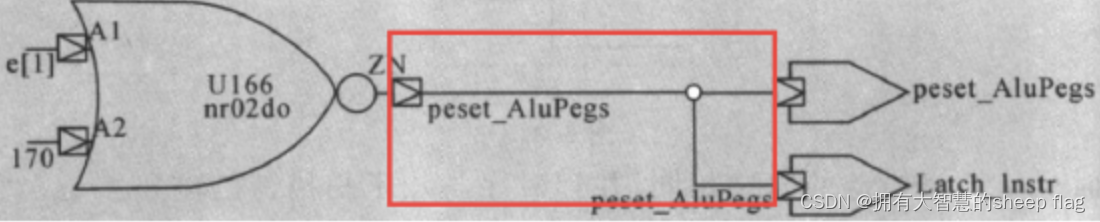

- set_fix_multiple_port_nets -all -buffer_constants [get_designs *],此命令用来去除多端口连线,在默认的情况下,如遇到下述的情况,DC写出网表时,会在网表产生assign指令。assign指令会使非Synopsys公司的工具在读入文件时产生问题。该指令也可能会在反标( back-annotation)流程中产生问题。

- change_names -rules verilog -hierarchy -verbose > change_name,将换掉的名字输出。此命令可以将设计中的特别字符去掉,比如说reg[31]和reg[31:0]综合后会用两个名字表示同一个信号,一些工具会理解出错。

https://www.cnblogs.com/xh13dream/p/8798529.html

16、关于link_library和target_library?

target_library是link_library的子集,target里面放的是标准单元库,link里面还放了什么IO库,IP库等等,比如说rom,ram。

Target library和Link library的区别(转)_Myron_Yu_新浪博客

17、怎样修时序?

- 增加pipeline和retiming

- 细分group path,设置不同group的权重。设置目标slack,使工具能更强的优化对应的timing(工具可以换阈值电压小的器件吧)。

- 可以compile -scan -inc(增量编辑),先设置严格的约束,移除后添加正确约束做增量编译。

- 驱动的net太长可能导致driver变弱(电容充放电时间变长就更会容易造成violation,同样transition也是同样的原理,cell的delay其实是根据它的input transition,以及output load查表计算得来),可以插入buffer提高驱动能力。(后端给加)

- 若某个cell的output transition比input transition大很多,那说明这个cell的驱动不够,我们可以尝试size up一下。但是sizeup可能带来的影响就是load变大,可能造成前一级无法驱动后一级。

- 或许可以在clock_path上加buffer。

- 若修hold violation只需在data route上增加buffer或者增大launch clk或者较小capture clk(谨慎使用)。

本文概述了集成电路设计过程中从RTL编码、内存BIST测试、DC综合技术(包括逻辑综合、物理综合、时序分析和优化)、到虚拟时钟设置、输入输出延迟管理、时序约束调整以及如何修复setup和holdviolation的详细步骤。

本文概述了集成电路设计过程中从RTL编码、内存BIST测试、DC综合技术(包括逻辑综合、物理综合、时序分析和优化)、到虚拟时钟设置、输入输出延迟管理、时序约束调整以及如何修复setup和holdviolation的详细步骤。

764

764

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?