时钟门控技术就是一种非常简单和有效的功耗控制方法,它的基本原理就是通过关闭芯片上暂时用不到的功能和它的时钟,从而实现节省电流消耗的目的。clock network消耗的功耗占总功耗的很大比例,而时钟信号的无效翻转会造成多余功耗的损失,因此可以在时钟不需要翻转时使用Clock Gating电路'关闭'时钟信号翻转,节省功耗。

时钟门控的产生:

时钟门控单元时由综合工具自动生成的,能根据RTL代码风格自动生成,但需要按固定的写法才能生成门控单元,因此要想通过clock gating技术降低动态功耗,需要门控单元达到一定的覆盖率,所以对编码风格有一定要求。

always@(posedge clk)begin

if(rst)

q <= 'd0;

else if(clk_en)

q <= data_in;

else

q <= q;

end-

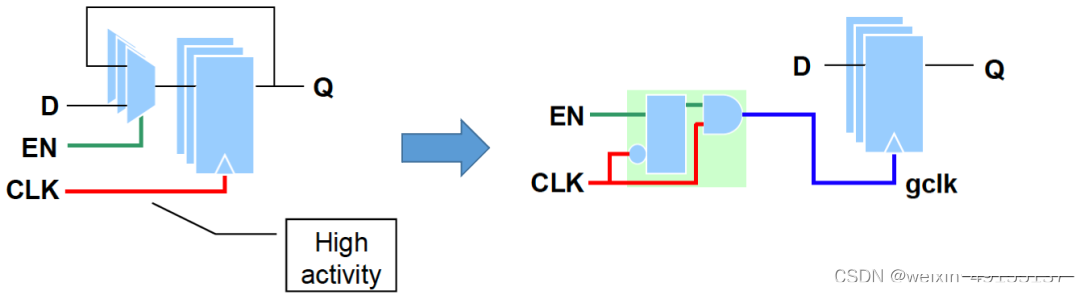

Clock Gating思路:将寄存器输入信号D和保持信号Q的选择控制信号EN变换为用来控制时钟信号,在EN有效,控制时钟信号不翻转,降低电路翻转概率。

-

-

1429

1429

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?