0x00 编码器(Encoder)

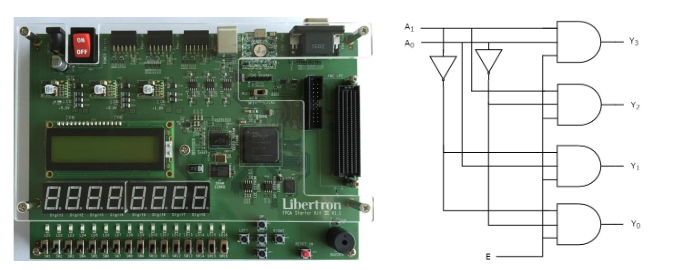

编码器与解码器相反。当多台设备向计算机提供输入时,编码器会为每一个输入生成一个与设备相对应的信号,因此有多少比特就有多少输出,以数字形式表示输入的数量。

例如,如果有四个输入,就需要一个两位二进制数来表示 0 至 3,这样就有四个输出。编码器用于转换和标准化表格或格式、提高安全性、加快处理速度或压缩数据。

编码器的应用:文件压缩 在计算机上生成视频、图像和声音等数据时,编码器用于编码和压缩数据,以减少数据量。

| 解码器 |

|

编码器与解码器相反。当多台设备向计算机提供输入时,编码器会为每一个输入生成一个与设备相对应的信号,因此有多少比特就有多少输出,以数字形式表示输入的数量。

例如,如果有四个输入,就需要一个两位二进制数来表示 0 至 3,这样就有四个输出。编码器用于转换和标准化表格或格式、提高安全性、加快处理速度或压缩数据。

编码器的应用:文件压缩 在计算机上生成视频、图像和声音等数据时,编码器用于编码和压缩数据,以减少数据量。

| 解码器 |

|

2万+

2万+

2611

2611

3020

3020

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?