0-9计数器

module cnt_0to9(clk,ov);

input clk;

output ov;

reg ov;

reg [27:0] con;

always@(posedge clk)

begin

if(con==50000000)

begin

ov<=1;

con<=0;

end

else

begin

ov<=0;

con<=con+1;

end

end

endmodule

module cnt_1to9(CNTVAL,nv,clk1);

input clk1;

output [3:0]CNTVAL;

reg [3:0]CNTVAL;

output nv;

reg nv;

reg [3:0]count;

always@(posedge clk1)

begin

if(count==9)

begin

nv=1;

end

else

begin

count=count+1;

nv=0;

end

CNTVAL=count;

end

endmodule

module yima(in,out);

input[3:0] in;

output[7:0] out;

reg[7:0] out;

always@(in)

begin

case(in)

4'b0000:out=8'b11000000;

4'b0001:out=8'b11111001;

4'b0010:out=8'b10100100</

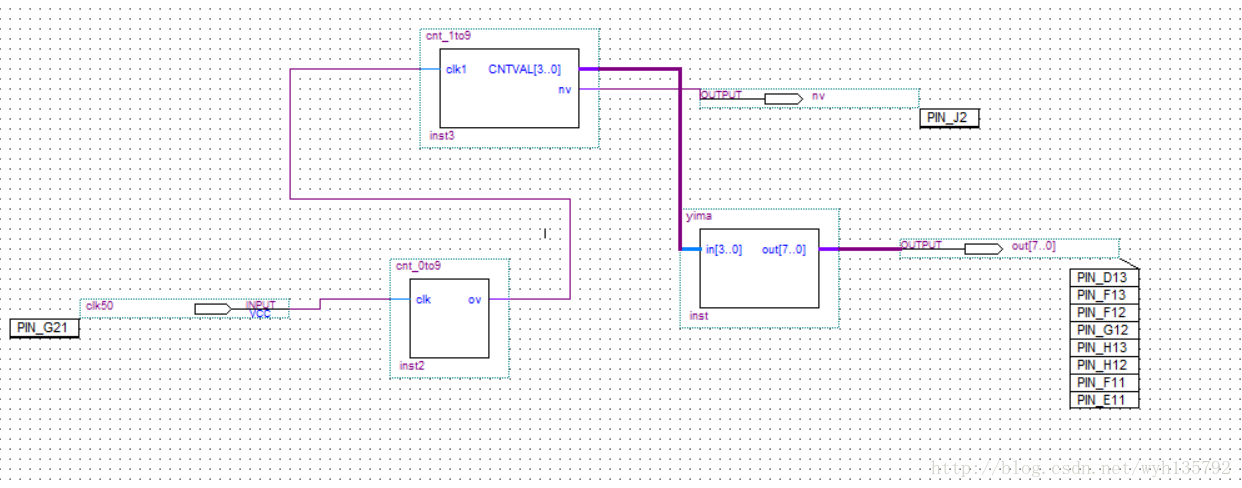

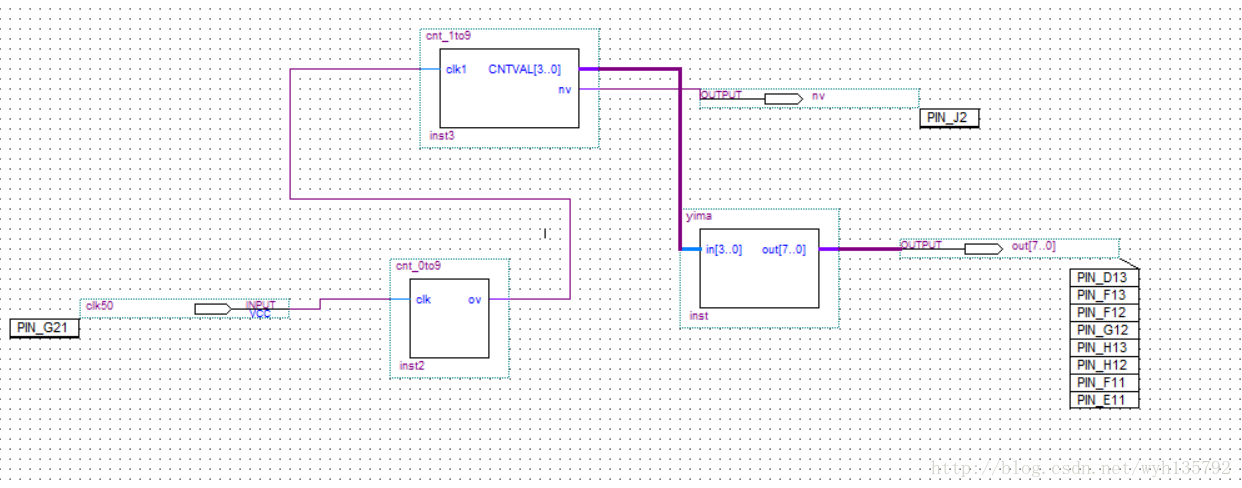

这篇博客主要介绍了如何使用Verilog设计0-9和0-15计数器,其中在0-9计数时,当达到9时会产生一个高电平信号。此外,还探讨了设计0-17计数器的方法,当计数在0-9时ov输出0,10-17时ov输出1。文章包括RTL视图、内部框图及波形仿真的详细内容。

这篇博客主要介绍了如何使用Verilog设计0-9和0-15计数器,其中在0-9计数时,当达到9时会产生一个高电平信号。此外,还探讨了设计0-17计数器的方法,当计数在0-9时ov输出0,10-17时ov输出1。文章包括RTL视图、内部框图及波形仿真的详细内容。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

536

536

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?