名称:Quartus同步FIFO设计verilog代码仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

同步FIFO设计

内容及要求

完成3bit宽、360深的同步FIFO。

(1)存储器可以采用片内SRAM或者用触发器替代;

(2)输入数据片内生成,输出侧由ISA时序读操作进行

(3)满、空指示驱动LED;

(4)SRAM双口

(5)读写信号同步于工作时钟,工作时钟100M

(6)使用实验室的开发箱或自备开发板完成设计;

(7)完成全部流程:设计规范文档、模块设计、代码输入、功能仿真、约束与综合、时序仿真、

载验证等

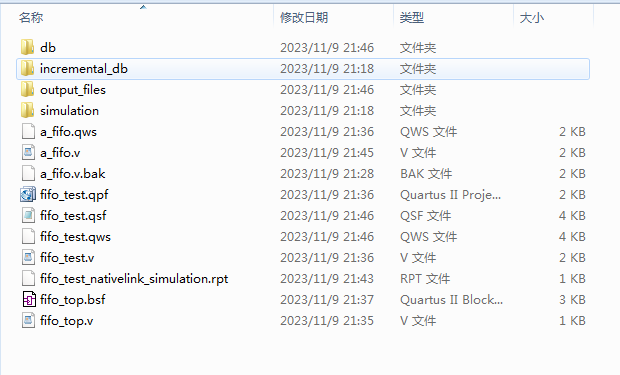

1. 工程文件

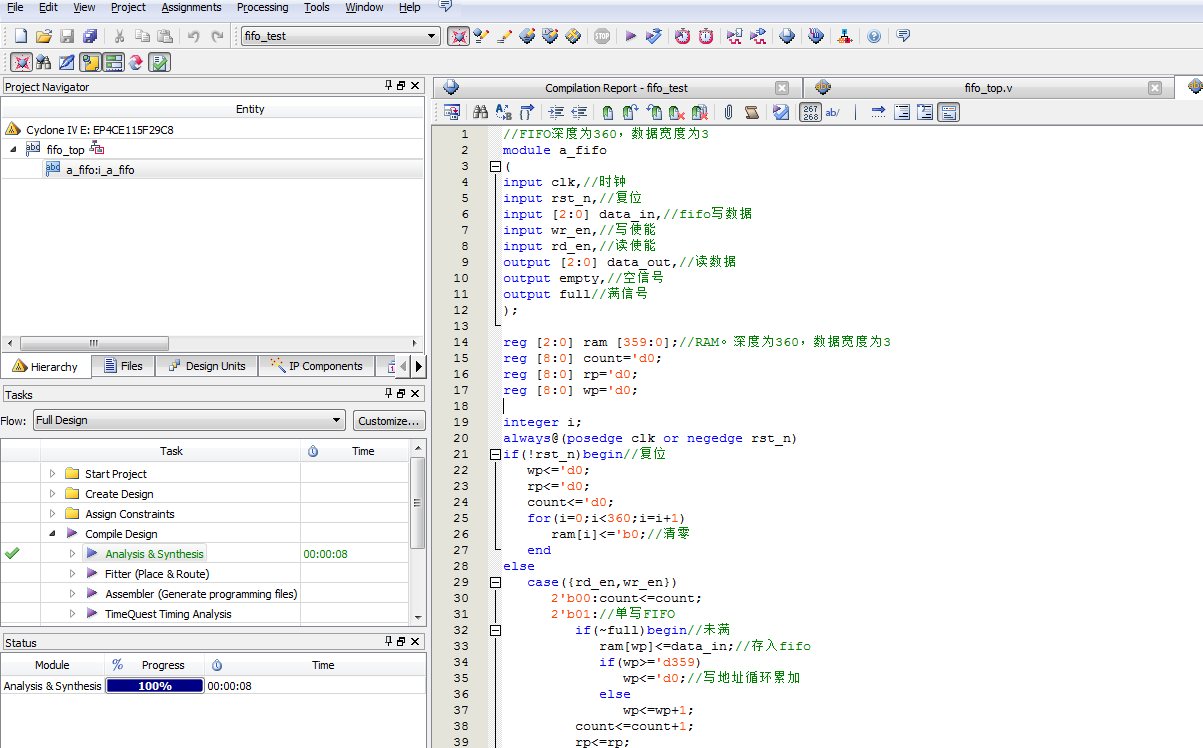

2. 程序文件

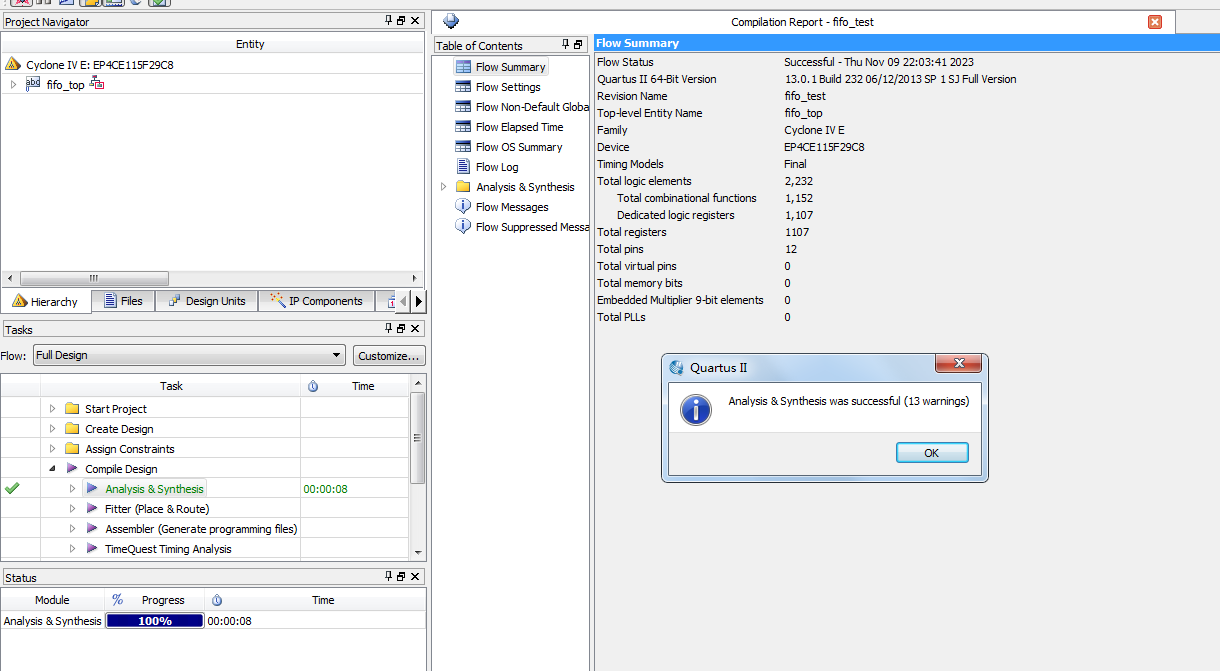

3. 程序编译

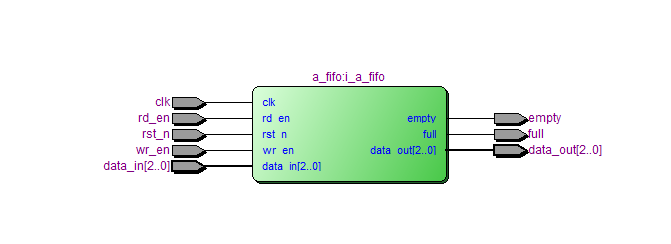

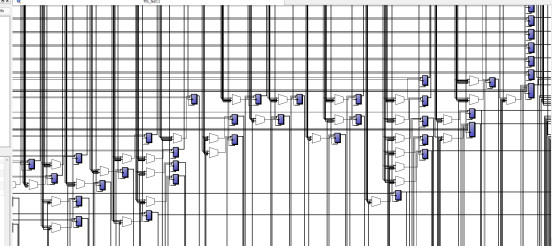

4. RTL图

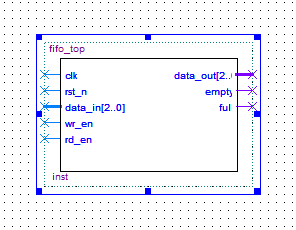

5. 模块图

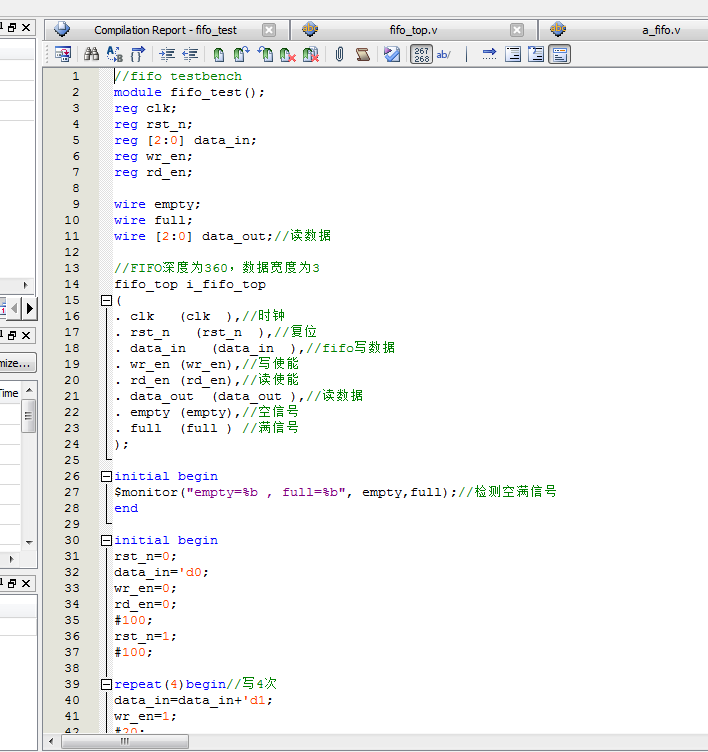

6. Testebnch

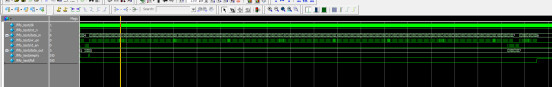

7. 仿真图

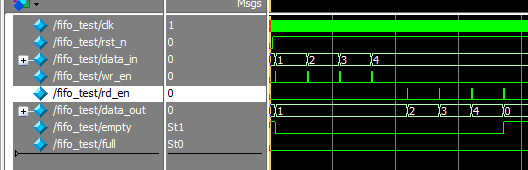

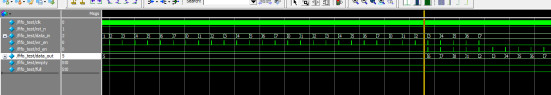

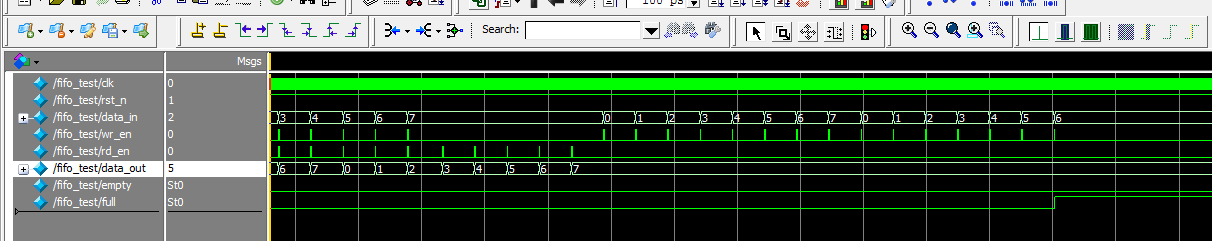

仿真图依次仿真了如下功能:

具体功能1/2/3对应如下:

1.写FIFO 4次,再读4次,FIFO读空

2.写FIFO 350次,然后同时读写5次,最后读5次,FIFO剩余345个空间

3.连续写FIFO 15次,FIFO写满

部分代码展示:

//fifo testbench

module fifo_test();

reg clk;

reg rst_n;

reg [2:0] data_in;

reg wr_en;

reg rd_en;

wire empty;

wire full;

wire [2:0] data_out;//读数据

//FIFO深度为360,数据宽度为3

fifo_top i_fifo_top

(

. clk (clk ),//时钟

. rst_n (rst_n ),//复位

. data_in (data_in ),//fifo写数据

. wr_en (wr_en),//写使能

. rd_en (rd_en),//读使能

. data_out (data_out ),//读数据

. empty (empty),//空信号

. full (full ) //满信号

);

initial begin

$monitor("empty=%b , full=%b", empty,full);//检测空满信号

end

initial begin

rst_n=0;

data_in='d0;

wr_en=0;

rd_en=0;

#100;

rst_n=1;

#100;

repeat(4)begin//写4次

data_in=data_in+'d1;

wr_en=1;

#20;

wr_en=0;

#1000;

end

#100;

repeat(4)begin//读4次

rd_en=1;

#20;

rd_en=0;

#1000;

end

repeat(350)begin//写350次

data_in=data_in+'d1;

wr_en=1;

#20;

wr_en=0;

#1000;

end

repeat(5)begin//读写5次

data_in=data_in+'d1;

wr_en=1;

rd_en=1;

#20;

wr_en=0;

rd_en=0;

#1000;

end

#100;

repeat(5)begin//读5次

rd_en=1;

#20;

rd_en=0;

#1000;

end

repeat(15)begin//写15次

data_in=data_in+64'd1;

wr_en=1;

#20;

wr_en=0;

#1000;

end

end

//产生时钟

always begin

clk=1;

#10;

clk=0;

#10;

end

endmodule

完整代码

扫描文章末尾的公众号二维码

本文详细介绍了在Quartus环境下使用Verilog语言设计3bit宽、360深的同步FIFO,涉及存储器选择、双口SRAM、同步时钟、LED指示、功能仿真等内容,包括写入、读取测试和满/空状态验证。

本文详细介绍了在Quartus环境下使用Verilog语言设计3bit宽、360深的同步FIFO,涉及存储器选择、双口SRAM、同步时钟、LED指示、功能仿真等内容,包括写入、读取测试和满/空状态验证。

879

879

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?