名称:误码率测试仪Verilog代码vivado仿真(文末获取)

软件:vivado

语言:Verilog

代码功能:

误码率测试仪

包含模块:

1、锁相环

2、M序列生成模块

3、数据接口模块

4、模拟信道模块(没有实信道,所以收发模块预留,中间加了一个误码插入模块)

5、本地M序列生成模块

6、同步模块

7、误码统计模块

8、显示模块

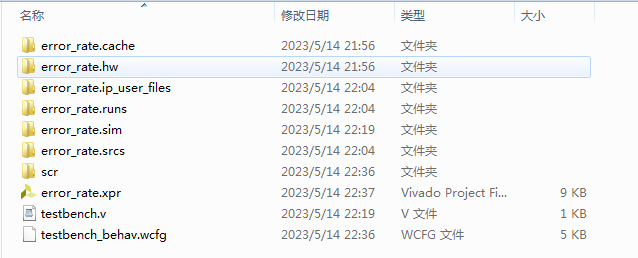

1. 工程文件

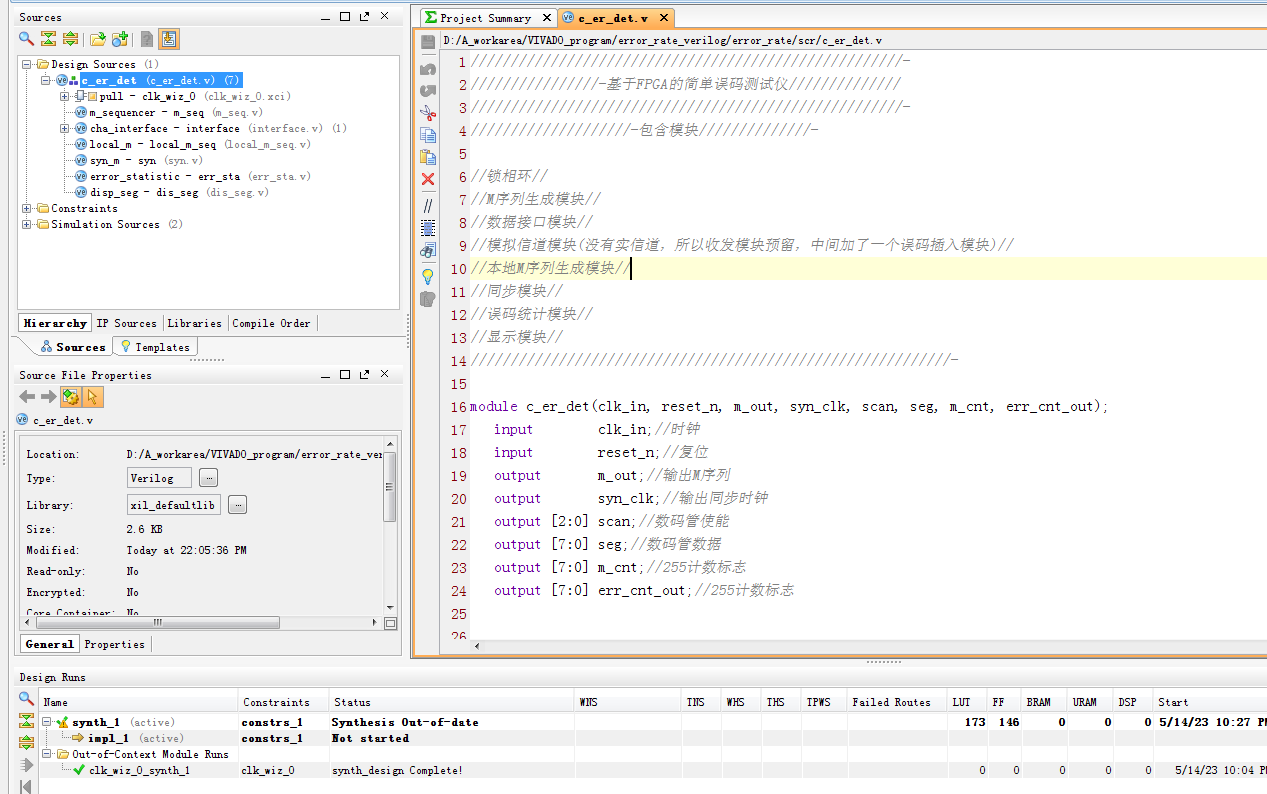

2. 程序文件

3. 程序编译

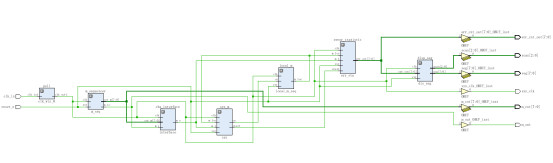

4. RTL图

5. Testbench

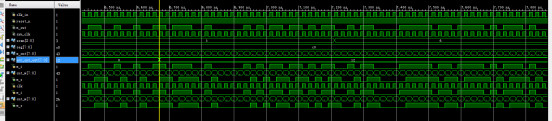

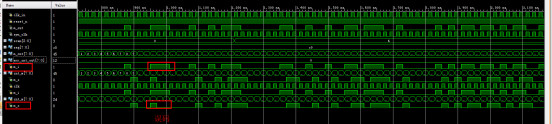

6. 仿真图

整体仿真图

锁相环

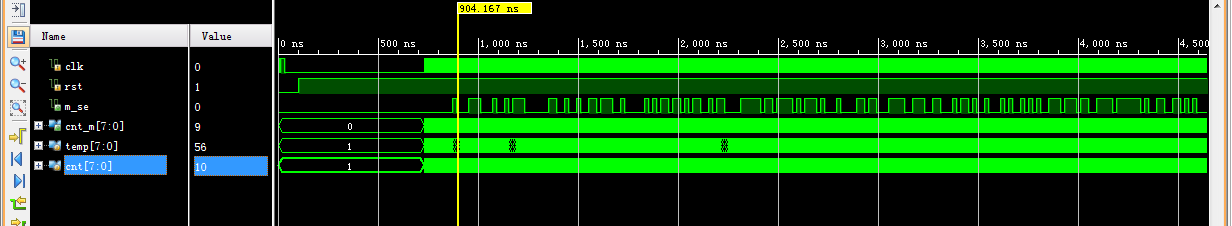

M序列生成模块

数据接口模块

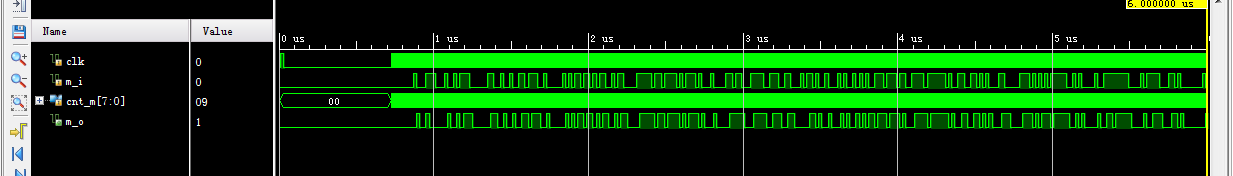

模拟信道模块

本地M序列生成模块

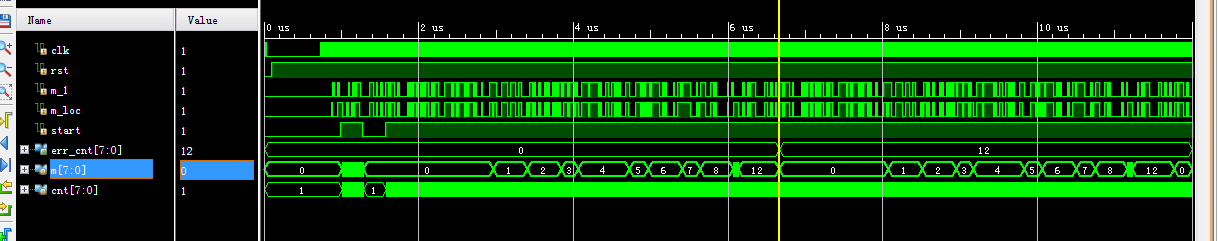

同步模块

误码统计模块

显示模块

部分代码展示:

module testbench(); reg clk_in;//时钟 reg reset_n;//复位 wire m_out;//输出M序列 wire syn_clk;//输出同步时钟 wire [2:0] scan;//数码管使能 wire [7:0] seg;//数码管数据 wire [7:0] m_cnt;//255计数标志 wire [7:0] err_cnt_out;//255计数标志 c_er_det i_c_er_det( . clk_in (clk_in ),//时钟 . reset_n (reset_n ),//复位 . m_out (m_out ),//输出M序列 . syn_clk (syn_clk ),//输出同步时钟 . scan (scan ),//数码管使能 . seg (seg ),//数码管数据 . m_cnt (m_cnt ),//255计数标志 . err_cnt_out(err_cnt_out)//255计数标志\ ); //复位 initial begin reset_n=0; #100; reset_n=1; end //产生时钟 always begin clk_in=0; #10; clk_in=1; #10; end endmodule

源代码

扫描文章末尾的公众号二维码

本文详细介绍了使用Verilog语言在Vivado环境下开发的误码率测试仪,涉及锁相环、M序列生成模块、数据接口等关键模块的代码,并展示了Testbench的实现。仿真图和部分代码展示有助于理解和应用。

本文详细介绍了使用Verilog语言在Vivado环境下开发的误码率测试仪,涉及锁相环、M序列生成模块、数据接口等关键模块的代码,并展示了Testbench的实现。仿真图和部分代码展示有助于理解和应用。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?