名称:在点阵上显示自己的名字Verilog代码Vivado仿真(文末获取)

软件:Vivado

语言:Verilog

代码功能:

在点阵上显示自己的名字

1、实验任务

在16x16点阵上,编写 Verilog程序实现循环显示你自己的“名字”的汉字。2、实验结果与现象

在点阵模块上循环依次显示你自己的“名字”,每个汉字显示的时间约为0.5秒3、问题与思考

(1)怎样让汉字左旋转和右旋转

(2)怎样让汉字左移动和右移动。

(3) Verilog程序中哪部分,影响每一列的显示时间?

(4) Verilog程序中哪部分,影响每一个字的显示时间?

1. 点阵显示汉字

工程文件

程序文件

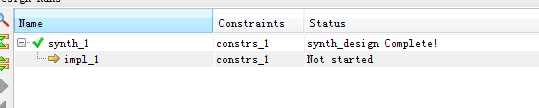

程序编译

Testbench

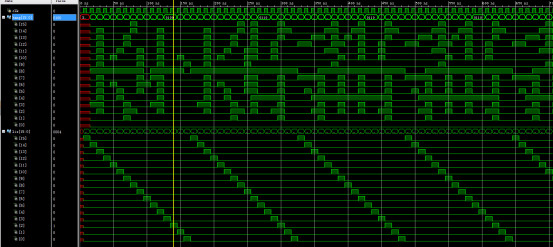

仿真图

字模软件介绍

部分代码展示:

//滚动显示"李维涛" module led_16X16( input clk,//时钟100Hz output reg [15:0] hang,//点阵行信号 output reg [15:0] lie //点阵列信号 ); //汉字3--涛 reg [15:0] word3_1= 16'h0080; reg [15:0] word3_2= 16'h4088; reg [15:0] word3_3= 16'h37FC; reg [15:0] word3_4= 16'h1080; reg [15:0] word3_5= 16'h83F8; reg [15:0] word3_6= 16'h6080; reg [15:0] word3_7= 16'h2FFE; reg [15:0] word3_8= 16'h0908; reg [15:0] word3_9= 16'h1108; reg [15:0] word3_10=16'h23FE; reg [15:0] word3_11=16'hE208; reg [15:0] word3_12=16'h2508; reg [15:0] word3_13=16'h2888; reg [15:0] word3_14=16'h3088; reg [15:0] word3_15=16'h2028; reg [15:0] word3_16=16'h2010; reg [15:0] word [0:47]; //字符初始化 always@(posedge clk) begin word[0]<=word1_1; word[1]<=word1_2; word[2]<=word1_3; word[3]<=word1_4; word[4]<=word1_5; word[5]<=word1_6; word[6]<=word1_7; word[7]<=word1_8; word[8]<=word1_9; word[9]<=word1_10; word[10]<=word1_11; word[11]<=word1_12; word[12]<=word1_13; word[13]<=word1_14; word[14]<=word1_15; word[15]<=word1_16; word[16]<=word2_1; word[17]<=word2_2; word[18]<=word2_3; word[19]<=word2_4; word[20]<=word2_5; word[21]<=word2_6; word[22]<=word2_7; word[23]<=word2_8; word[24]<=word2_9; word[25]<=word2_10; word[26]<=word2_11; word[27]<=word2_12; word[28]<=word2_13; word[29]<=word2_14; word[30]<=word2_15; word[31]<=word2_16; word[32]<=word3_1; word[33]<=word3_2; word[34]<=word3_3; word[35]<=word3_4; word[36]<=word3_5; word[37]<=word3_6; word[38]<=word3_7; word[39]<=word3_8; word[40]<=word3_9; word[41]<=word3_10; word[42]<=word3_11; word[43]<=word3_12; word[44]<=word3_13; word[45]<=word3_14; word[46]<=word3_15; word[47]<=word3_16; end //对clk进行分频为2Hz,即对应0.5s reg clk_1=0; integer x=0; always @(posedge clk) begin if(x==24) begin x<=0; clk_1=~clk_1;//2Hz end else x<=x+1; end //列计数 reg [3:0] lie_cnt=4'd0; always@(posedge clk) lie_cnt<=lie_cnt+4'd1; integer n=0; //16*16 always@(posedge clk) case(lie_cnt) 4'd0 :begin lie<=16'b1000000000000000; hang<=word[n]; end//显示第1行 4'd1 :begin lie<=16'b0100000000000000; hang<=word[n+1]; end//显示第2行 4'd2 :begin lie<=16'b0010000000000000; hang<=word[n+2]; end//显示第3行 4'd3 :begin lie<=16'b0001000000000000; hang<=word[n+3]; end//显示第4行 4'd4 :begin lie<=16'b0000100000000000; hang<=word[n+4]; end//显示第5行 4'd5 :begin lie<=16'b0000010000000000; hang<=word[n+5]; end//显示第6行 4'd6 :begin lie<=16'b0000001000000000; hang<=word[n+6]; end//显示第7行 4'd7 :begin lie<=16'b0000000100000000; hang<=word[n+7]; end//显示第8行 4'd8 :begin lie<=16'b0000000010000000; hang<=word[n+8]; end//显示第9行 4'd9 :begin lie<=16'b0000000001000000; hang<=word[n+9]; end//显示第10行 4'd10:begin lie<=16'b0000000000100000; hang<=word[n+10]; end//显示第11行 4'd11:begin lie<=16'b0000000000010000; hang<=word[n+11]; end//显示第12行 4'd12:begin lie<=16'b0000000000001000; hang<=word[n+12]; end//显示第13行 4'd13:begin lie<=16'b0000000000000100; hang<=word[n+13]; end//显示第14行 4'd14:begin lie<=16'b0000000000000010; hang<=word[n+14]; end//显示第15行 4'd15:begin lie<=16'b0000000000000001; hang<=word[n+15]; end//显示第16行 endcase //循环计数,滚动显示 always @(posedge clk_1) begin if(n==32) n<=0; else n<=n+16; end endmodule

源代码

扫描文章末尾的公众号二维码

6815

6815

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?