名称:基于FPGA的8位移位相加乘法器Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:8位移位相加乘法器

1. 工程文件

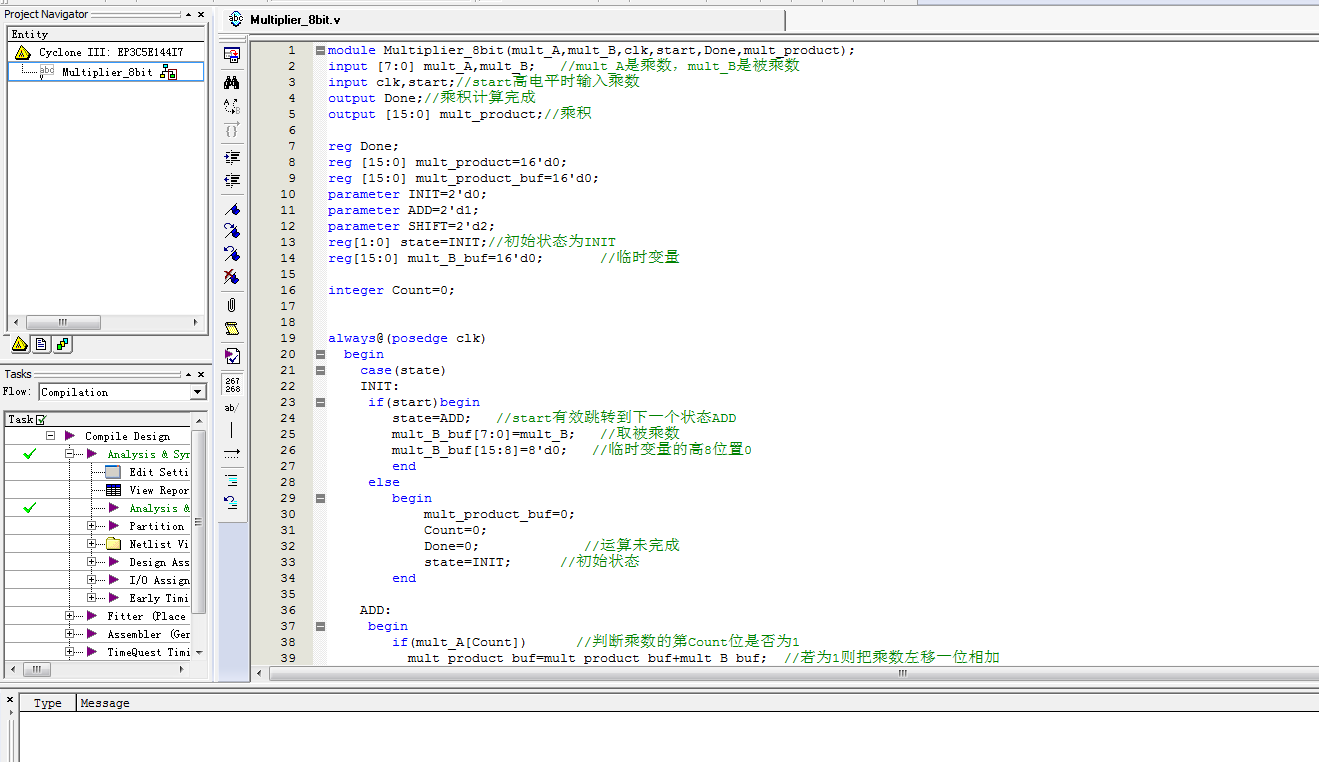

2. 程序文件

3. 程序编译

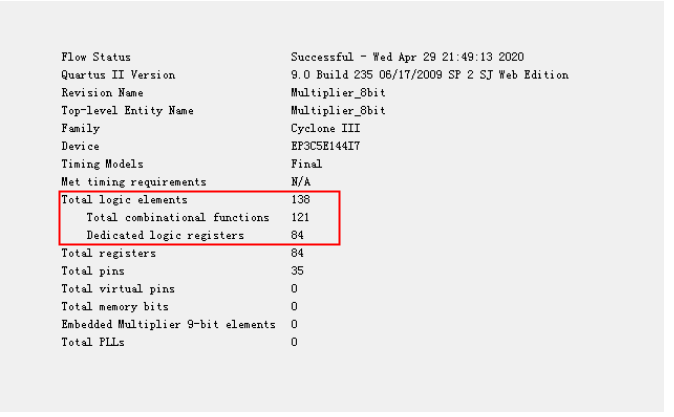

4. 资源占用

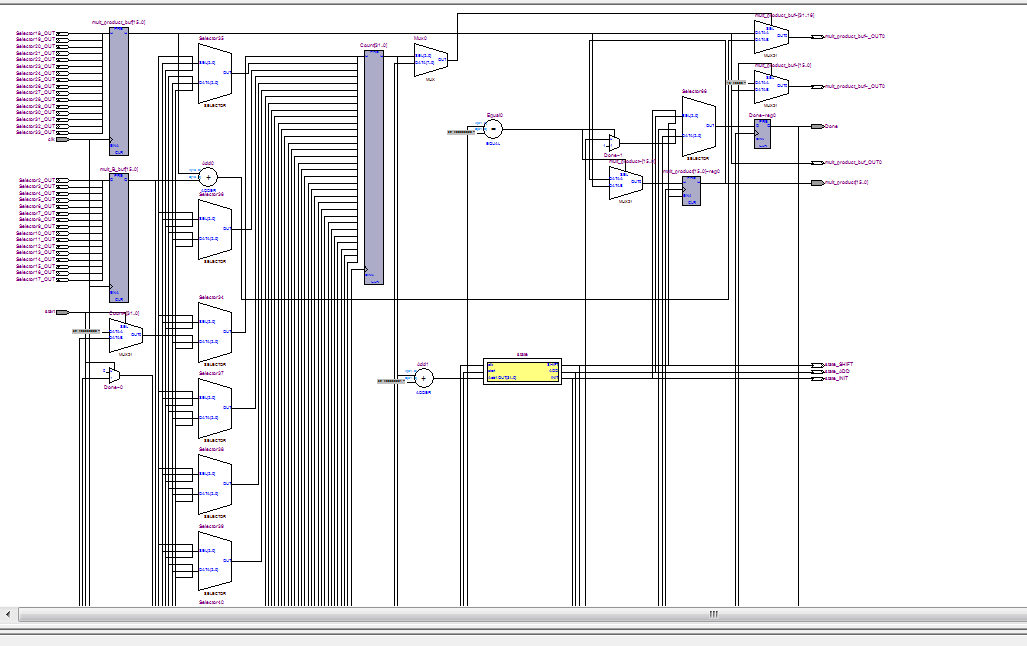

5. RTL图

6. 仿真文件

7. 仿真图

部分代码展示:

module Multiplier_8bit(mult_A,mult_B,clk,start,Done,mult_product); input [7:0] mult_A,mult_B; //mult_A是乘数,mult_B是被乘数 input clk,start;//start高电平时输入乘数 output Done;//乘积计算完成 output [15:0] mult_product;//乘积 reg Done; reg [15:0] mult_product=16'd0; reg [15:0] mult_product_buf=16'd0; parameter INIT=2'd0; parameter ADD=2'd1; parameter SHIFT=2'd2; reg[1:0] state=INIT;//初始状态为INIT reg[15:0] mult_B_buf=16'd0; //临时变量 integer Count=0; always@(posedge clk) begin case(state) INIT: if(start)begin state=ADD; //start有效跳转到下一个状态ADD mult_B_buf[7:0]=mult_B; //取被乘数 mult_B_buf[15:8]=8'd0; //临时变量的高8位置0 end

源代码

扫描文章末尾的公众号二维码

1195

1195

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?