名称:基于FPGA的8位有符号乘法器设计Verilog代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

8位有符号乘法器设计

1、输入2个8位有符号数作为乘数

2、具有清零信号

3、输出乘积,和乘法结束指示信号

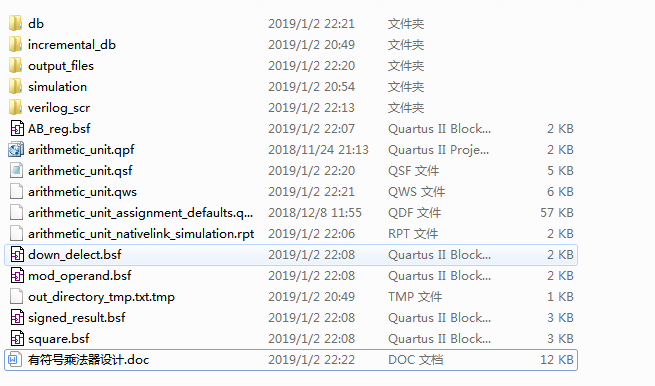

1.工程文件

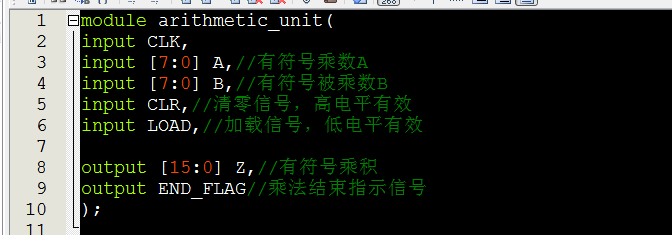

2.程序文件

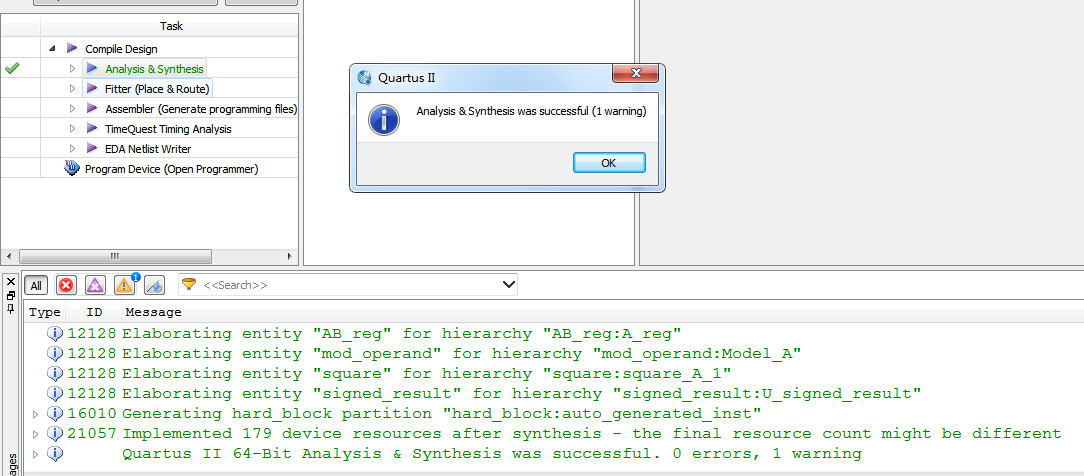

3.程序运行

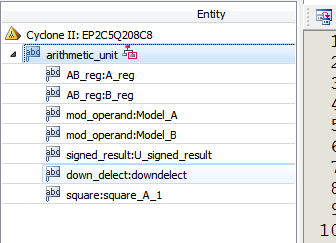

4.程序RTL图

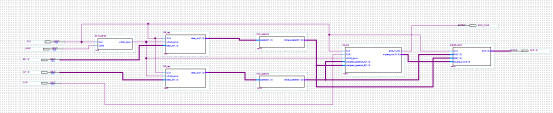

5.顶层原理图文件

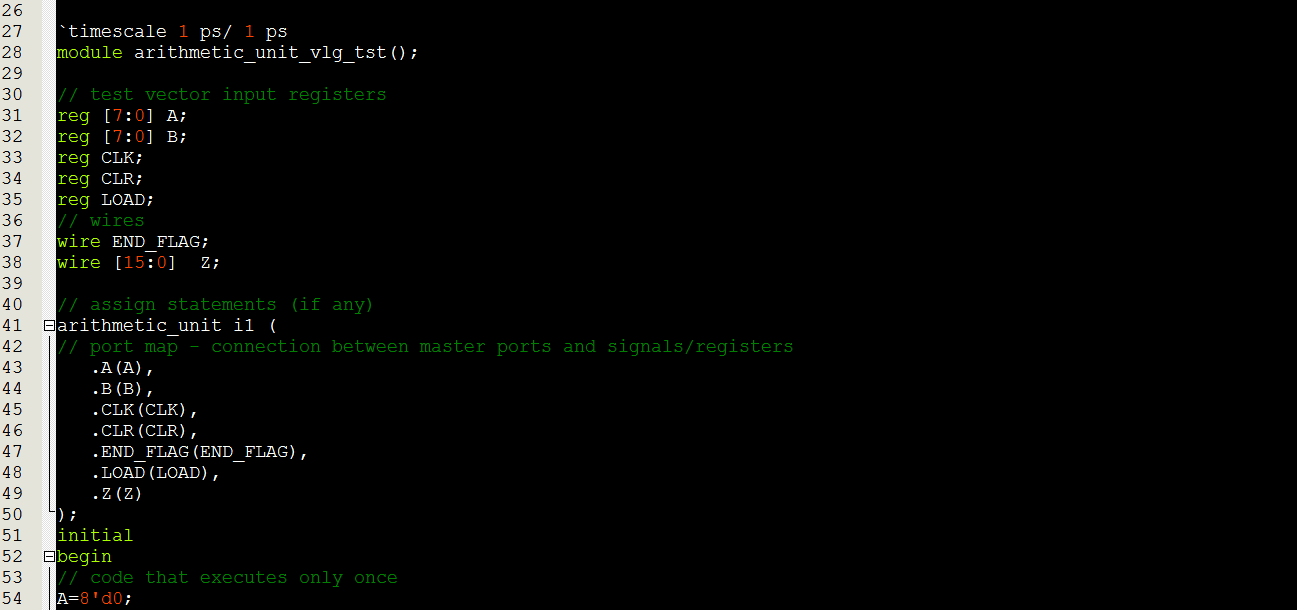

6.Testbench

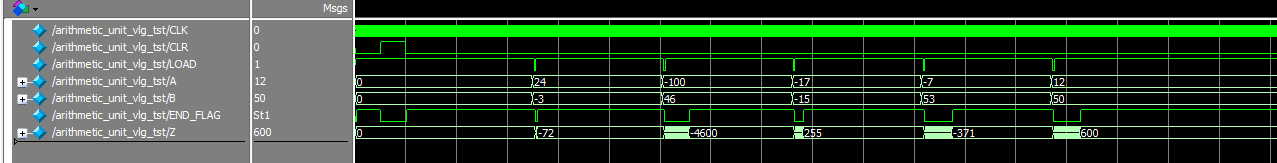

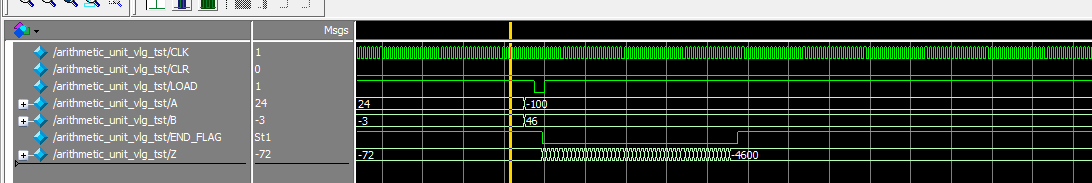

7.仿真图

部分代码展示:

input CLK, input [7:0] A,//有符号乘数A input [7:0] B,//有符号被乘数B input CLR,//清零信号,高电平有效 input LOAD,//加载信号,低电平有效 output [15:0] Z,//有符号乘积 output END_FLAG//乘法结束指示信号 ); //LOAD信号的下降沿检测模块 down_delect downdelect( . CLK(CLK), . LOAD(LOAD), . LOAD_down(LOAD_down) ); wire [7:0] RA;//寄存器 wire [7:0] RB;//寄存器 //寄存器模块 AB_reg A_reg( . CLK(CLK), . LOAD_down(LOAD_down), . data_in(A), . data_out(RA) ); //寄存器模块 AB_reg B_reg( . CLK(CLK), . LOAD_down(LOAD_down), . data_in(B), . data_out(RB) ); wire [7:0] unsigned_operand_A; wire [7:0] unsigned_operand_B; //有符号数据转换为无符号数据 mod_operand Model_A( .operand(RA), .Model_operand(unsigned_operand_A) ); //有符号数据转换为无符号数据 mod_operand Model_B( .operand(RB), .Model_operand(unsigned_operand_B) ); wire [15:0] square_out;//无符号乘积结果 square square_A_1 ( . CLK(CLK), . CLR(CLR),//清零 . LOAD_down(LOAD_down),//开始 . unsigned_operand_A(unsigned_operand_A),//A . unsigned_operand_B(unsigned_operand_B),//B . END_FLAG(END_FLAG),//结束 . square_out(square_out)//乘积 ); //无符号转换为有符号 signed_result U_signed_result( . CLK(CLK), . RA(RA), . RB(RB), . square_out(square_out), . Z(Z) ); endmodule

源代码

扫描文章末尾的公众号二维码

694

694

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?