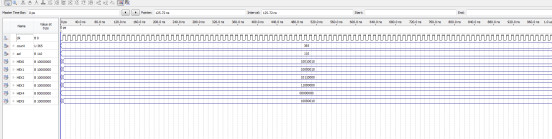

名称:基于FPGA的可变模计数器设计Verilog代码Quartus仿真(文末获取)

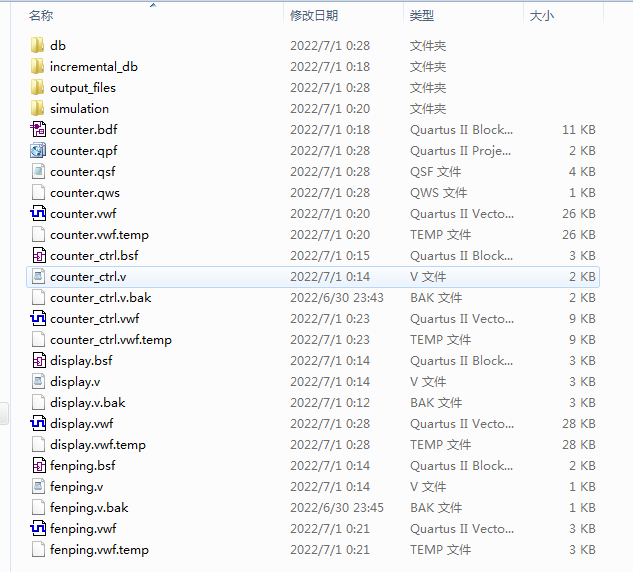

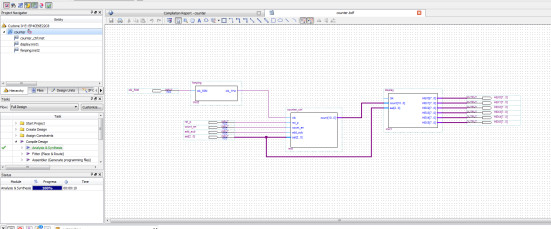

软件:Quartus

语言:Verilog

代码功能:

设计一个可变模计数器(6位数码管2位显示模式4位显示计数)

主要功能:

1.能够任意设定不同的模实现计数

2.能够暂停继续倒计时

3.能够完成常见的810121624303651024计数(独立模式)

部分代码展示:

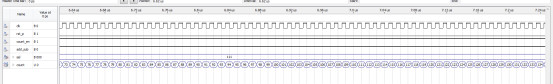

//计数控制模块 module counter_ctrl( input clk,//时钟 input rst_p,//复位 input count_en,//继续,暂停 input add_sub,//正计时还是倒计时 input [2:0] sel,//模设置 output reg [10:0] count//计数输出 ); //进制设置 reg [10:0] mode; always@(posedge clk or posedge rst_p) if(rst_p) mode<=11'd8;//默认模8进制 else case(sel)//模设置 3'd0:mode<=11'd8; 3'd1:mode<=11'd10; 3'd2:mode<=11'd12; 3'd3:mode<=11'd16; 3'd4:mode<=11'd24; 3'd5:mode<=11'd30; 3'd6:mode<=11'd365; 3'd7:mode<=11'd1024; default:; endcase always@(posedge clk or posedge rst_p) if(rst_p) count<=11'd0; else if(count_en==1)//高电平继续,低电平暂停 if(add_sub==1)//高电平表示正计时 if(count>=mode-1)//计数到最大 count<=11'd0; else count<=count+10'd1;//加计数 else 低电平表示倒计时 if(count==11'd0)//计数到最小 count<=mode-1; else count<=count-10'd1;//减计数 else //低电平暂停 count<=count; endmodule

源代码

扫描文章末尾的公众号二维码

7613

7613

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?