一种可变模计数器的设计。

目录

一、概述

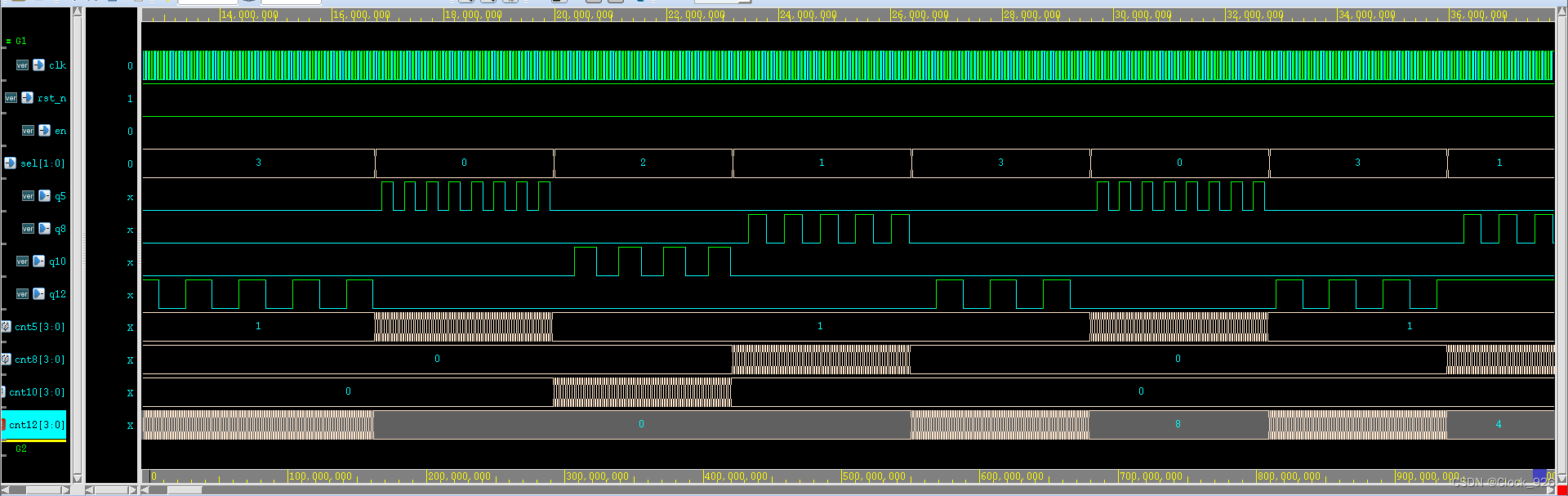

可变模长计数器是用标准计数器结合与门电路,构成任意进制计数器的方法。通过控制使能或者选择信号,实现切换不同进制计数器的功能。本次设计分别采用5进制,8进制,10进制,12进制四种模数,通过选择信号切换来实现变模计数。

二、代码实现

上代码:

module vary(

input clk,

input rst_n,

input en,

input [1:0] sel,

output reg q5,

output reg q8,

output reg q10,

output reg q12

);

reg [3:0] cnt5,cnt8,cnt10,cnt12;

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

q5 <= 0;

cnt5 <= 0;

q8 <= 0;

cnt8 <= 0;

q10 <= 0;

cnt10 <= 0;

q12 <= 0;

cnt12 <= 0;

end

else if(en)begin

case(sel)

2'b00: begin

if(cnt5 == 4'd4)begin

q5 <= ~q5;

cnt5 <= 4'd0;

end

else begin

cnt5 <= cnt5+1;

end

end

2'b01: begin

if(cnt8 == 4'd7)begin

q8 <= ~q8;

cnt8 <= 4'd0;

end

else begin

cnt8 <= cnt8+1;

end

end

2'b10: begin

if(cnt10 == 4'd9)begin

q10 <= ~q10;

cnt10 <= 4'd0;

end

else begin

cnt10 <= cnt10+1;

end

end

2'b11: begin

if(cnt12 == 4'd11)begin

q12 <= ~q12;

cnt12 <= 4'd0;

end

else begin

cnt12 <= cnt12+1;

end

end

default: begin

q5 <= q5;

q8 <= q8;

q10 <= q10;

q12 <= q12;

cnt5 <= cnt5;

cnt8 <= cnt8;

cnt10 <= cnt10;

cnt12 <= cnt12;

end

endcase

end

end

endmodule测试波形:

3719

3719

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?