名称:基于FPGA的电子计时时钟设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:

要求

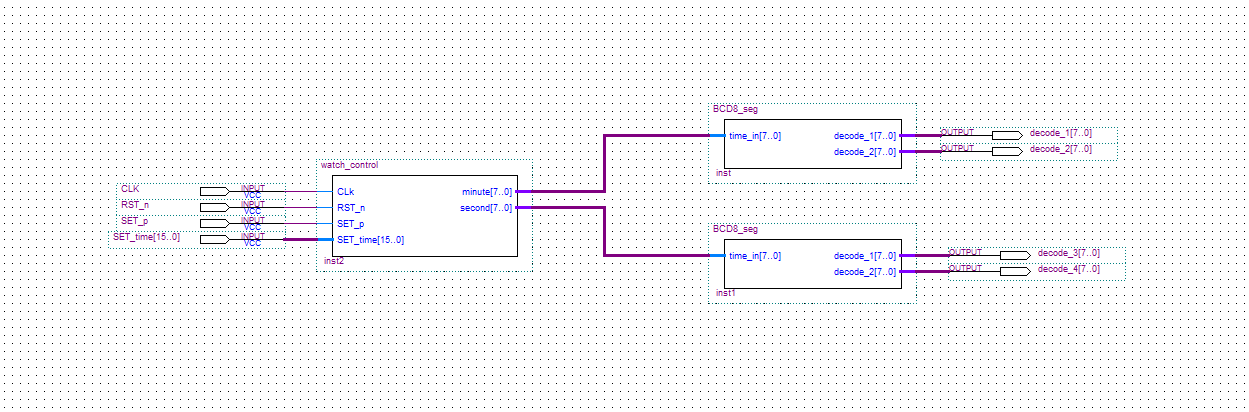

1.电子计时时钟具有异步清零、同步置数功能,用VHDL实现计数逻辑,并阐述设计原理,给出关键 block diagram设计框图。

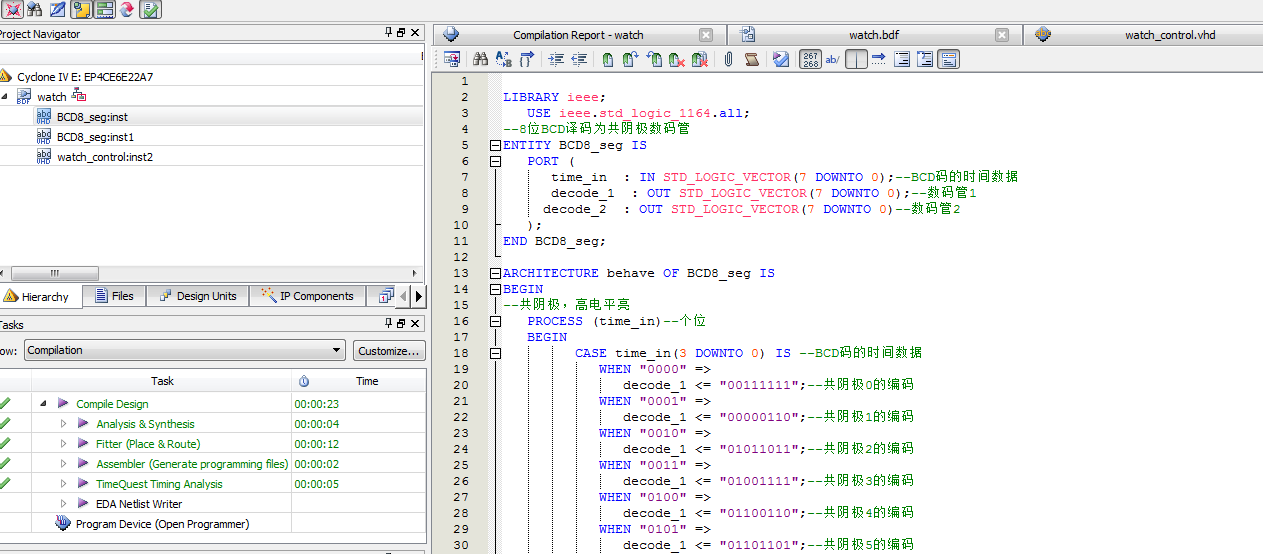

2.用VHDL实现译码显示逻辑,并阐述设计原理,给出关键 block diagran设计框图。

3.驱动的数码管为共阴极数码管,阐述电路原理,给出相应编码方式。

4.报告要求

(1)按设计指导书中要求的格式书写,所有内容一律打印

(2)报告内容包括设计过程、软件仿真的结果及分析;

(3)报告中要有整体电路原理图、各模块原理图;

(4)软件仿真包括各个模块的仿真和整体电路的仿真;

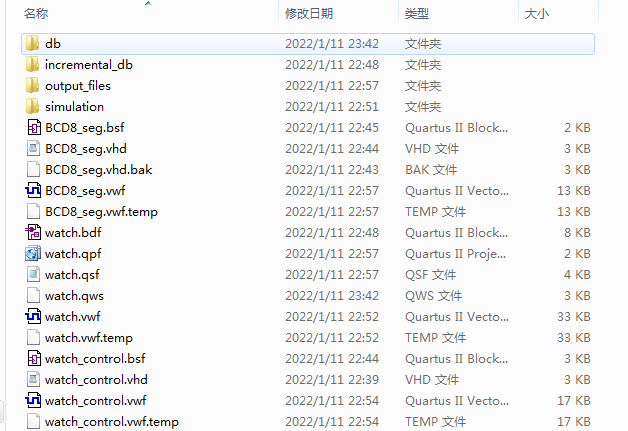

1. 工程文件

2. 程序文件

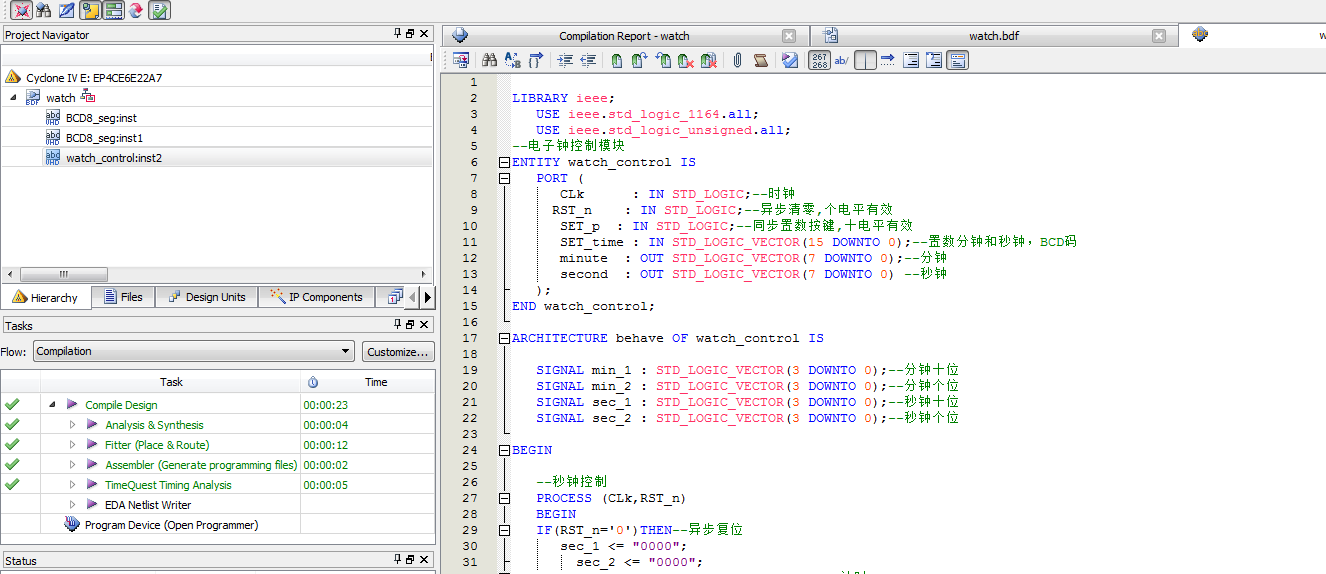

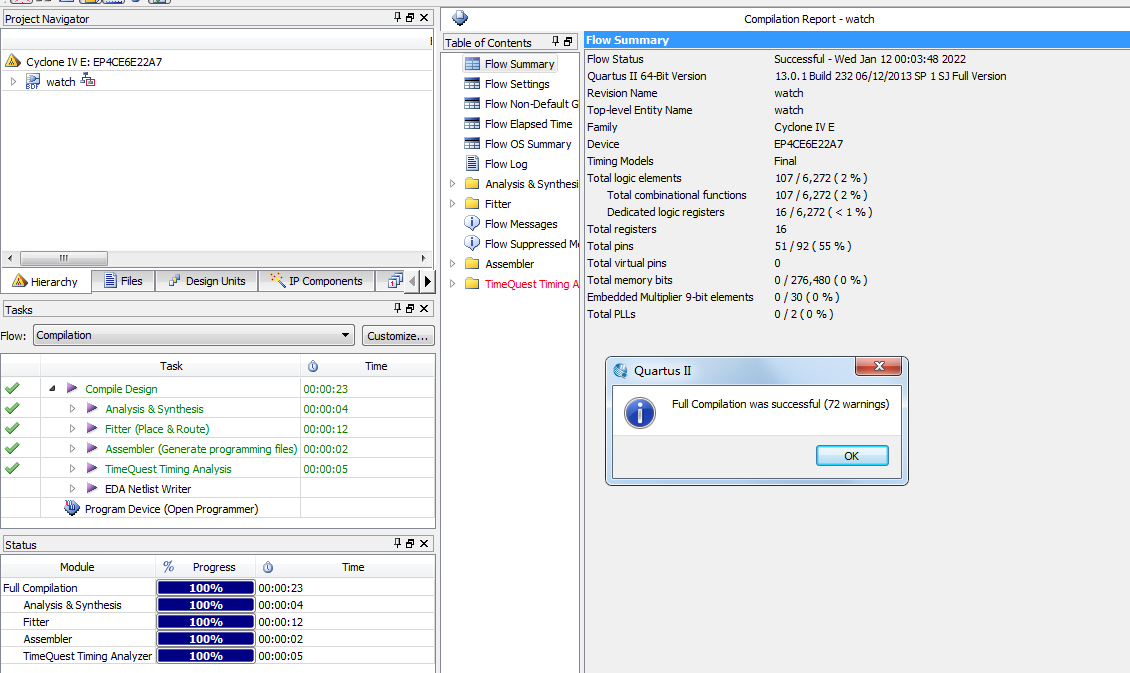

3. 程序编译

4. RTL图

5. 仿真图

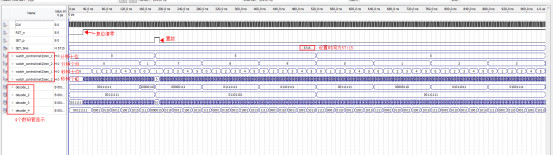

整体仿真图

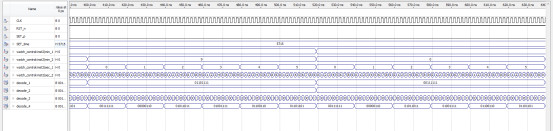

电子钟控制模块仿真图

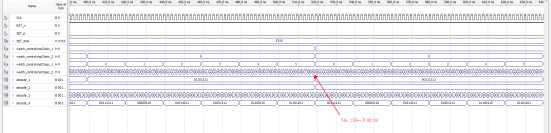

共阴极数码管译码模块仿真图

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; USE ieee.std_logic_unsigned.all; --电子钟控制模块 ENTITY watch_control IS PORT ( CLk : IN STD_LOGIC;--时钟 RST_n : IN STD_LOGIC;--异步清零,个电平有效 SET_p : IN STD_LOGIC;--同步置数按键,十电平有效 SET_time : IN STD_LOGIC_VECTOR(15 DOWNTO 0);--置数分钟和秒钟,BCD码 minute : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--分钟 second : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --秒钟 ); END watch_control; ARCHITECTURE behave OF watch_control IS SIGNAL min_1 : STD_LOGIC_VECTOR(3 DOWNTO 0);--分钟十位 SIGNAL min_2 : STD_LOGIC_VECTOR(3 DOWNTO 0);--分钟个位 SIGNAL sec_1 : STD_LOGIC_VECTOR(3 DOWNTO 0);--秒钟十位 SIGNAL sec_2 : STD_LOGIC_VECTOR(3 DOWNTO 0);--秒钟个位 BEGIN --秒钟控制 PROCESS (CLk,RST_n) BEGIN IF(RST_n='0')THEN--异步复位 sec_1 <= "0000"; sec_2 <= "0000"; ELSIF (CLk'EVENT AND CLk = '1') THEN--计时 IF(SET_p='1')THEN--同步置数 sec_1 <= SET_time(7 DOWNTO 4);--置数秒钟十位 sec_2 <= SET_time(3 DOWNTO 0);--置数秒钟个位 ELSIF (sec_1 = "0101" AND sec_2 = "1001") THEN--秒钟记到59秒后变为00 sec_1 <= "0000"; sec_2 <= "0000"; ELSIF (sec_2 = "1001") THEN--9秒 sec_1 <= sec_1 + "0001";--秒钟十位加1 sec_2 <= "0000"; ELSE

源代码

扫描文章末尾的公众号二维码

1444

1444

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?