名称:基于FPGA的带闹钟功能的数字钟设计VHDL代码Quartus仿真(文末获取)

软件:Quartus

语言:VHDL

代码功能:

数字钟

1、可以调节小时、分钟

2、可以调整闹钟时间

3、到设置的时间闹铃响

4、整点报时

控制方法:

2个拨码开关SW0和SW1控制模式:

SW0=0,SW1=0为正常计时模式;

SW0=0,SW1=1为修改时间模式;

SW0=1,SW1=0为显示闹钟时间模式;

SW0=1,SW1=1为修改闹钟时间模式;

2个按键,BT0修改小时,BT1修改分钟:

将拨码开关设置为SW0=0,SW1=1,此时可以修改当前时间;

将拨码开关设置为SW0=1,SW1=1,此时可以修改闹钟时间;

1. 工程文件

2. 程序文件

3. 程序编译

4. 程序RTL图

5. Vwf文件

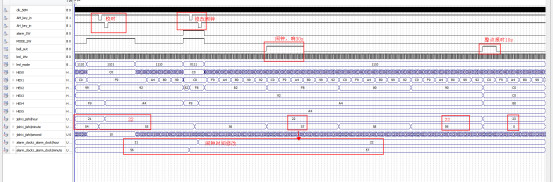

6. 仿真图

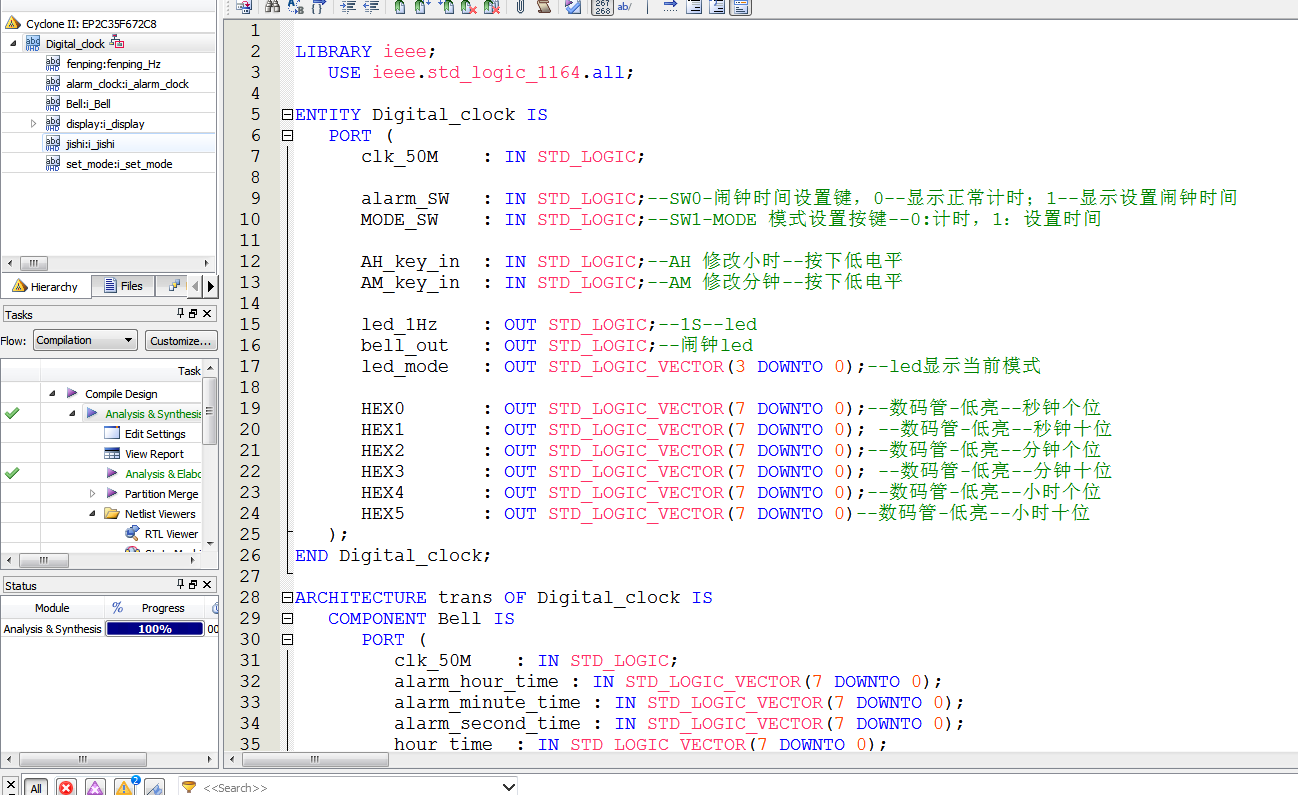

部分代码展示:

LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY Digital_clock IS PORT ( clk_50M : IN STD_LOGIC; alarm_SW : IN STD_LOGIC;--SW0-闹钟时间设置键,0--显示正常计时;1--显示设置闹钟时间 MODE_SW : IN STD_LOGIC;--SW1-MODE 模式设置按键--0:计时,1:设置时间 AH_key_in : IN STD_LOGIC;--AH 修改小时--按下低电平 AM_key_in : IN STD_LOGIC;--AM 修改分钟--按下低电平 led_1Hz : OUT STD_LOGIC;--1S--led bell_out : OUT STD_LOGIC;--闹钟led led_mode : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);--led显示当前模式 HEX0 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管-低亮--秒钟个位 HEX1 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --数码管-低亮--秒钟十位 HEX2 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管-低亮--分钟个位 HEX3 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --数码管-低亮--分钟十位 HEX4 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--数码管-低亮--小时个位 HEX5 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0)--数码管-低亮--小时十位 ); END Digital_clock; ARCHITECTURE trans OF Digital_clock IS COMPONENT Bell IS PORT ( clk_50M : IN STD_LOGIC; alarm_hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); bell_out : OUT STD_LOGIC ); END COMPONENT; COMPONENT alarm_clock IS PORT ( clk_50M : IN STD_LOGIC; state_mode : IN STD_LOGIC_VECTOR(3 DOWNTO 0); AH_key : IN STD_LOGIC; AM_key : IN STD_LOGIC; alarm_hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; COMPONENT display IS PORT ( clk : IN STD_LOGIC; state_mode : IN STD_LOGIC_VECTOR(3 DOWNTO 0); alarm_hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); alarm_second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); hour_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : IN STD_LOGIC_VECTOR(7 DOWNTO 0); HEX0 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX1 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX2 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX3 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX4 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); HEX5 : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT; COMPONENT set_mode IS PORT ( clk_50M : IN STD_LOGIC; alarm_SW : IN STD_LOGIC; MODE_SW : IN STD_LOGIC; led_mode : OUT STD_LOGIC_VECTOR(3 DOWNTO 0); state_mode : OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END COMPONENT; COMPONENT fenping IS PORT ( clk_50M : IN STD_LOGIC; led_1Hz : OUT STD_LOGIC; clk_1Hz : OUT STD_LOGIC ); END COMPONENT; COMPONENT jishi IS PORT ( clk_50M : IN STD_LOGIC; clk_1Hz : IN STD_LOGIC; state_mode : IN STD_LOGIC_VECTOR(3 DOWNTO 0); AH_key : IN STD_LOGIC; AM_key : IN STD_LOGIC; hour_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); minute_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0); second_time : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END COMPONENT;

源代码

扫描文章末尾的公众号二维码

1360

1360

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?