名称:基于FPGA的32位补码除法器设计Verilog代码ISE仿真(文末获取)

软件:Quartus

语言:Verilog

代码功能:32位补码除法器设计

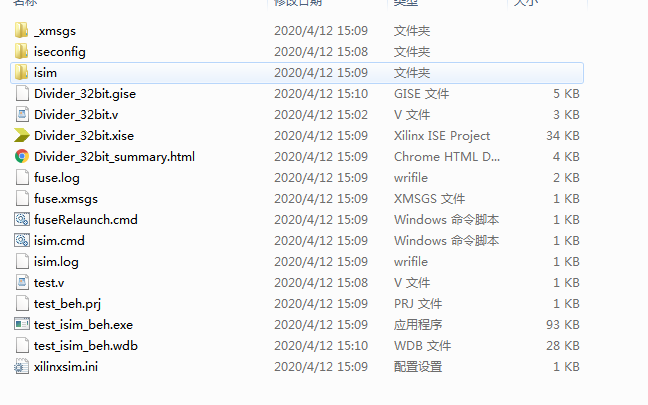

1. 工程文件

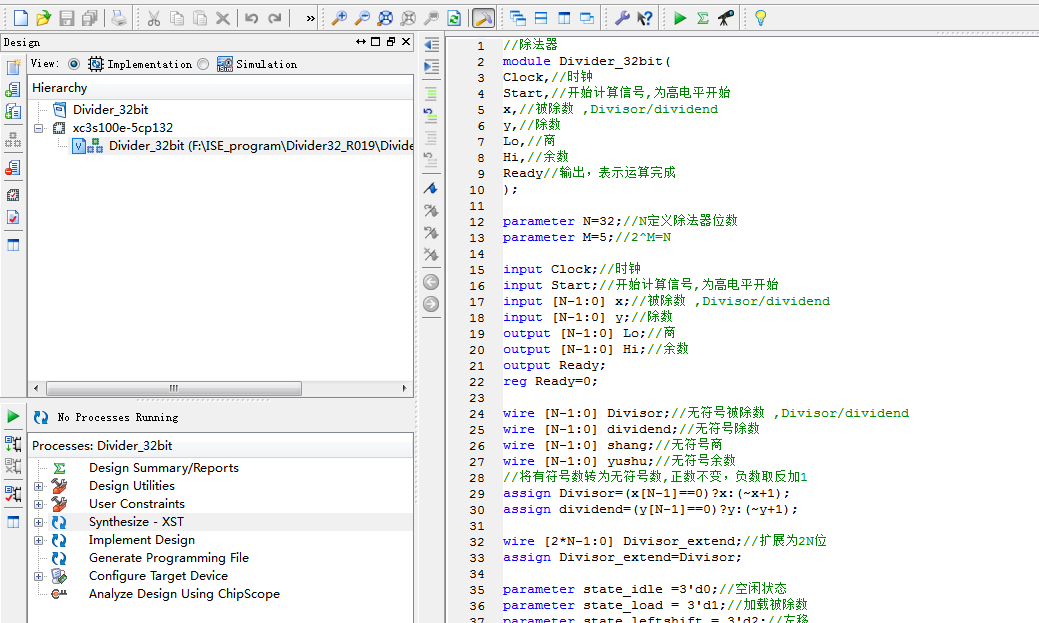

2. 程序文件

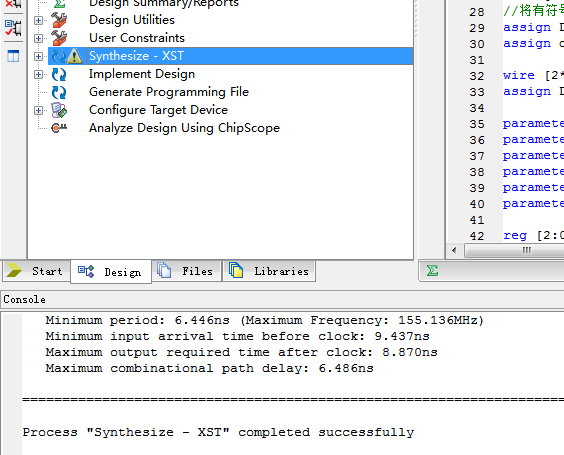

3. 程序编译

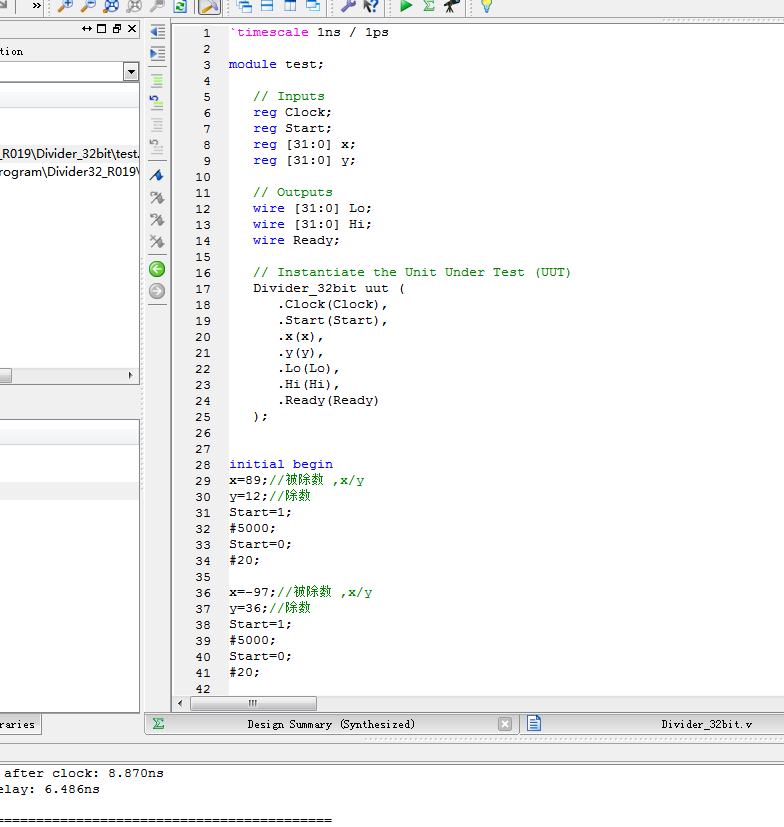

4. Testbench

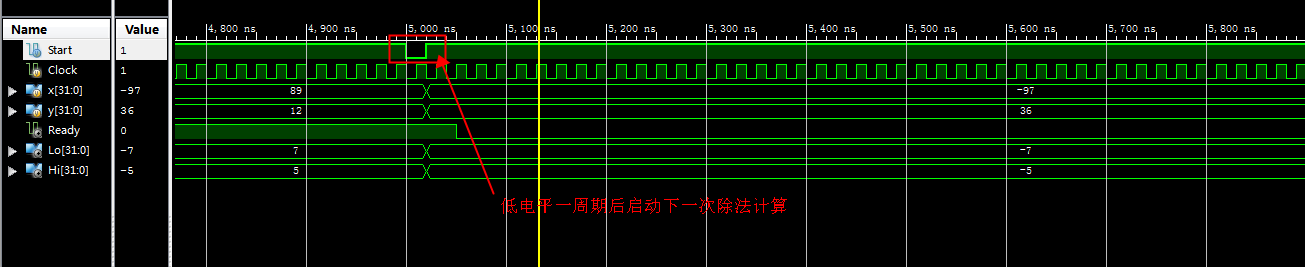

5. 仿真图

用有符号十进制显示:

可以看到:

89除以12等于7余数5;

-97除以36等于-2余数-25;

72除以-8等于-9余数0;

-85除以-37等于2余数-11;

89除以-5等于-17余数4;

部分代码展示:

//除法器

module Divider_32bit(

Clock,//时钟

Start,//开始计算信号,为高电平开始

x,//被除数 ,Divisor/dividend

y,//除数

Lo,//商

Hi,//余数

Ready//输出,表示运算完成

);

parameter N=32;//N定义除法器位数

parameter M=5;//2^M=N

input Clock;//时钟

input Start;//开始计算信号,为高电平开始

input [N-1:0] x;//被除数 ,Divisor/dividend

input [N-1:0] y;//除数

output [N-1:0] Lo;//商

output [N-1:0] Hi;//余数

output Ready;

reg Ready=0;

wire [N-1:0] Divisor;//无符号被除数 ,Divisor/dividend

wire [N-1:0] dividend;//无符号除数

wire [N-1:0] shang;//无符号商

wire [N-1:0] yushu;//无符号余数

//将有符号数转为无符号数,正数不变,负数取反加1

assign Divisor=(x[N-1]==0)?x:(~x+1);

assign dividend=(y[N-1]==0)?y:(~y+1);

wire [2*N-1:0] Divisor_extend;//扩展为2N位

assign Divisor_extend=Divisor;

parameter state_idle =3'd0;//空闲状态

parameter state_load = 3'd1;//加载被除数

parameter state_leftshift = 3'd2;//左移

parameter state_judge = 3'd3;//判断高位是否大于除数

parameter state_sub = 3'd4;//减去

parameter state_end = 3'd5;//结束

reg [2:0] state=3'd0;

reg [2*N-1:0] data=16'd0;

reg [M-1:0] shift_cnt='d0;//移位次数累计

reg [N-1:0] shang_reg=8'd0;//商

reg [N-1:0] yushu_reg=8'd0;//余数

always@(posedge Clock)

case(state)

state_idle:begin

shift_cnt<='d0;

if(Start==1)//加载被除数

state<=state_load;

else

state<=state_idle;

end

state_load:begin

data<=Divisor_extend;//加载被除数

state<=state_leftshift;

shift_cnt<='d0;

end

state_leftshift:begin

shift_cnt<=shift_cnt+'d1;//移位次数累计

data<={data[2*N-2:0],1'b0};//左移

state<=state_judge;

、

源代码

扫描文章末尾的公众号二维码

907

907

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?