名称:基于FPGA的交通灯设计Verilog代码ISE basys2开发板(文末获取)

软件:ISE

语言:Verilog

代码功能:

简易交通灯设计

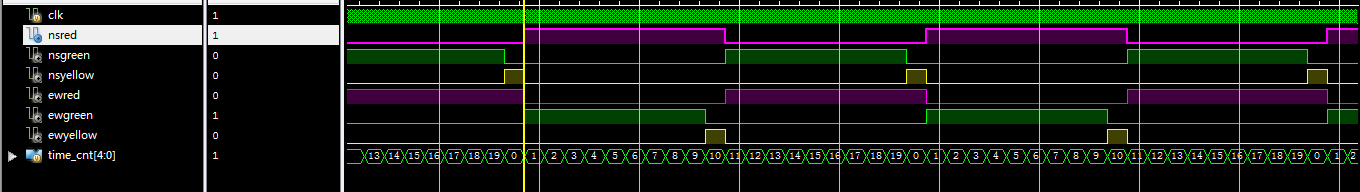

十字路口交通灯:红灯10s,黄灯1秒,绿灯9秒

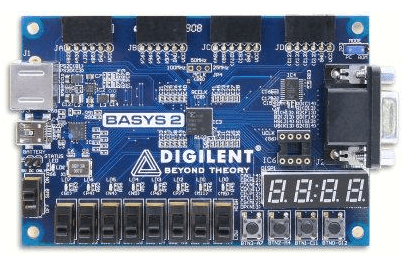

本代码已在basys2开发板验证,basys2开发板如下,其他开发板可以修改管脚适配:

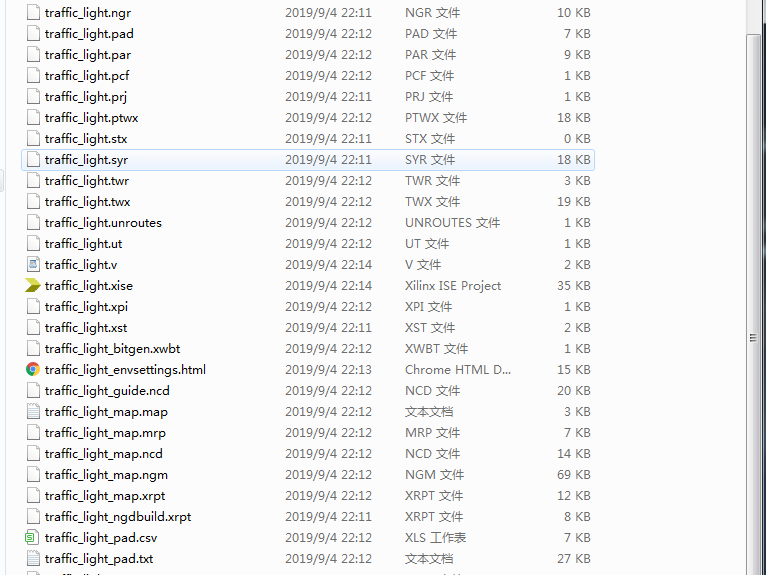

1. 工程文件

2. 程序文件

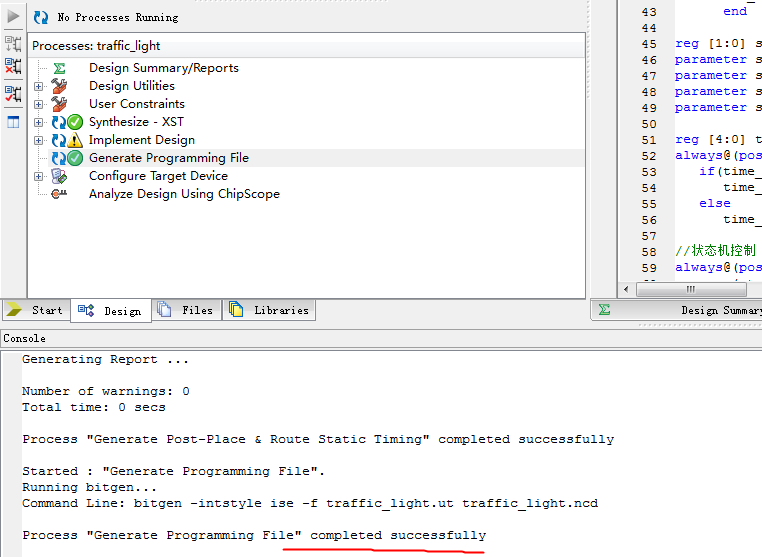

3. 程序编译

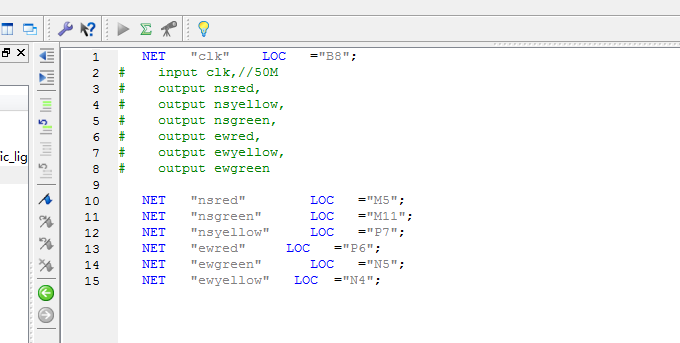

4. 管脚约束

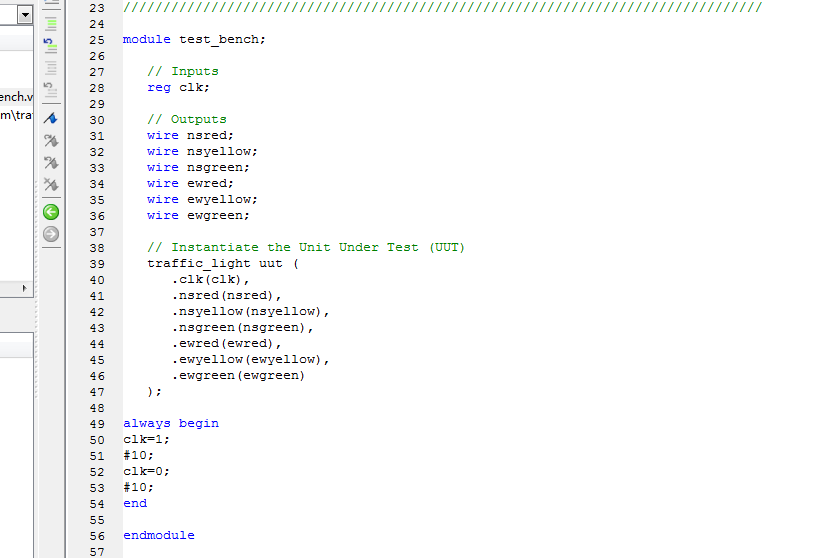

5. Testbench

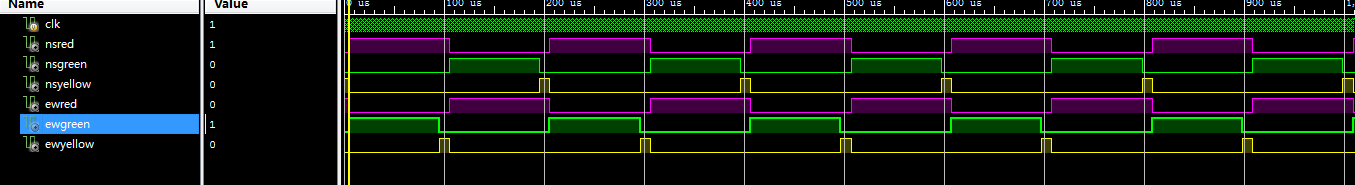

6. 仿真图

部分代码展示:

`timescale 1ns / 1ps // // Company: // Engineer: // // Create Date: 21:12:41 09/04/2019 // Design Name: // Module Name: traffic_light // Project Name: // Target Devices: // Tool versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // BASYS2 // //红灯10s,黄灯1秒,绿灯9秒 module traffic_light( input clk,//50M output reg nsred, output reg nsyellow, output reg nsgreen, output reg ewred, output reg ewyellow, output reg ewgreen ); //50M分频到1Hz reg [31:0] cnt='d0; reg clk_1hz=0;//1Hz时钟信号 always@(posedge clk) if(cnt==32'd25_000_000) begin//分频50_000_000,得1HZ cnt<=32'd0; clk_1hz<=~clk_1hz; end else begin cnt<=cnt+32'd1; clk_1hz<=clk_1hz; end reg [1:0] state=2'd0; parameter s_nsyellow=2'd0; parameter s_nsgreen=2'd1; parameter s_ewyellow=2'd2; parameter s_ewgreen=2'd3; reg [4:0] time_cnt=5'd0;//时间计数器,1s计数一次 always@(posedge clk_1hz) if(time_cnt>=5'd19)//红灯10s,黄灯1秒,绿灯9秒,一个周期20s time_cnt<=5'd0; else time_cnt<=time_cnt+5'd1;

源代码

扫描文章末尾的公众号二维码

988

988

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?