名称:上课作息时间打铃器设计Verilog代码VIVADO仿真(文末获取)

软件:VIVADO

语言:Verilog

代码功能:

在 Vivado软件中设计一个面向学校上课作息时间的打铃器。具体要求如下基本功能

1.按照学校上课作息时间点定时打铃,每次打铃时长5秒。

2.具备电子钟的功能,能够完成24小时、60分和和60秒的计时。

3电子钟走时不准确时,可对时和分进行调整。

4用数码管显示小时和分钟的计时值。

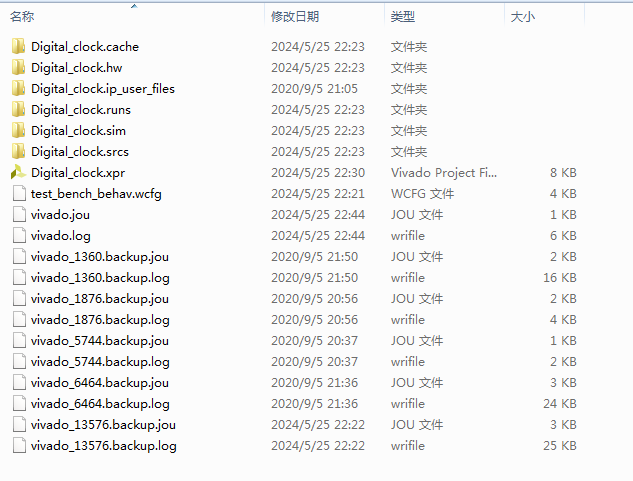

1. 工程文件

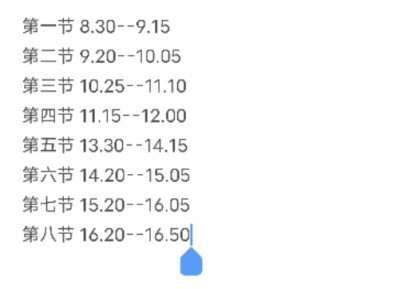

打铃时间为:

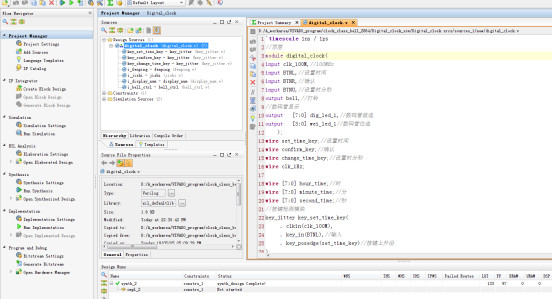

2. 程序文件

3. 程序编译

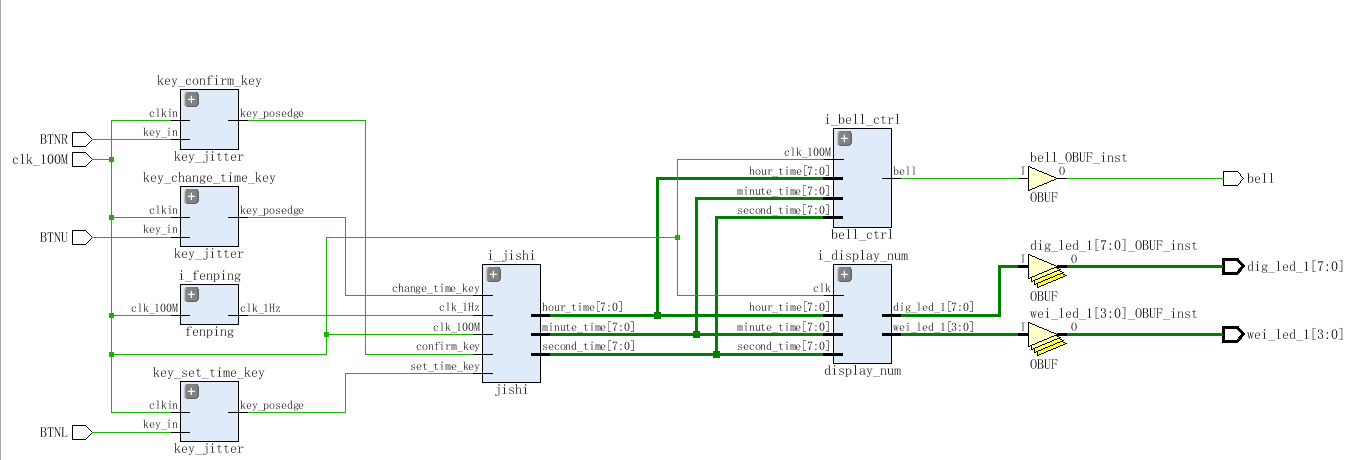

4. RTL图

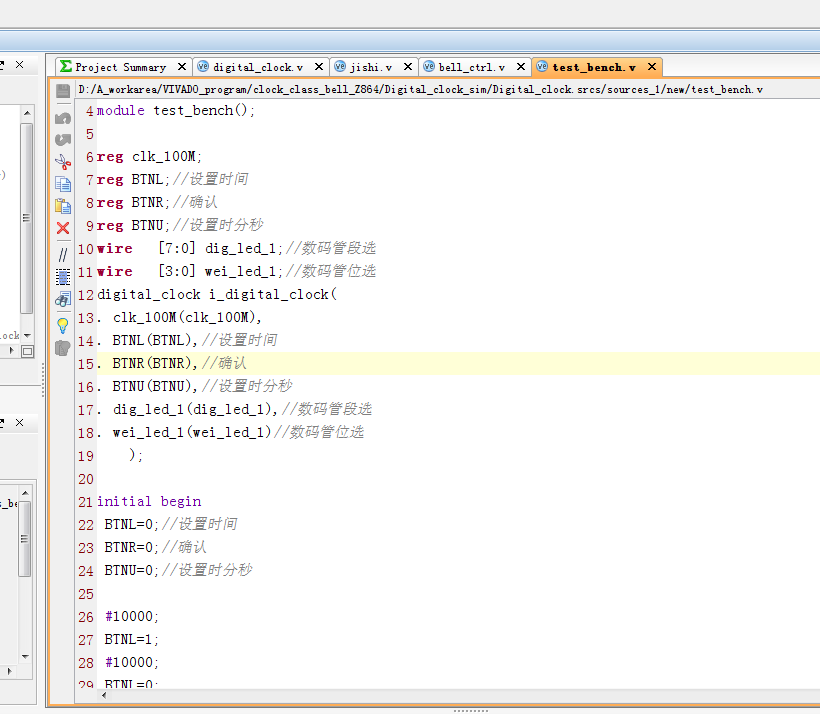

5. Testbench

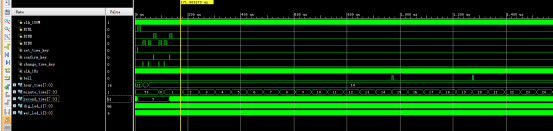

6. 仿真图

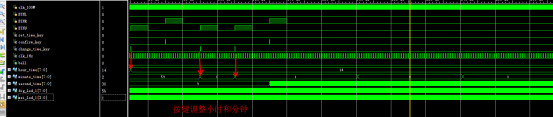

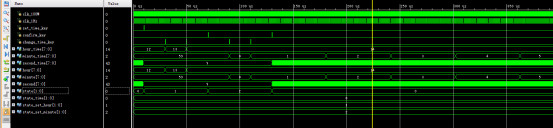

整体仿真图

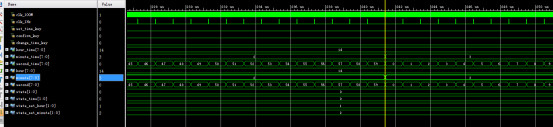

按键检测模块

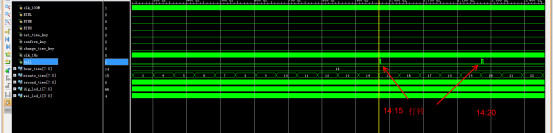

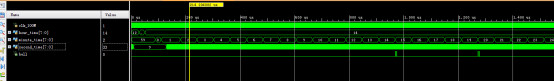

分频模块

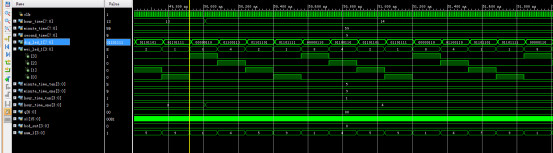

计时模块

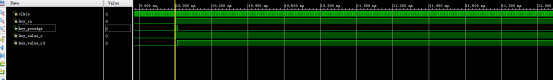

显示模块

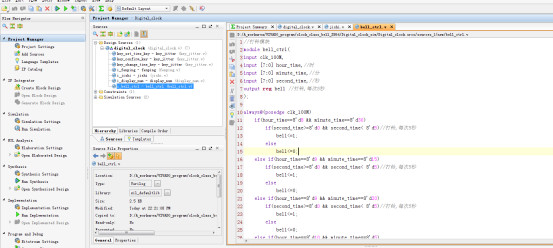

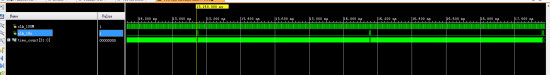

打铃模块

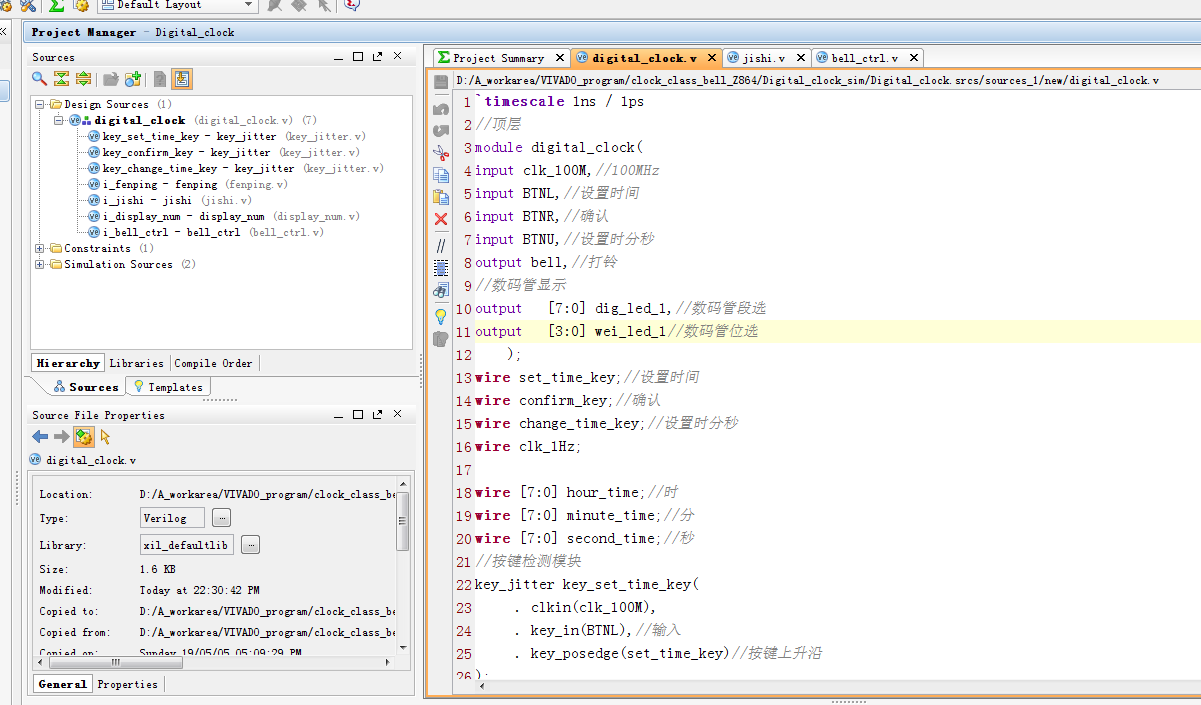

部分代码展示:

`timescale 1ns / 1ps //顶层 module digital_clock( input clk_100M,//100MHz input BTNL,//设置时间 input BTNR,//确认 input BTNU,//设置时分秒 output bell,//打铃 //数码管显示 output [7:0] dig_led_1,//数码管段选 output [3:0] wei_led_1//数码管位选 ); wire set_time_key;//设置时间 wire confirm_key;//确认 wire change_time_key;//设置时分秒 wire clk_1Hz; wire [7:0] hour_time;//时 wire [7:0] minute_time;//分 wire [7:0] second_time;//秒 //按键检测模块 key_jitter key_set_time_key( . clkin(clk_100M), . key_in(BTNL),//输入 . key_posedge(set_time_key)//按键上升沿 ); //按键检测模块 key_jitter key_confirm_key( . clkin(clk_100M), . key_in(BTNR),//输入 . key_posedge(confirm_key)//按键上升沿 ); //按键检测模块 key_jitter key_change_time_key( . clkin(clk_100M), . key_in(BTNU),//输入 . key_posedge(change_time_key)//后按键上升沿 ); //分频模块 fenping i_fenping( . clk_100M(clk_100M), . clk_1Hz(clk_1Hz) ); //计时 jishi i_jishi( . clk_100M(clk_100M), . clk_1Hz(clk_1Hz), . set_time_key(set_time_key),//设置时间 . confirm_key(confirm_key),//确认 . change_time_key(change_time_key),//设置时分秒 . hour_time(hour_time),//时 . minute_time(minute_time),//分 . second_time(second_time)//秒 ); //显示模块 display_num i_display_num( . clk(clk_100M), . hour_time(hour_time),//时 . minute_time(minute_time),//分 . second_time(second_time),//秒 . dig_led_1(dig_led_1), . wei_led_1(wei_led_1) ); //打铃模块 bell_ctrl i_bell_ctrl( . clk_100M(clk_100M), . hour_time(hour_time),//时 . minute_time(minute_time),//分 . second_time(second_time),//秒 . bell(bell) //打铃,每次5秒 ); endmodule

源代码

点击下方的公众号卡片获取

2195

2195

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?