1、高流量

拆开环路

就是将反馈拆开。

2、低时滞

去除触发器(并不是有效的提速方法,不够可以在非关键路径加)

3、时序

缩短关键路径

(1)并行化

(2)流水线

(3)寄存器平衡,将关键路径的组合逻辑移动到相邻路径

(4)添加触发器,将关键路径分成小块。

(5)迟滞信号后移,把延迟比较大的放距离输出寄存器进的位置。

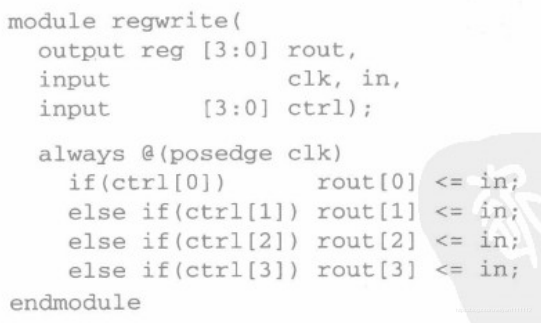

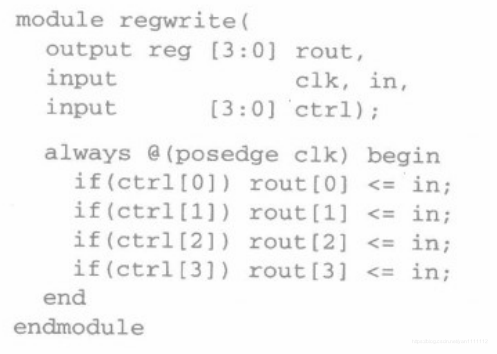

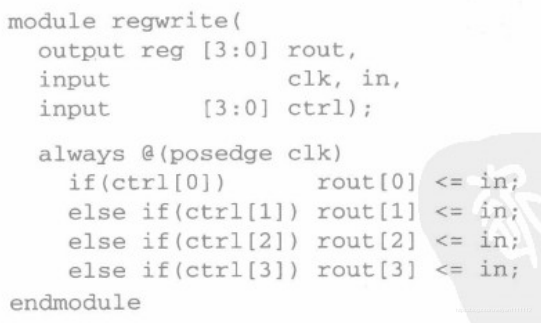

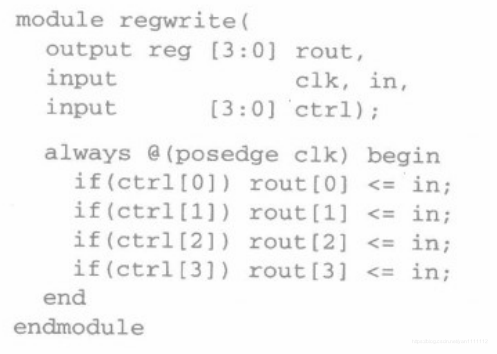

(6)展平逻辑(消除优先级)

少使用if else和case

FPGA速度优化

最新推荐文章于 2022-04-18 22:27:19 发布

1、高流量

拆开环路

就是将反馈拆开。

2、低时滞

去除触发器(并不是有效的提速方法,不够可以在非关键路径加)

3、时序

缩短关键路径

(1)并行化

(2)流水线

(3)寄存器平衡,将关键路径的组合逻辑移动到相邻路径

(4)添加触发器,将关键路径分成小块。

(5)迟滞信号后移,把延迟比较大的放距离输出寄存器进的位置。

(6)展平逻辑(消除优先级)

少使用if else和case

1891

1891

7817

7817

9024

9024

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?