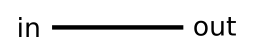

wire:

Implement the following circuit:

module top_module (

input in,

output out);

assign out=in;

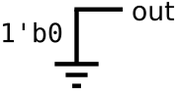

endmodulegnd:

Implement the following circuit:

.

module top_module (

output out);

assign out=1'b0;

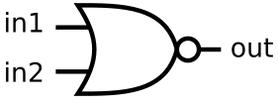

endmoduleNOR:

Implement the following circuit:

module top_module (

input in1,

input in2,

output out);

assign out=~(in1|in2);

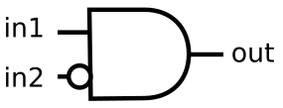

endmoduleanother gate:

Implement the following circuit

module top_module (

input in1,

input in2,

output out);

assign out=in1&(~in2);

endmoduletwo gates:

Implement the following circuit:

module top_module (

input in1,

input in2,

input in3,

output out);

wire t;

assign t=~(in1^in2);

assign out=t^in3;

endmodulemore logic gates:

let's try building several logic gates at the same time. Build a combinational circuit with two inputs, a and b.

There are 7 outputs, each with a logic gate driving it:

- out_and: a and b

- out_or: a or b

- out_xor: a xor b

- out_nand: a nand b

- out_nor: a nor b

- out_xnor: a xnor b

- out_anotb: a and-not b

module top_module(

input a, b,

output out_and,

output out_or,

output out_xor,

output out_nand,

output out_nor,

output out_xnor,

output out_anotb

);

assign out_and=a&b;

assign out_or=a|b;

assign out_xor=a^b;

assign out_nand=~(a&b);

ass

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3515

3515

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?