set_clock_groups

set_clock_groups 命令有三个选项:“-asynchronous”,“-logically_exclusive”,“-physically_exclusive”

当 set_clock_groups 命令中多个 groups 被指定时,同一个时钟不能出现在不同的 group 中,但是可以存在于多次 set_clock_groups 命令使用。

例如 set_clock_groups -asynchronous -group {ClkA ClkB} -group {ClkC} -group { ClkA ClkD},其中ClkA 存在于两个group中是不允许的。

但是 set_clock_groups -asynchronous -group {ClkA ClkB} -group {ClkC}

set_clock_groups -asynchronous -group {ClkA} -group {ClkD}

上面两个连续声明是合法的。

Asynchronous Clocks

多个时钟之间相位关系不确定,就可以将这两个(或多个)时钟是asynchronous,一般而言当时钟来自于不同的PLL或者晶振时,时钟之间的相位是不固定的。

creat_clock-period 10 -name ClkA [get_ports CLKA]

creat_clock-period 20 -name ClkB [get_ports CLKB]

上面两个时钟定义在primary input ports上,并且是asynchronous关系,我们就可按如下设置:

set_clock_groups -asynchronous -group {ClkA} -group {ClkB}

上面的命令等价于如下两个false path声明:

set_false_path -from [get_clocks ClkA] -to [get_clocks ClkB]

set_false_path -from [get_clocks ClkB] -to [get_clocks ClkA]

案例1

set_clock_groups -asynchronous -group {ClkA ClkC} -group {ClkB ClkD}

从上面的命令我们可以得到如下信息

1. ClkA 和 ClkC 是同步关系时钟。

2. ClkB 和 ClkD 是同步关系时钟。

3. ClkA & ClkC 与 ClkB & ClkD 是异步关系时钟。

同一个group分组中的时钟相互为同步关系,不同分组之间的时钟相互为异步关系。

案例2

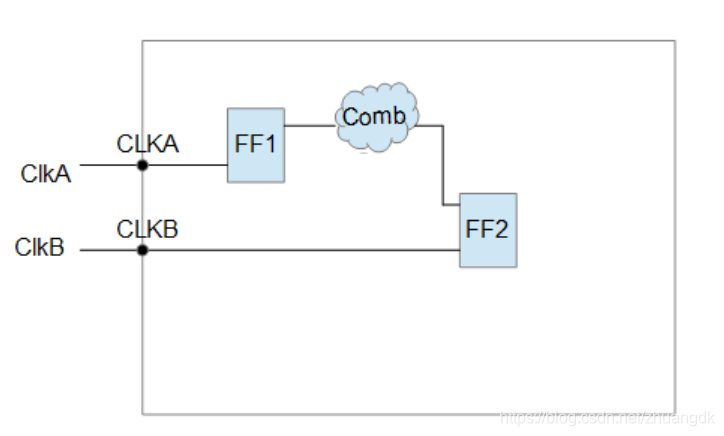

现在考虑这两个时钟其中一个(或者两个)产生其他时钟,如图所示

本案例中,时钟 ClkB 和 ClkDiv1 是同步的, 但与时钟 ClkA 为异步关系 。divClkB使用 “create_generated_clock” 以 ClkB 作为源时钟定义。

set_clock_group 在master clock 的作用影响默认不会应用于generated时钟上面。需要显式指定generated时钟的同异步关系。

set_clock_groups -asynchronous -group [get_clocks ClkA] -group [get_clocks {ClkB divClkB}]

Logically Exclusive Clocks

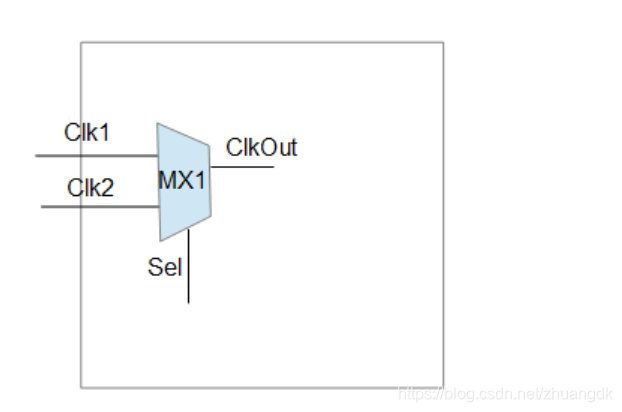

如果两个时钟同时存在但是他们之间没有任何 path,则这两个时钟可以设置为 logically exclusive,典型的情况就是一个 MUX 选择两个或多个时钟。

案例1

时钟 clkOut 通过Mux MX 的 Sel 进行选择,因此 Clk1 和 Clk2 在 MX1 的下游路径上不会逻辑上同时存在。它们在离开 MUX 之后不会相互作用。

set_clock_groups -logically_exclusive -group [get_clocks Clk1] -group [get_clocks Clk2]

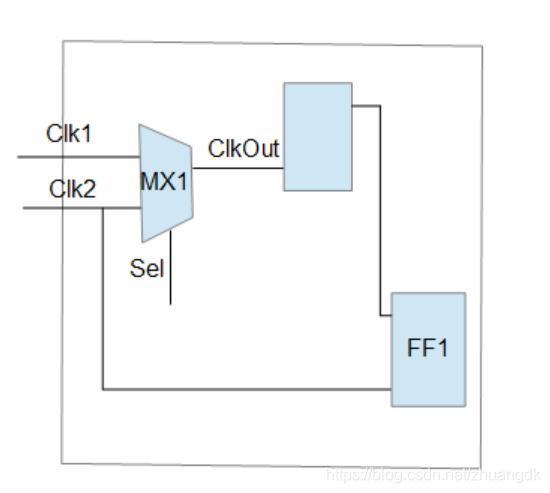

案例2

假如在 MUX 之外存在 Clk2 驱动的 flops,并且与 ClkOut 时钟驱动的 flops 相互作用,这时就不能设置 Clk1 和 Clk2 logically exclusive。

此时必须在 MX1 的 output 处创建 generated 时钟,创建的时钟可以设置为逻辑互斥关系。

create_generated_clk -name genClk1 -source MX1/Y -master Clk1

create_generated_clk -name genClk2 -source MX1/Y -master Clk2

set_clock_groups -logically_exclusive -group [get_clocks genClk1] -group [genClk2]

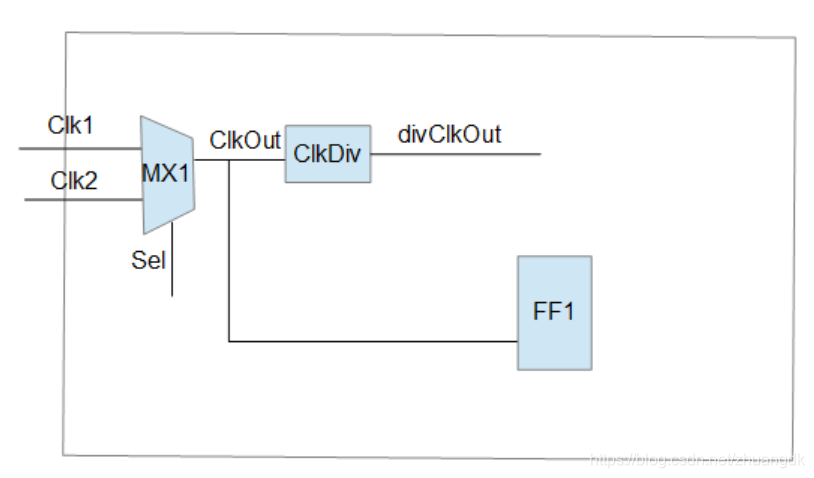

案例3

在 MX1 的输出有一个分频器,这种情况下需要创建两个 generated 时钟分别以 Clk1 和 Clk2 作为 master 时钟。

create_generated_clk -name genDivClk1 -source ClkDiv/Y -master Clk1

create_generated_clk -name genDivClk2 -source ClkDiv/Y -master Clk2

set_clock_groups -logically_exclusive -group [get_clocks {Clk1 genDivClk1}] -group [get_clocks {Clk2 genDivClk2}]

Physically Exclusive Clocks

当两个时钟在同一时刻不可能同时存在时,则这两个时钟就可以设置为 physical exclusive。比如在相同的 primary 端口上创建多个时钟,但是

这两个时钟工作在不同的工作模式,比如TestClk 和 Function Clock。SI 相互作用不会发生在这两个时钟之间。

set_clock_groups -physically_exclusive -group [get_clocks TestClk] -group [get_clocks SysClk]

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?