FPGA 设计中的流量,时滞,时序

流量:每个时钟周期能够传输的数据位。

时滞:数据从输入到输出需要经历的时钟周期;

时序:两个元件之间的最大延迟,他决定系统的最高时钟速度。

1 采用流水线可以提高 流量;

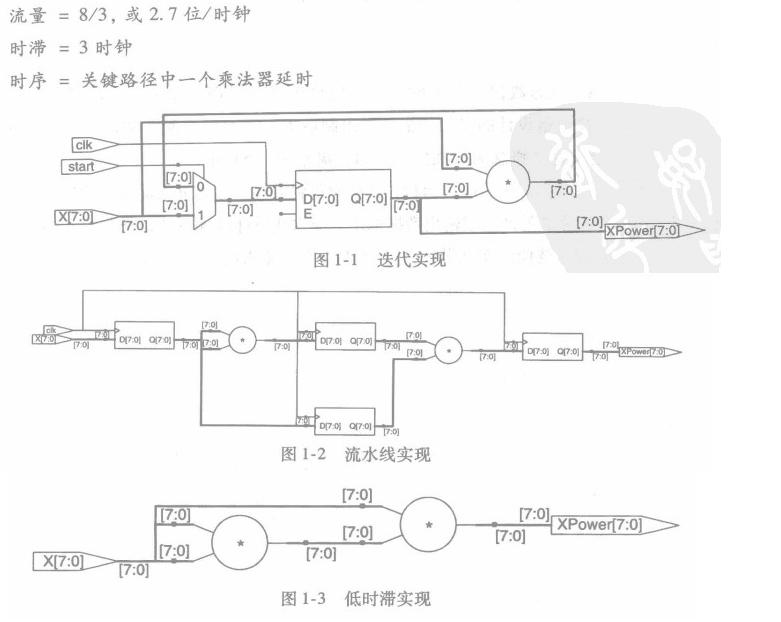

例如计算X^3,迭代结构

流水线:

此时

流量=8/1

时滞=3

时序=乘法器延迟

2 如果要求低时滞则可以去掉寄存器

3 降低时序,提高时钟频率的方法

86

86

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?