一、故事前传

前面的文章针对PCIe的一部分内容已经做了解析。

较为详细解释请见之前的文章:

1. PCIe技术概述;

2.0~2.8 PCIe Transaction layer事务层详细解析;

3.0~3.2 PCIe数据链路层详细解析;

二、物理层结构

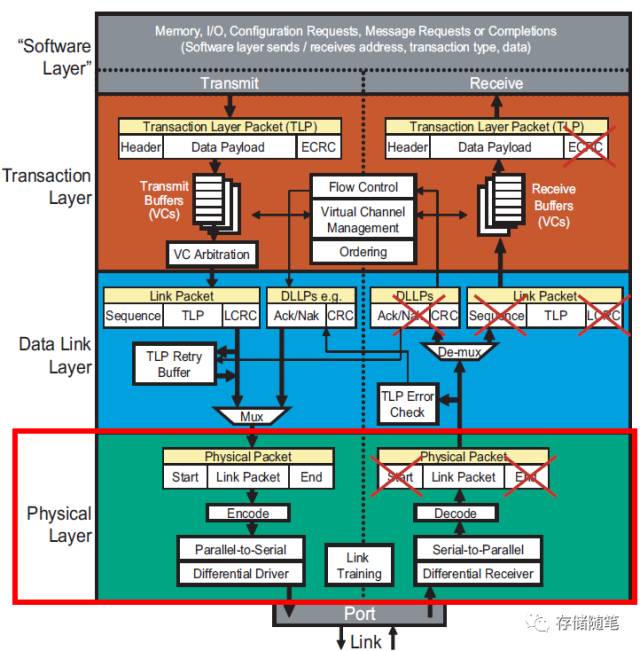

在PCIe体系中,物理层处于最底层。发送端数据链路层(Data Link Layer)的DLLP和TLP报文通过物理层(Physical Layer)发送至接收端的物理层,再传送至接收端的数据链路层。

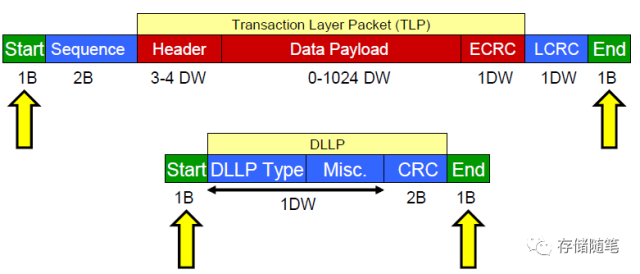

DLLP和TLP从数据链路层到达物理层后,物理层会在其两端分别加上Start和End标识,主要是方便接收端找到DLLP和TLP的边界。

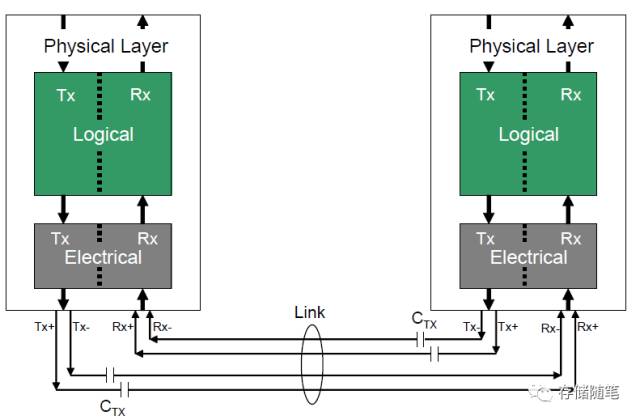

另外,物理层又分为两层:逻辑层(Logical)和电气层(Electrical)。逻辑层主要负责与数据链路层之间的数据交互,由发送逻辑Tx和接收逻辑Rx组成。电气层是物理层的模拟接口,包括了差分信号驱动和接收器。本专题对电气层不作展开介绍,主要会针对逻辑层进行解析。

话说现在的社会是拼颜值的时代,那我们是不是先看一下逻辑层的样子呀?

发送端逻辑层:

接收端逻辑层:

看到上面两张逻辑层结构图,又晕了~

这里先结合上面的逻辑层结构图大致表述一下逻辑层的作用:

发送端:

1. 从发送端数据链路层下发的DLLP/TLP在到达物理层后,会先放入Tx Buffer中。在Tx buffer中,DLLP/TLP被加上前缀Start和后缀End。

2. 之后,DLLP/TLP通过多路选择器Mux,到达Byte Stripping组件。由于PCIe总线可能包含多个Lane, Byte Stripping组件将DLLP/TLP数据报文按照数据依次分发到不同的Lane。

3. 数据进入每个Lane之后都会做加扰(Scramble), 8/10b编码( Only for Gen1/2), 128b/130b编码(Only for Gen3).

4. 完成加扰和编码后,数据通过并转串逻辑,最后发送到PCIe链路中。

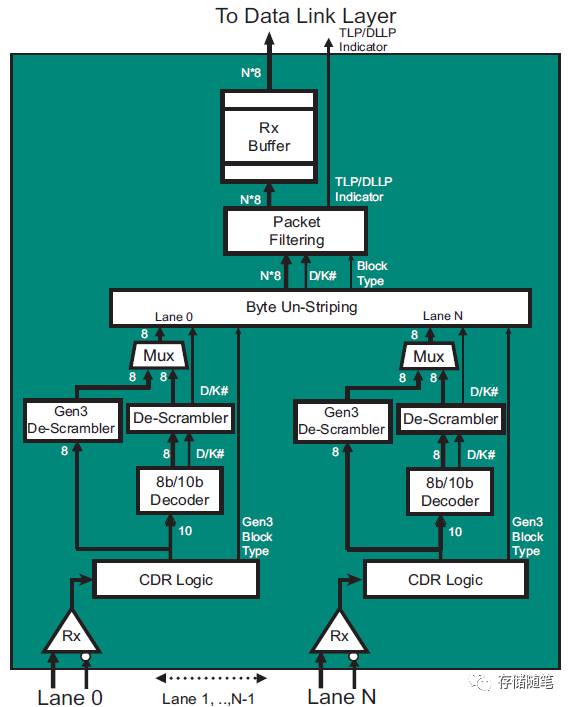

接收端:

1. 接收端的逻辑层从PCIe链路的各个Lane中获得串行数据。

2. 各个Lane的数据经过解码与解扰(De-Scramble),最终到达Byte Un-Stripping组件。

3. Byte Un-Stripping组件将来自各个Lane的数据进行合并,检查Start和End标识后送入Rx Buffer, 最后传送至接收端数据链路层。

本文深入探讨了PCIe物理层的结构与工作原理,重点介绍了发送端与接收端的逻辑层如何处理DLLP/TLP报文,包括加扰、编码等关键步骤。

本文深入探讨了PCIe物理层的结构与工作原理,重点介绍了发送端与接收端的逻辑层如何处理DLLP/TLP报文,包括加扰、编码等关键步骤。

1354

1354

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?