在过去的十年里,数据中心和服务器行业经历了前所未有的扩张,这一进程伴随着CPU核心数量、内存带宽(BW),以及存储容量的显著增长。这种超大规模数据中心的扩张不仅带来了对计算能力的急剧需求,也带来了前所未有的内存功率密度挑战,类似于移动设备中遇到的问题。因此,提高DRAM的能效成为当务之急,以应对数据中心内不断上升的能耗压力。(扩展阅读:一文读懂DDR内存基础知识|值得收藏)

云技术的出现彻底改变了我们对大规模计算的观念和部署方式,而人工智能(AI)更是从根本上重塑了计算的本质。AI性能直接与内存带宽挂钩,简而言之,AI性能=内存带宽=每比特能量消耗(pj/bit)=AI性能。在这个等式中,存储容量和可靠性虽然重要性有所下降,但仍需考虑其长期的可持续性和扩展性。

目前,主流DRAM作为行业发展的驱动力,其体积解决方案对于引导工艺节点和技术发展至关重要。HBM(High Bandwidth Memory,高带宽内存)技术的Bit增长依赖于基础DRAM技术的持续进步。

然而,DDR5系统的带宽和容量扩展并没有出现预期的指数级增长,在DDR5的情况下,这种快速增长的拐点并未出现,意味着其带宽与容量的增长较为线性和渐进,而非呈现陡峭的上升曲线。这样凸显了优化DRAM带宽与容量比率以及降低DRAM接口能耗的重要性。

这一现象背后的两个核心衡量指标是“BW/capacity ratio”(带宽与容量比率)和“DRAM + interface pj/bit”(DRAM及其接口每比特能量消耗)。这两个指标共同构成了加速DRAM扩展的关键绩效指标。

-

BW/Capacity Ratio:这个比率体现了系统带宽与存储容量之间的平衡。在数据中心和AI应用中,高效的计算不仅需要足够的存储空间(容量),还需要快速的数据访问速度(带宽)。一个理想的配置是两者保持适当比例,以避免带宽瓶颈或过度投资于不被充分利用的容量。因此,维持合理的BW/Capacity比率对于优化系统性能至关重要。

-

DRAM + Interface pj/bit:这里的“pj/bit”是指每传输一位数据所消耗的能量单位。降低这个值意味着提高了能效,这对于数据中心运营来说至关重要,因为这直接影响到电力消耗和冷却成本。DRAM及其接口的能耗优化是提升整体系统能效的关键。尤其是在高密度、高性能的环境中,如AI计算,减少每比特能耗对于持续运行的大型服务器集群来说,能显著降低成本并提高环境可持续性。

随着AI技术的不断演进,2028年及之后的AI营收预测显示,无论是训练还是峰值推理任务,HBM仍将是必要的选择。预计推理工作负载将更加细分,不同的应用场景将需要不同的内存技术。特别是主流和基础推理应用,它们对带宽的需求超过了DDR5所能提供的,同时要求在更低功耗下运行,这提示了一个新解决方案的需求正在浮现。(扩展阅读:深度剖析AI存储架构的挑战与解决方案)

-

训练与峰值推理继续需要HBM:AI模型的训练阶段通常涉及大量数据的处理,需要极高的内存带宽来快速读取和写入数据。HBM因其高带宽特性,成为满足这一需求的理想选择。即使在模型训练完成后,进行高负载的峰值推理时,HBM的高性能依旧不可或缺,以确保快速响应和处理能力。

-

推理工作负载细分将要求不同的内存技术:随着AI应用的多样化,推理任务不再是单一类型,而是根据场景和需求被细分为多个类别。例如,主流推理可能在大多数日常应用中进行,而基线推理可能涉及对延迟不太敏感的任务。这些不同类型的推理负载可能对内存的带宽、功耗、容量等有各自特定的需求,促使业界探索和采用多样化的内存技术。(扩展阅读:是谁?阻止CXL在AI场景大展身手~)

尽管DDR5作为新一代内存标准,在带宽和能效方面相比前代已有显著提升,但在某些主流和基线推理场景下,其带宽和功耗表现仍不足以满足需求。这些场景要求比DDR5更高的带宽,同时还要保持或优于DDR5的能效水平,这意味着需要在现有技术之外寻找新的解决方案。

鉴于上述挑战,开发一种既能提供更高带宽,又能保持良好能效比的新内存技术成为必然。这暗示着业界正在探索HBM之外的其他技术或HBM技术的进一步演进,以满足不同AI推理场景的需求。例如,可能涉及更先进的内存架构设计、新材料的应用、或是对现有HBM技术进行改进,以突破现有的堆叠层数限制和密度瓶颈,同时优化功耗。

随着人工智能(AI)解决方案对数据处理速度的不断追求,其最大峰值带宽(Max peak BW)持续快速提升,这对内存技术提出了更高要求。特别是对于高带宽内存(HBM),其容量扩展受到了多方面因素的限制,主要包括超过16层堆叠(>16Hstacking)、基础DRAM技术节点的密度限制,以及封装技术的制约。这些限制意味着单纯依靠增加HBM堆叠层数或提高单个DRAM芯片的密度来扩大容量并非长久之计,因为这些方法都面临着物理和材料科学上的极限。

在此背景下,大规模的AI和服务器市场期待着一种全新的长期发展路径,该路径旨在同时提升带宽和容量,从而弥补当前市场上带宽与容量之间存在的缺口(BW/capacity gap)。这样的发展策略对于确保AI应用的持续增长和数据中心效率的提升至关重要,因为它不仅解决了性能瓶颈,还能引入更强大、更可靠的RAS(Reliability, Availability, Serviceability,即可靠性、可用性和可维护性)选项。

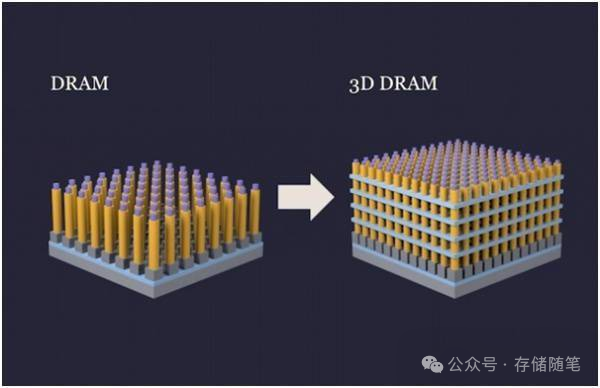

特别是对 3D DRAM 的探索,通过将存储单元垂直堆叠而非水平排列,可以在不大幅改变单个单元尺寸的情况下显著增加单位体积内的存储比特数,从而在一定程度上克服 2D 缩放的局限。尽管 3D DRAM 技术尚处于早期研发阶段,且面临诸多技术挑战(如专利布局、工艺复杂性、架构选择等),但因其巨大的潜力,已成为业界关注的焦点。

目前3D DRAM 的公开技术文献数量极少。行业主要厂商在公开交流上保持沉默,但在背后却在积极申请大量与 3D DRAM 相关的专利。这种现象表明,尽管企业不愿意公开分享技术细节,但他们对 3D DRAM 技术的开发投入巨大,并且通过专利保护的方式为未来的市场竞争和技术主导权做准备。这种策略反映出 3D DRAM 技术的战略重要性和潜在的巨大商业价值。

可以公开查询的关于3D DRAM的论文,比如来自 国内长鑫存储CXMT(2023 IMW Conf.)和三星(2023 VLSI Symp.),都是DRAM厂商在专业会议上发布的针对 1T1C(一晶体管一电容)结构的 3D DRAM。

• 2023 IMW Conf. “A 3D Stackable 1T1C DRAM: Architecture, Process…” by CXMT

• 2023 VLSI Symp. “ Ongoing Evolution of DRAM Scaling via 3rd Dimension: V-DAM” by Samsung

除了主流的 1T1C 3D DRAM 研究,还有其他创新的无电容 DRAM 方法在探索中。其中,2T0C Gain Cell 主要集中在学术研究层面,而 Gate-controlled-thyristor DRAM 则由 Macronix 开发。这两种无电容方案旨在通过简化结构、减少或取消电容元件来降低制造复杂度,提高集成度,可能是 3D DRAM 发展的另一种可能路径。

从 2D DRAM 向 3D DRAM 转变过程中将面临无数技术挑战。这些挑战涵盖工艺技术的各个方面,如硬掩模刻蚀(HAR etch)、横向刻蚀、原子层沉积(ALD)、原子层刻蚀(ALE)、外延生长、沉积技术、掺杂、硅化物形成、接触形成以及应力管理等。这些复杂且精密的工艺步骤需要相应的设备支持和技术创新,为半导体设备供应商提供了技术服务和设备升级的市场空间。

三星(Samsung)和SK海力士(SK hynix)作为在高带宽内存(HBM)领域快速发展的企业,根据最新报告,这两家公司确认计划在即将推出的3D DRAM技术中采用混合键合技术。当前技术主要利用微凸点连接DRAM模块,而混合键合技术则可以通过硅通孔(TSV)实现芯片的垂直堆叠,从而避免使用微凸点,大幅减小芯片厚度。

早前《韩国经济日报》的报道指出,当前的DRAM技术在一个基板上集成了高达620亿个单元,基板上密集排列着晶体管,形成了平面结构,这导致了电流泄漏和干扰等问题。相比之下,3D DRAM通过将晶体管堆叠成多层,增加了它们之间的间隔,从而减少了泄漏和干扰。

为了替代传统的横向布局,3D DRAM通过垂直堆叠存储单元,实现了单位面积存储容量的三倍提升。这与HBM有所不同,HBM是通过垂直连接多个DRAM芯片来实现高带宽。

在最近于首尔举行的2024国际内存研讨会(International Memory Workshop)上,SK海力士宣布了其在3D DRAM生产中实施混合键合的计划。而三星则据《韩国经济日报》之前的报道,计划在2025年推出3D DRAM。

与此同时,三星还在探索4F²DRAM技术,并计划将其与混合键合技术整合到生产过程中。如果成功,与目前商业化生产的6F² DRAM相比,三星可以将裸片表面积减少30%。三星预计将使用10纳米或更精细的工艺节点来实现4F²结构的DRAM。

此外,三星认为混合键合技术对于16层堆叠的HBM至关重要,这标志着3D DRAM市场份额争夺战的悄然开始。这些动向显示出存储巨头们正积极布局未来,通过技术创新解决数据存储的带宽、容量、能效以及可靠性等挑战,为数据中心和人工智能等高需求应用提供更为先进的解决方案。

展望2030年及以后,AI解决方案的峰值带宽将持续快速增长,而HBM的容量扩展因技术节点密度和封装的限制而受限。为了解决当前带宽与容量之间的缺口,并允许更强大的RAS(可靠性、可用性、可服务性)选项,大规模的AI和服务器市场需要探索新的长期发展路径,这条路径能够同时提升带宽和容量,确保AI和数据中心行业的可持续发展。

扩展阅读:

行业正面临从带宽驱动的内存需求转向,这为解决带宽与容量差距及提升内存韧性的挑战提供了契机。基础技术的发展对于HBM和DDR5/LPDDR技术的持续演进至关重要,且在提升带宽和容量的同时,还需关注能效、成本优化以及大规模部署下的RAS特性。未来,数据中心和AI领域的内存技术革新将是应对这些挑战、把握新机遇的关键。

参考文献:

-

JEDEC-Server & Data Center Memory (& the AI paradigm shift)

-

https://www.trendforce.com/news/2024/06/20/news-samsung-and-sk-hynix-to-implement-hybrid-bonding-with-3d-dram/

如果您看完有所受益,欢迎点击文章底部左下角“关注”并点击“分享”、“在看”,非常感谢!

精彩推荐:

404

404

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?