目录

一、前言

比较器是数字电路中使用频率高的逻辑,器件通常也有自带的比较器IP核,本文通过verilog代码来实现。

二、工程设计

工程代码,设计为比较2个8位的二进制数的大小

2.1 设计代码

module Compare(A,B,AEB,ASB,AGB);

input [N-1:0] A,B;

output reg AEB,ASB,AGB;

parameter N=8;

always@(A,B)

begin

if(A==B)

begin

AEB=1'b1;

ASB=1'b0;

AGB=1'b0;

end

else

if(A>B)

begin

AEB=1'b0;

ASB=1'b0;

AGB=1'b1;

end

else

begin

AEB=1'b0;

ASB=1'b1;

AGB=1'b0;

end

end

endmodule测试代码,A和B的值使用系统任务random来生成,

module Compare_tb;

reg [7:0] A,B;

wire AEB,ASB,AGB;

initial

begin

A=8'b0;

B=8'b0;

end

always #1 A={$random}%(50);//生成0-49间的随机数

always #1 B={$random}%(49);//生成0-48间的随机数

Compare Compare_test(.A(A),.B(B),.AEB(AEB),.ASB(ASB),.AGB(AGB));

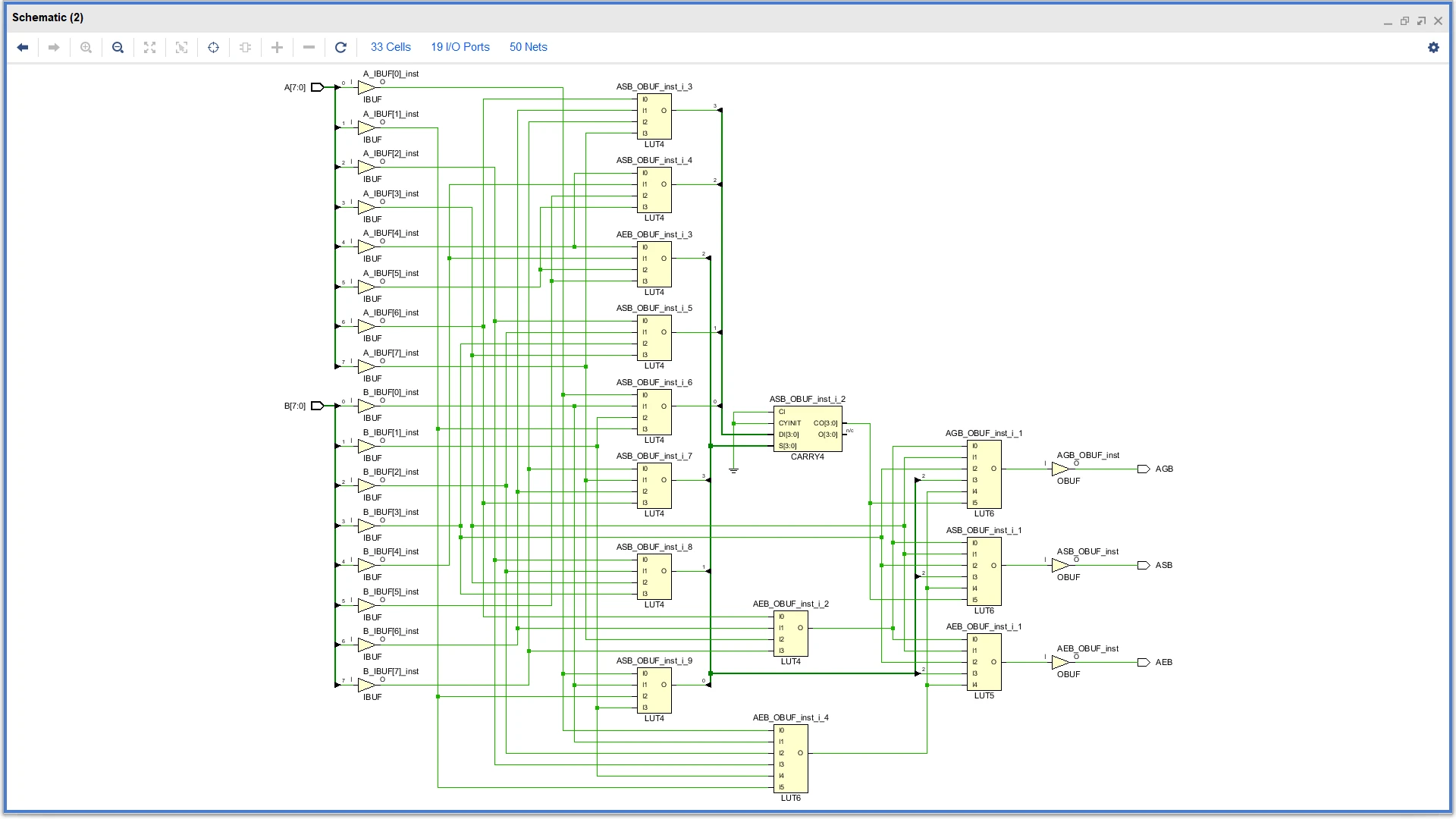

endmodule综合结果

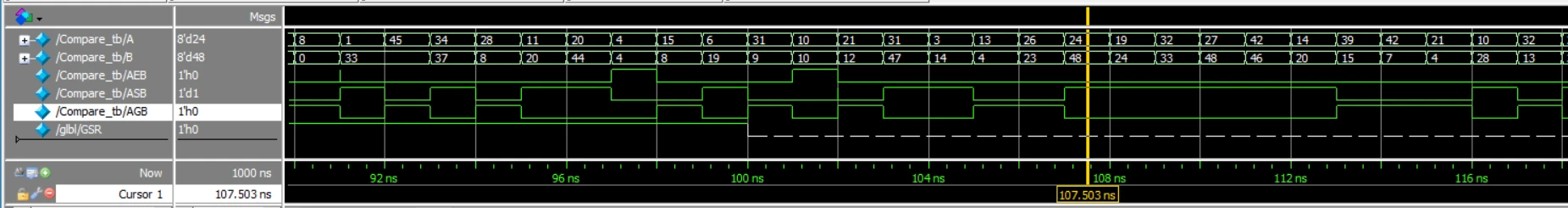

2.2 仿真结果

通过仿真结果图,可知逻辑正确

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?