目录

一、前言

时序约束中,有一类约束属于Exceptions类,之所以称为Exceptions(例外)是指约束后进行时序分析时与默认的边沿选取不同,包含set_multicycle_path/set_false_path/set_max_dealy/set_min_delay四种约束。在运行时序分析时,Report Exceptions即是专门针对涉及Exceptions的路径进行报告,并且还会报告clk group约束,通过时序例外约束报告可以获取以下信息。

a) 设计中设置的所有影响时序分析的时序例外约束

b) 设计中设置的因被其他时序例外覆盖而不影响时序的时序例外约束

有些设计存在着复杂的时序例外约束,同时时序例外约束的优先级规则较多,通过时序例外报告可以用于调试时序例外相关的问题。

二 Report Exceptions

2.1 配置界面

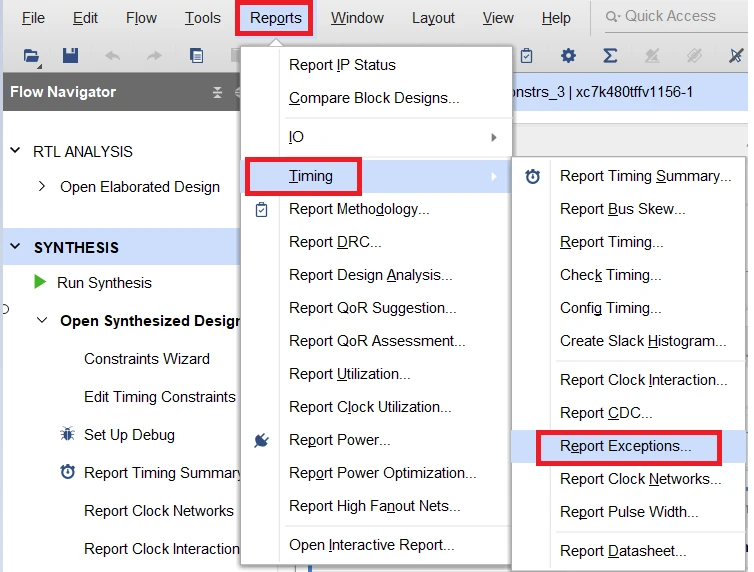

通过菜单栏的Reports->Timing->Report Exceptions可以进入到报告的配置界面

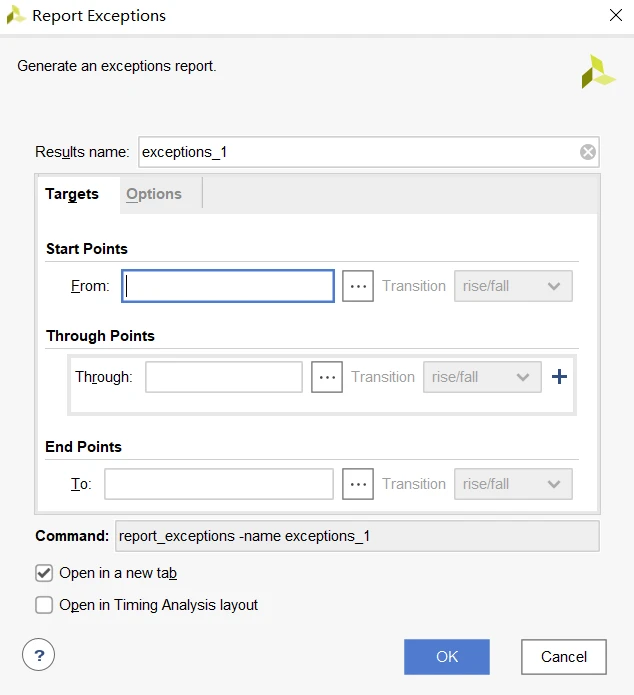

配置界面主要有Targets和Options两部分组成

Results Name:设置Exceptions报告的名称

Start Points:指定生成Exceptions报告的时序路径起点,类型可为Cells,Clocks,Cell Pins,I/O Port四种

Transition:指定start points的上升沿/下降沿或两个边沿都有效

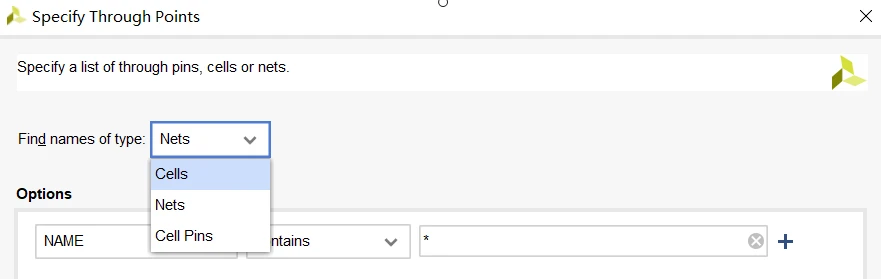

Through Points:指定时序分析路径中间经过的对象,可为Nets,Cells,Cell Pins三类

End Points:指定时序分析路径的终点,类型可为Cells,Clocks,Cell Pins,I/O Port四种,同样也可以在Transition设置对象生效的边沿rise/fall

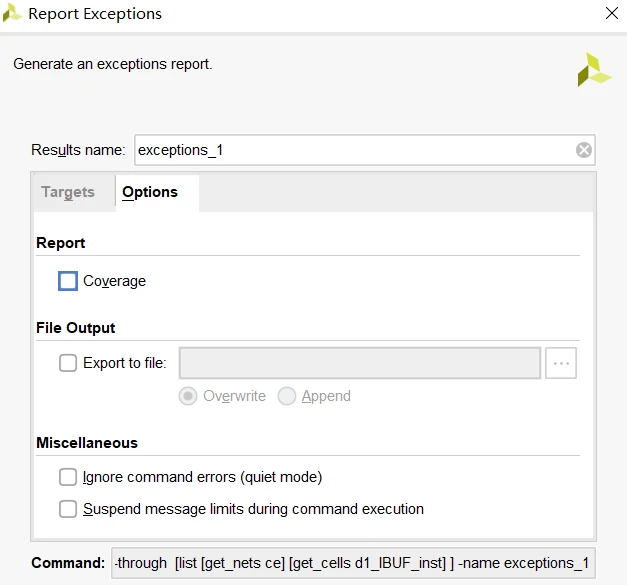

Options界面如下图

Coverage:报告是否包含所有时序例外,

File Output:用于设置是否将报告结果导出为txt文件,默认不导出。如果勾选了设置导出文件路径后,默认选择Overwrite,即如果存在报告文件,则新的报告内容直接覆盖原有的内容,如果选择Append则在原来内容后面追加新的报告内容

Ignore command errors (quiet mode):勾选后将会忽略运行报告时遇到的错误

Suspend message limits during command:勾选后将会忽略运行报告时的信息输出限制

Command:根据上述的配置自动生成对应的tcl命令

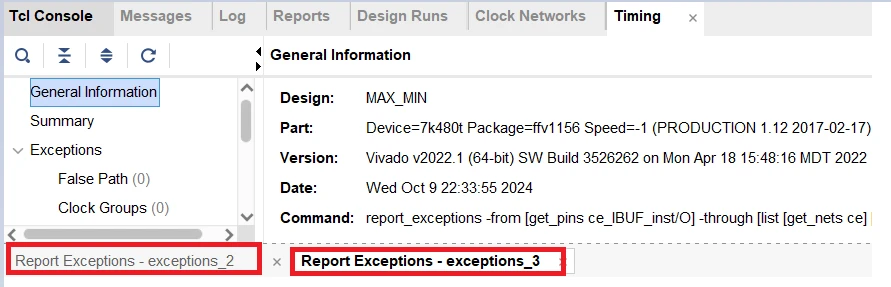

Open in a new tab:勾选后每执行一次分析会打开一个新的窗口,默认勾选,下图是勾选后执行了两次分析生成的两个tab。

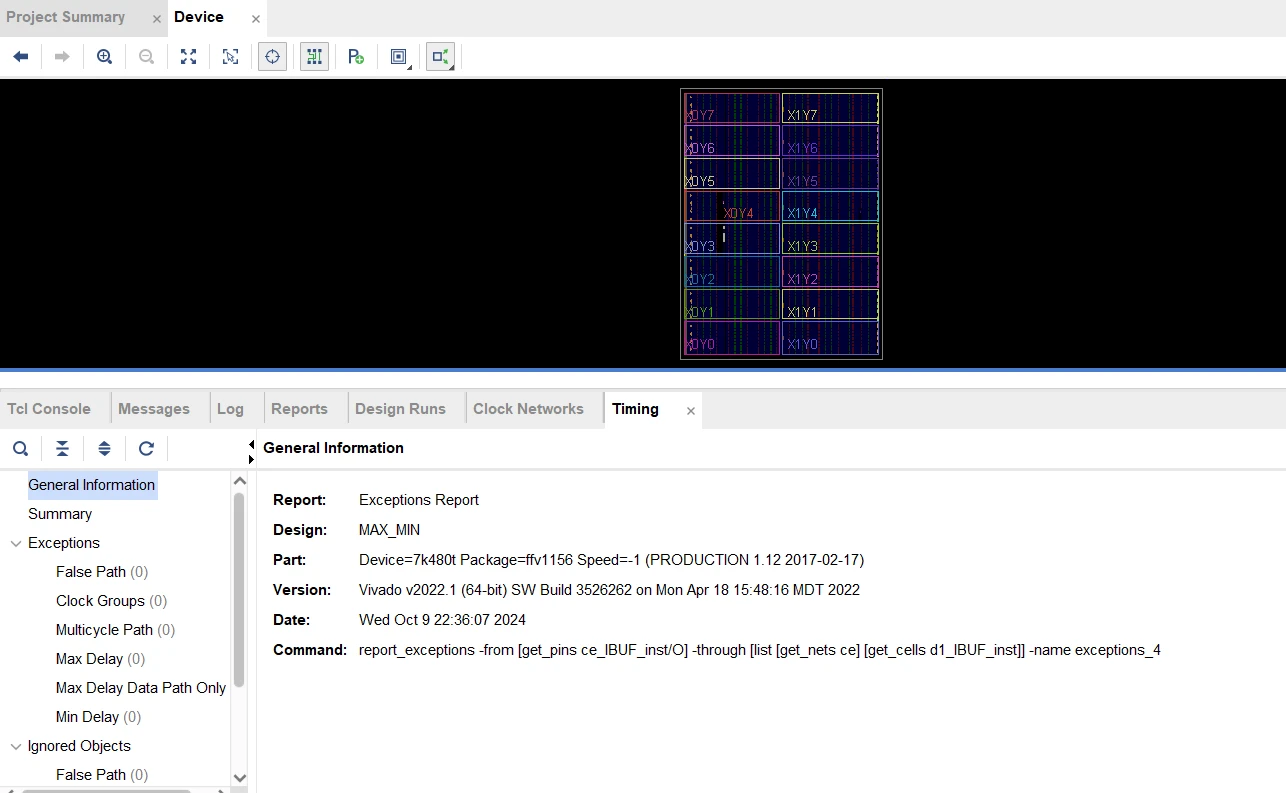

Open in Timing Analysis layout:勾选后在生成报告的同时会打开Device窗口,默认不勾选

2.2 设计示例

module report_exception(d1,d2,d3,d4,clk1,clk2,clk3,ce,ff_min,ff_max,ff_false,ff_multi,out,out_group);

input d1,d2,d3,d4,clk1,clk2,clk3,ce;

output ff_min,ff_max,ff_false,ff_multi,out,out_group;

reg ff_min,ff_max,ff_false,ff_multi,out,out_group;

wire result;

always@(posedge clk1,negedge ce)

begin

if(!ce)

ff_min<=0;

else begin

ff_min<=d1;

ff_max<=d2;

ff_multi<=d3;

ff_false<=d4;

end

end

assign result=ff_min+ff_max+ff_false+ff_multi;

always@(posedge clk2,negedge ce)

begin

if(!ce)

out<=0;

else

out<=result;

end

always@(posedge clk3,negedge ce)

begin

if(!ce)

out_group<=0;

else

out_group<=result;

end

endmodule2.3 Exception报告

Exception报告包含四个部分:General information,Summary,Exceptions,Ignored Objects;

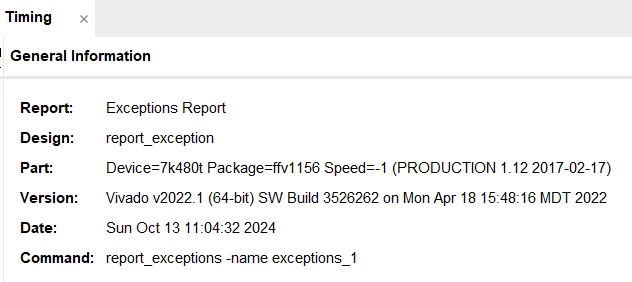

2.3.1 General information

与其他时序报告类似,General information主要包含一些基本信息,报告类型,设计模块名称,器件信息,Vivado版本,报告生成时间,报告生成对应的tcl命令

2.3.2 Summary

summary中根据Exception类型对设置的约束,约束如下

create_clock -period 10.000 -name clk1 -waveform {1.000 6.000} [get_ports clk1]

create_clock -period 8.000 -name clk2 -waveform {0.000 4.000} [get_ports clk2]

create_clock -period 8.000 -name clk3 -waveform {0.000 4.000} [get_ports clk3]

set_false_path -from [get_pins ff_false_reg/C] -to [get_pins out_reg/D]

set_multicycle_path -from [get_pins ff_multi_reg/C] -to [get_pins out_reg/D] 3

set_max_delay -from [get_pins ff_max_reg/C] -to [get_pins out_reg/D] 2.000

set_min_delay -from [get_pins ff_min_reg/C] -to [get_pins out_reg/D] 3.000

set_clock_groups -name clk3_group -asynchronous -group [get_clocks clk3]

set_max_delay -datapath_only -from [get_pins ff_min_reg/C] -to [get_pins out_reg/D] 4.000报告如下,按照时序例外约束类型分类进行

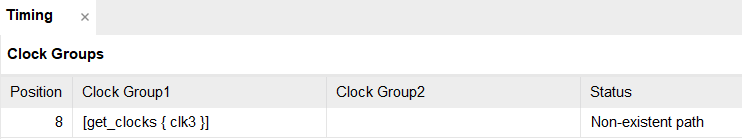

其中Ignored Constraints中Clock Groups为1,是由于设置的clock_group约束无有效的时序路径

2.3.3 Exceptions

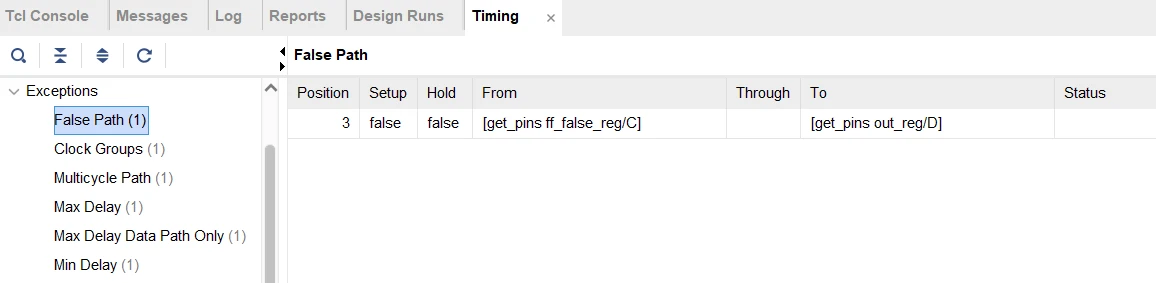

Exceptions中显示各类型约束命令的内容详情,Position为约束命令所在约束文件中的行数

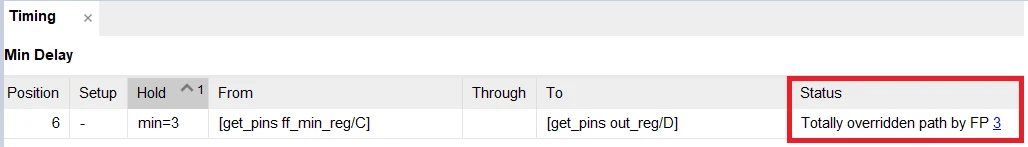

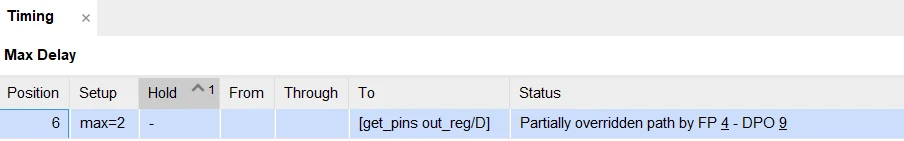

Status显示约束命令的状态,为空表示约束生效,如果约束的路径对象不存在或约束被覆盖也会显示说明,例外上述set_false_path约束改成如下约束

set_false_path -to [get_pins out_reg/D]结果如下,Min delay约束即被约束文件中第3行的false path约束覆盖,FP表示false path,其他类似的简写含义,MCP:multicycle path,MXD:max delay,MND:min delay,CG:clock group

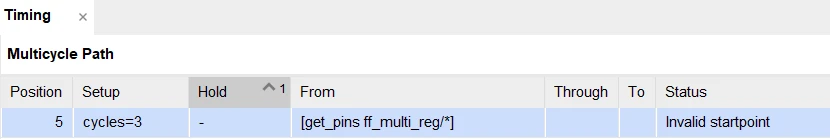

约束设置了无效起点的status

部分约束被覆盖

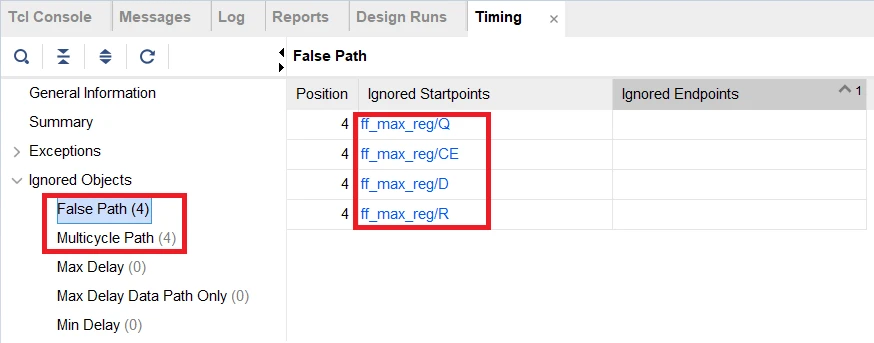

2.3.4 Ignored Objects

Ignored Objects报告是用于显示时序例外约束中约束的无效起点,终点,Vivado通常会直接忽略这些无效的对象,以下面约束为例,set_false_path和set_multicycle_path约束将触发器的所有引脚设为了起点

set_false_path -from ff_max_reg/*

set_multicycle_path -from [get_pins ff_multi_reg/*] 3报告如下,除了时钟引脚有效外,其他4个引脚都属于无效的起点

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?