#学习记录#

1 计数器

计数是一种最简单基本的运算。计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能,计数器是由基本的计数单元和一些控制门所组成,计数单元则由一系列具有存储信息功能的各类触发器构成,这些触发器有RS触发器、T触发器、D触发器及JK触发器等。

1.1 计数器的Schematic

图1 计数器的schematic

2 Verilog描述4位的计数器

2.1 代码

`timescale 1ns / 1ps

//

// Company:

// Engineer: Mr-pn-junction

//

// Create Date: 2023/10/14 09:46:08

// Design Name:

// Module Name: counter_4

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module counter_4(

input clk,

input rst_n,

output reg [3:0] dout

);

always @(posedge clk or negedge rst_n) begin

if(!rst_n)

dout<=0;

else if(dout==4'b1111)

dout<=0;

else

dout<=dout+1;

end

endmodule2.2 testbench

`timescale 1ns / 1ps

//

// Company:

// Engineer: Mr-pn-junction

//

// Create Date: 2023/10/14 10:11:02

// Design Name:

// Module Name: counter_tb

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module counter_tb( );

reg clk;

reg rst_n;

wire [3:0] dout;

counter_4 tb(

.clk(clk),

.rst_n(rst_n),

.dout(dout)

);

initial begin

clk=0; rst_n=0;

#10

rst_n=1;

end

always #10 clk=~clk;

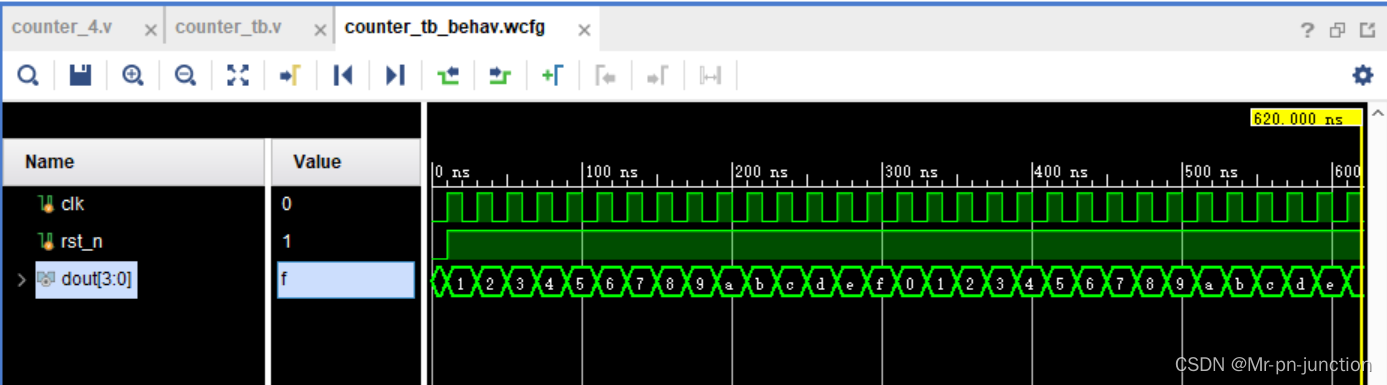

endmodule3 仿真结果

图2 仿真结果

参考文献

[1] 计数器. 百度百科. 计数器_百度百科 (baidu.com)

2804

2804

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?