在我们常规的理解中认为,一个信号经过一个标准单元后,必然会有一个delay。那么这个delay基本上正值。

但在特殊情况下,cell delay其实也可以是负值。那么,为了搞清楚这个问题,我们先看一下cell delay是如何定义的?

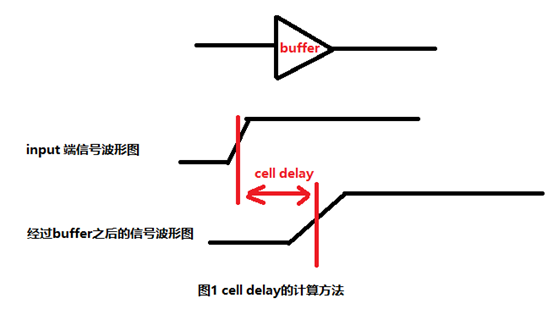

假设一个信号,经过buffer以后,其信号delay值得计算方法如图1所示,其delay值由input信号上升沿50%处至output信号上升沿50%的delay值。

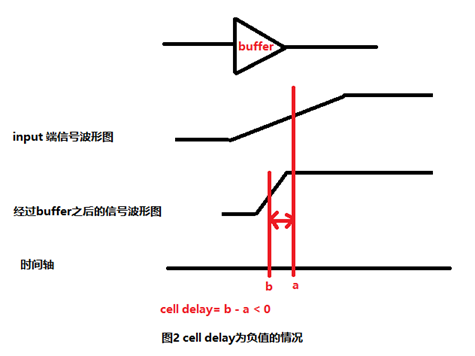

那么,假设如图2这种特殊的情况,即input信号上升沿特别大,便有可能出现cell delay

所以,碰到这种cell delay是负值的情况时,我们首先去检查一下是不是input transition太大导致。

#小编是一个入行多年的数字后端工程师,本身对编程方面比较感兴趣,在数字后端的脚本、flow上比较擅长,可以为大家提供答疑咨询服务。如有需求,可打开星球芯冰乐,获取更多知识干货分享与答疑服务。

134

134

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?