赋值语句共有两种,即非阻塞赋值,和阻塞赋值。

(1)非阻塞赋值

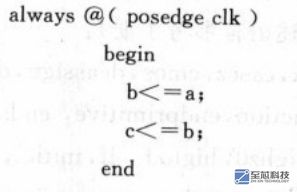

非阻塞赋值方式所赋值的变量不能立即就为下面语句所用,只有当块结束后才能得到上一次所附的值,这种赋值方式是编写可综合的时序逻辑时常用的赋值方式。例如

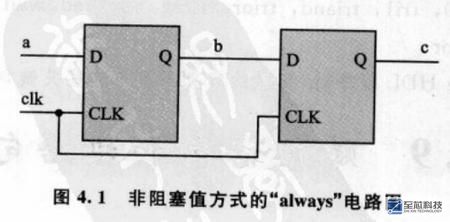

实际上,上面的非阻塞赋值的RTL是一个移位寄存器

如果开始时,a=1,b=2,c=x;那么,当一个clk上升沿到达后,a=1,b=1,c=2,实际从12x变成了112,即向后移了一位,最后,输出会变成a=1,b=1,c=1。

也可以直接理解非阻塞赋值时并行执行语句,即begin里面的两个非阻塞赋值语句是同时执行的,当clk上升沿到达后,a的值赋值给b,在a赋值给b的同时,b的值赋值给c,于是,a=1,b=1,c=2。

非阻塞赋值方式所赋值的变量不能立即就为下面语句所用,我的理解就是当时赋值的语句被锁存了,必须等下一个上升沿触发后才能赋值给下个语句。

(2)阻塞赋值

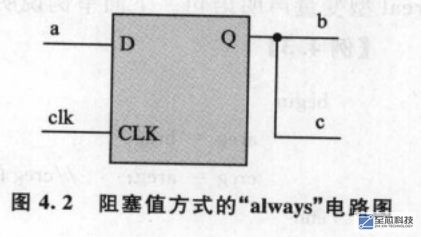

与非阻塞赋值不同,赋值语句执行完后块才结束,b 的值在赋值语句结束后立刻改变,但是在时序逻辑电路中可能会出问题。

always @(clk or clr);

begin

b=a;

c=b;

end

阻塞赋值就是顺序执行语句,类似于C语言结构化编程一样,语句是按顺序执行的,该语句的RTL如下图:

如果开始a=1,b=2,c=2;当上升沿到达后,a=1,b=1,c=1.

学习到的重点:

1)时序电路建模时,用非阻塞赋值;

2)锁存器电路建模时,用非阻塞赋值;

3)用always块建立组合逻辑模型时,用阻塞赋值;

4)在同一个always块中建立时序和组合逻辑电路时,用非阻塞赋值;

5)在同一个alway块中,不要即用非阻塞又用阻塞赋值;

6)不要在一个以上的always块中为同一个变量赋值;

7)用$strobe系统任务来显示用非阻塞赋值的变量值;

8)在赋值时不要使用#0延迟。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?