实用建模技术

前言

- 来了来了,Verilog语言的另外一些增强特性,这些特性使Verilog语言在建模和设计分析等方面具有更强大的灵活性。

过程连续赋值

- 过程赋值:将值赋给寄存器,值一直保存在寄存器中,直到另一个过程赋值将另外一个值存放在该寄存器中。

- 过程连续赋值:允许在有限时间段内将表达式的值连续地加(驱动)到寄存器或线网中。改写寄存器或线网上的现有值。

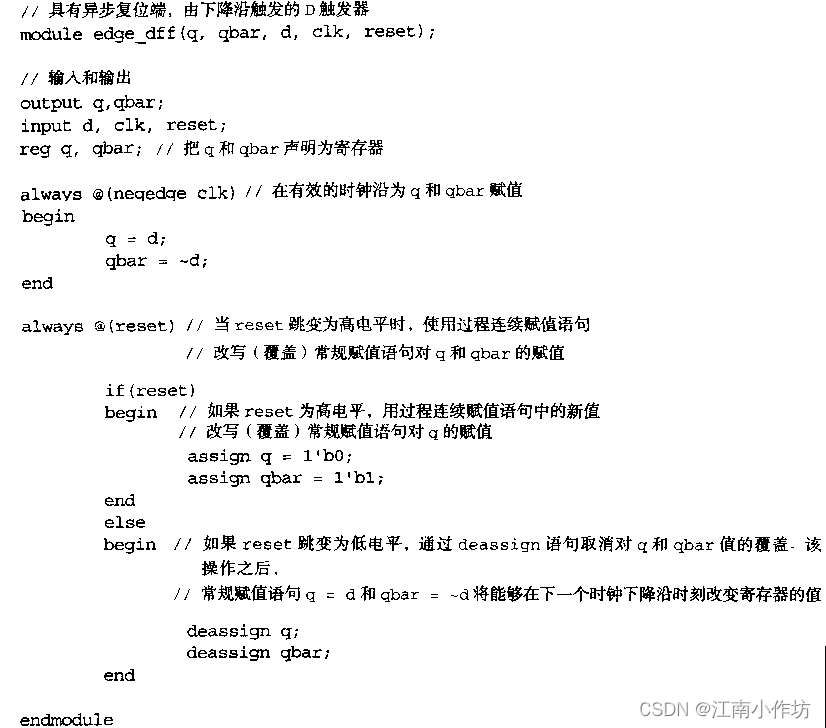

assign和deassign

- 关键字:

assign、deassign - 用来表示第一类过程连续赋值语句,不建议使用,了解一下。

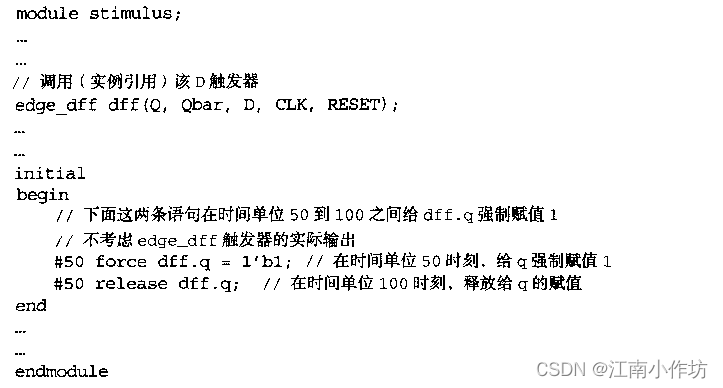

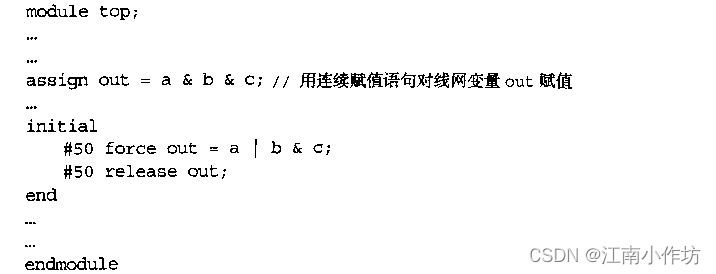

force和release

- 关键字:

force、release - 过程连续赋值语句的第二种形式,既可以用来改写(覆盖)寄存器上的赋值,也可以改写(覆盖)线网上的赋值。

- 典型应用:交互式调试过程中。

- 建议不要在设计模块内部使用,应当只出现在激励中,或仅作为调试语句。

作用在寄存器上

- 在一个受控时间段内改写q和qbar的值。

作用在线网上

- 线网被释放后,立即返回自己的正常驱动。线网可以被强制赋值为一个表达式或一个数值。

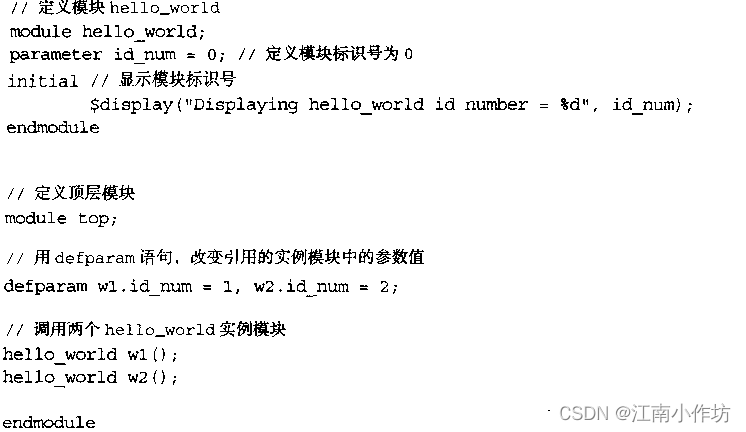

改写参数

- 又称覆盖参数。参数可以在模块定义内定义,但是在Verilog模块编译过程中,参数值可以针对每个模块调用单独改变。

- 两种方法:通过defparam语句、通过模块调用参数赋值。

defparam语句

- 关键字:

defparam - 可以在任意模块调用中改变参数值,模块调用的层次名称可以用在改写(覆盖)参数值的语句中。

- 一个模块中可以出现多个defparam语句。

- 可以用defparam语句覆盖任何参数。

- ok,又到了糟糕的环节,defparam语句被认为是糟糕的代码风格,建议在Verilog HDL代码中使用替代形式。了解一下即可。

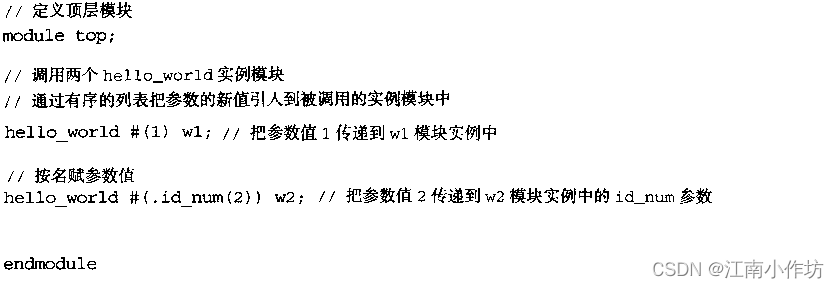

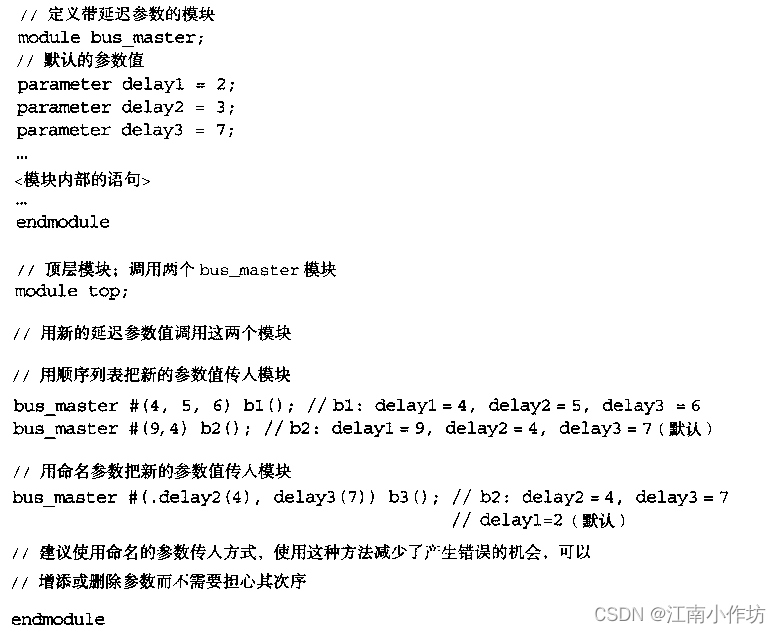

模块实例的参数值

- 在调用模块时可以改写(覆盖)其原来定义的参数值。

- 将上面例子做如下修改

- 参数按名称赋值

条件编译与执行

- 条件编译:Verilog代码的一部分可能使用于某个编译环境,但不适用另一个环境。设计者在代码中指定其中某一部分代码只有在设置了特定的标志后才能被编译。这就是条件编译。

- 条件执行:同理,在程序运行,设置了某个标志后才能执行Verilog设计的某些部分。

条件编译

- <

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?